搜索到

344

篇与

的结果

-

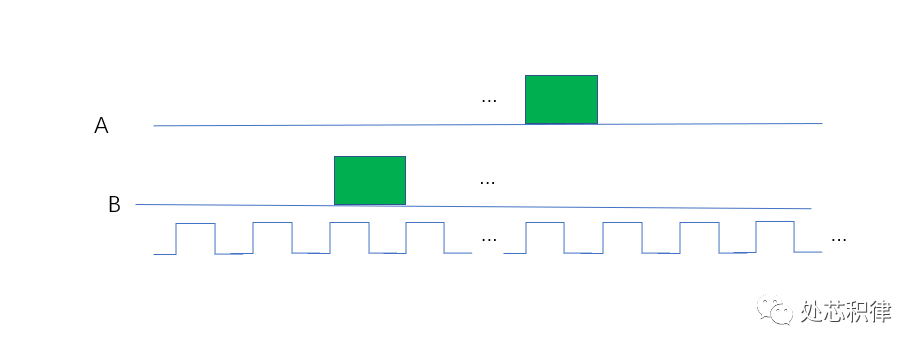

芯片验证随机(random)的六宗罪 IP与SoC设计2023年04月19日12:04江苏以前看到不少验证技术书籍都在说验证环境中随机怎么怎么好,然后为了随机,UVM,SV 提供了什么什么支持。但是最近的一些工作小编发现在验证中采用随机存在很多缺点。下面小编带大家看看使用随机带来的六宗罪。第一宗罪:难以debug出现fail的test,当debug完,对设计和验证环境做了改动,可能无法复现fail的场景。如何确保发现的testbench的问题,或者RTL的问题有真的修掉?一般的做法是用同样的seed,然后跑一遍之前的fail的test。但是有很多时候,由于环境的文件,约束等改变,再用同样的seed 跑fail 的test 和之前的行为不一致,从而错误的认为问题已经修掉。第二宗罪:难以覆盖到特定场景有些场景通过随机撞到的概率非常低。如下图所示,C = A &&B,在下图场景中想通过 随机到 (A==1)&&(B==1)的 场景,非常难。第三宗罪:验证时间不确定回归结果不可靠。一次通过率100%,不代表次次回归100%。一次回归可能100%,第二次回归又变成90%。连续10次回归100%,第十一次回归又出现fail的test。第四宗罪:重复测试用例很多浪费太多license 和服务器资源。因为单次regression不能保证没有问题,所以要周周跑,月月跑,一直跑到tapout,这浪费了很多license和服务器资源。特别是有些test 打到的场景重复,做一些无效验证,给公司资源造成极大浪费。第五宗罪:覆盖率收集耗费资源coverage 收敛比较耗时间和资源。由于随机约束造成不同场景出现的概率不一样,通过随机测试将代码覆盖率和功能覆盖率补全需要经过大量的回归测试。coverage的收敛速度没有直接测试来得快。下面是一个案例,在跑完一版regression后,功能覆盖率是80.49%。我们想将该功能覆盖率补全,采用直接测试用例,我们调用了5次测试,可以将覆盖率打到95.90% ,剩下的部分可以waive掉。当我们采用随机测试,调用了5次随机测试,覆盖率为90.62%。当我们采用随机测试,调用了10次随机测试,覆盖率为93.97%。当我们采用随机测试,调用了20次随机测试,覆盖率为95.90%,达到了和直接测试同样的效果。第六宗罪:场景打不全随机验证打不全所有场景如上图所示,随机的行为很难将所有的测试路径都打到。随机有没有好处呢?当然有,比如探索更多的场景:随机验证可以探索更多的测试场景,覆盖更多的状态空间。这可以帮助发现设计中的潜在问题和漏洞,从而提高验证的质量。发现意外错误:随机测试可以揭示一些设计者未曾考虑的异常情况,以及在正常测试中可能被忽略的边缘情况。这有助于找到并修复一些潜在的设计错误。减少人为偏见:手动创建测试用例可能受到验证工程师的认知偏见和经验限制的影响。随机验证方法可以降低这种偏见对验证结果的影响,从而提高验证的可靠性。减少人工编写测试用例的时间和精力:随机验证方法可以自动生成大量测试用例,从而减少人工编写测试用例的时间和精力。这有助于缩短验证周期,提高验证效率。更好地应对复杂性:随着芯片设计变得越来越复杂,人工创建足够多的测试用例以覆盖所有可能的场景变得越来越困难。随机验证方法可以在面对复杂设计时自动生成更多的测试用例,从而更好地应对这种复杂性。使用随机验证存在很多问题,但它仍然是一种非常有效的验证方法。为了克服这些缺点,我们可以将随机验证与其他验证方法(如指导性验证、形式验证等)相结合,以实现更全面、有效的芯片验证。来自微信

芯片验证随机(random)的六宗罪 IP与SoC设计2023年04月19日12:04江苏以前看到不少验证技术书籍都在说验证环境中随机怎么怎么好,然后为了随机,UVM,SV 提供了什么什么支持。但是最近的一些工作小编发现在验证中采用随机存在很多缺点。下面小编带大家看看使用随机带来的六宗罪。第一宗罪:难以debug出现fail的test,当debug完,对设计和验证环境做了改动,可能无法复现fail的场景。如何确保发现的testbench的问题,或者RTL的问题有真的修掉?一般的做法是用同样的seed,然后跑一遍之前的fail的test。但是有很多时候,由于环境的文件,约束等改变,再用同样的seed 跑fail 的test 和之前的行为不一致,从而错误的认为问题已经修掉。第二宗罪:难以覆盖到特定场景有些场景通过随机撞到的概率非常低。如下图所示,C = A &&B,在下图场景中想通过 随机到 (A==1)&&(B==1)的 场景,非常难。第三宗罪:验证时间不确定回归结果不可靠。一次通过率100%,不代表次次回归100%。一次回归可能100%,第二次回归又变成90%。连续10次回归100%,第十一次回归又出现fail的test。第四宗罪:重复测试用例很多浪费太多license 和服务器资源。因为单次regression不能保证没有问题,所以要周周跑,月月跑,一直跑到tapout,这浪费了很多license和服务器资源。特别是有些test 打到的场景重复,做一些无效验证,给公司资源造成极大浪费。第五宗罪:覆盖率收集耗费资源coverage 收敛比较耗时间和资源。由于随机约束造成不同场景出现的概率不一样,通过随机测试将代码覆盖率和功能覆盖率补全需要经过大量的回归测试。coverage的收敛速度没有直接测试来得快。下面是一个案例,在跑完一版regression后,功能覆盖率是80.49%。我们想将该功能覆盖率补全,采用直接测试用例,我们调用了5次测试,可以将覆盖率打到95.90% ,剩下的部分可以waive掉。当我们采用随机测试,调用了5次随机测试,覆盖率为90.62%。当我们采用随机测试,调用了10次随机测试,覆盖率为93.97%。当我们采用随机测试,调用了20次随机测试,覆盖率为95.90%,达到了和直接测试同样的效果。第六宗罪:场景打不全随机验证打不全所有场景如上图所示,随机的行为很难将所有的测试路径都打到。随机有没有好处呢?当然有,比如探索更多的场景:随机验证可以探索更多的测试场景,覆盖更多的状态空间。这可以帮助发现设计中的潜在问题和漏洞,从而提高验证的质量。发现意外错误:随机测试可以揭示一些设计者未曾考虑的异常情况,以及在正常测试中可能被忽略的边缘情况。这有助于找到并修复一些潜在的设计错误。减少人为偏见:手动创建测试用例可能受到验证工程师的认知偏见和经验限制的影响。随机验证方法可以降低这种偏见对验证结果的影响,从而提高验证的可靠性。减少人工编写测试用例的时间和精力:随机验证方法可以自动生成大量测试用例,从而减少人工编写测试用例的时间和精力。这有助于缩短验证周期,提高验证效率。更好地应对复杂性:随着芯片设计变得越来越复杂,人工创建足够多的测试用例以覆盖所有可能的场景变得越来越困难。随机验证方法可以在面对复杂设计时自动生成更多的测试用例,从而更好地应对这种复杂性。使用随机验证存在很多问题,但它仍然是一种非常有效的验证方法。为了克服这些缺点,我们可以将随机验证与其他验证方法(如指导性验证、形式验证等)相结合,以实现更全面、有效的芯片验证。来自微信 -

4个令人惊艳的ChatGPT项目,开源了! 1T服务圈儿2023年04月18日17:32江苏来源丨经授权转自 Jack Cui(ID:JackCui-AI)作者丨Jack Cui自从 ChatGPT、Stable Diffusion 发布以来,各种相关开源项目百花齐放,着实让人应接不暇。今天,我将着重挑选几个优质的开源项目,对我们的日常工作、学习生活,都会有很大的帮助。今天整理分享给大家,希望对你有所帮助。一、Visual ChatGPT这个是微软开源的项目,一周多的时间,就斩获了 23.6k+ star。简单概括它,那就是一个多模态的问答系统。支持AI绘画、语言问答、看图问答,将 AI 届近期的 3 大热点集于一身。效果展示:系统实现框架如下:Visual ChatGPT的系统实现框架这是一个“大力出奇迹”的开源项目,集多方研究成果于一身:BLIP、CLIP、ChatGPT、pix2pix、inpainting、vqa 等。说白了,就是教你怎样使用这些项目,搭建一个多模态的问答系统,这个系统架构很有参考价值。项目地址:https://github.com/microsoft/visual-chatgpt二、SadTalker这是一篇 2023 年的 CVPR 论文对应的开源项目。刚刚开源,新鲜热乎~功能就是:根据一张图片、一段音频,合成面部说这段语音的视频。结合 ChatGPT、AIGC、音频文字转换,虚拟二次元 or 三次元形象,就能“活”过来了。此外,还项目还做成了 stable diffusion webui 的插件,也就是直接能在 stable diffusion 里使用。生成的图片,直接配合一段音频,就能生成合成的视频。项目地址:https://github.com/winfredy/sadtalker三、FateZero文本能编辑生成图片?那视频能编辑吗?FateZero:我可以!左图是原图,右图是生成效果,输入的文本是:增加 Pokémon 动漫风格除了视频的风格迁移,也支持修改里面的内容。比如:松鼠是胡萝卜,变成,兔子吃茄子。这个项目也是基于sd做的,离一键生成视频,又进了一步。项目地址:https://github.com/chenyangqiqi/fatezero四、ChatPaperarXiv 想必大家都知道,当下最流行的论文托管网站,上面有来自世界各地的科学家、研究学者。为了提高 arXiv 用户阅读论文的效率,有人开源了一款利用 ChatGPT 总结 arXiv 论文的开源工具 ChatPaper。简而言之,该项目可根据用户关键词下载 arXiv 上的最新论文,利用 ChatGPT3.5 API 强大的归纳能力,将其浓缩成固定格式,文字少且易读。同时,项目支持个人自己部署,或者直接去 Hugge Face 体验。项目地址:https://github.com/kaixindelele/ChatPaperhttps://huggingface.co/spaces/wangrongsheng/ChatPaper来自微信

4个令人惊艳的ChatGPT项目,开源了! 1T服务圈儿2023年04月18日17:32江苏来源丨经授权转自 Jack Cui(ID:JackCui-AI)作者丨Jack Cui自从 ChatGPT、Stable Diffusion 发布以来,各种相关开源项目百花齐放,着实让人应接不暇。今天,我将着重挑选几个优质的开源项目,对我们的日常工作、学习生活,都会有很大的帮助。今天整理分享给大家,希望对你有所帮助。一、Visual ChatGPT这个是微软开源的项目,一周多的时间,就斩获了 23.6k+ star。简单概括它,那就是一个多模态的问答系统。支持AI绘画、语言问答、看图问答,将 AI 届近期的 3 大热点集于一身。效果展示:系统实现框架如下:Visual ChatGPT的系统实现框架这是一个“大力出奇迹”的开源项目,集多方研究成果于一身:BLIP、CLIP、ChatGPT、pix2pix、inpainting、vqa 等。说白了,就是教你怎样使用这些项目,搭建一个多模态的问答系统,这个系统架构很有参考价值。项目地址:https://github.com/microsoft/visual-chatgpt二、SadTalker这是一篇 2023 年的 CVPR 论文对应的开源项目。刚刚开源,新鲜热乎~功能就是:根据一张图片、一段音频,合成面部说这段语音的视频。结合 ChatGPT、AIGC、音频文字转换,虚拟二次元 or 三次元形象,就能“活”过来了。此外,还项目还做成了 stable diffusion webui 的插件,也就是直接能在 stable diffusion 里使用。生成的图片,直接配合一段音频,就能生成合成的视频。项目地址:https://github.com/winfredy/sadtalker三、FateZero文本能编辑生成图片?那视频能编辑吗?FateZero:我可以!左图是原图,右图是生成效果,输入的文本是:增加 Pokémon 动漫风格除了视频的风格迁移,也支持修改里面的内容。比如:松鼠是胡萝卜,变成,兔子吃茄子。这个项目也是基于sd做的,离一键生成视频,又进了一步。项目地址:https://github.com/chenyangqiqi/fatezero四、ChatPaperarXiv 想必大家都知道,当下最流行的论文托管网站,上面有来自世界各地的科学家、研究学者。为了提高 arXiv 用户阅读论文的效率,有人开源了一款利用 ChatGPT 总结 arXiv 论文的开源工具 ChatPaper。简而言之,该项目可根据用户关键词下载 arXiv 上的最新论文,利用 ChatGPT3.5 API 强大的归纳能力,将其浓缩成固定格式,文字少且易读。同时,项目支持个人自己部署,或者直接去 Hugge Face 体验。项目地址:https://github.com/kaixindelele/ChatPaperhttps://huggingface.co/spaces/wangrongsheng/ChatPaper来自微信 -

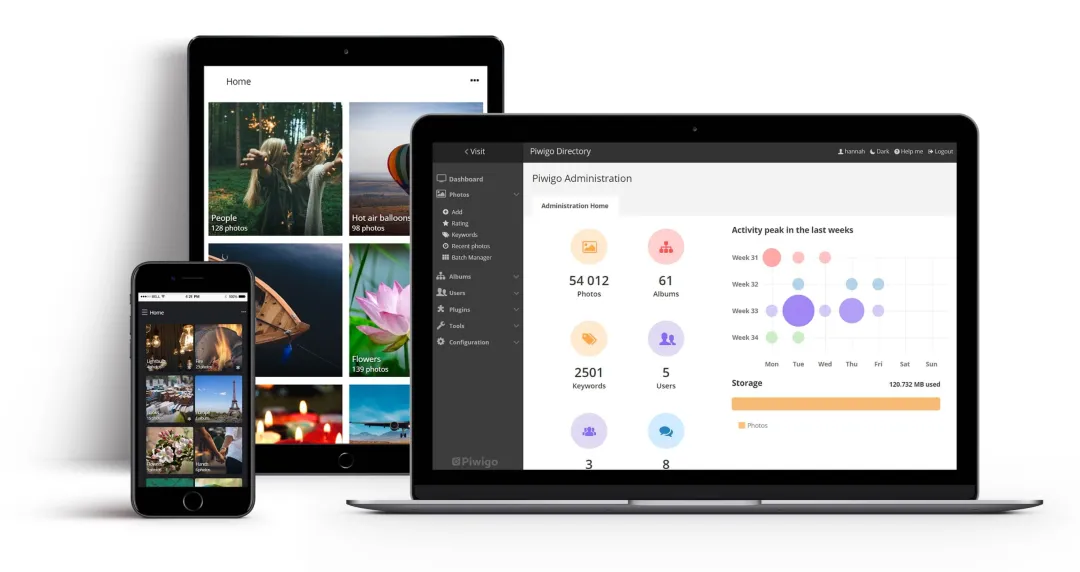

推荐5款Github上有趣的PHP项目 原创php中文网php中文网课程2022年11月16日17:00安徽1.Piwigo(一款开源在线相册应用)项目地址:https://github.com/Piwigo/Piwigo采用 PHP+MySQL 开发的管理照片的 Web 项目,它功能强大安装简单,拥有丰富的主题和灵活的插件,可轻松完成个性化定制。支持 iOS 和 Android 客户端,让你可以随时随地上传、管理照片。2.SyncMusic(在线弹幕点歌台)项目地址:https://github.com/kasuganosoras/SyncMusic基于 PHP Swoole 开发的在线弹幕点歌台。支持自由点歌、切歌、调整排序、删除指定音乐以及基础权限分级3.freenom(免费域名自动续期工具)项目地址:https://github.com/luolongfei/freenom因为顶级免费域名供应商 Freenom,提供的免费域名需要每年续期,该项目可以自动完成域名续期,让你轻松拥有免费的顶级域名。4.dootask(在线项目管理平台)项目地址:https://github.com/kuaifan/dootask功能包括任务分配、文档协作、即时 IM、文档协作、文件管理等5.server(开源云存储平台)项目地址:https://github.com/nextcloud/server开源云存储平台,功能齐全,可以用于搭建公司内部的云存储平台来自微信

推荐5款Github上有趣的PHP项目 原创php中文网php中文网课程2022年11月16日17:00安徽1.Piwigo(一款开源在线相册应用)项目地址:https://github.com/Piwigo/Piwigo采用 PHP+MySQL 开发的管理照片的 Web 项目,它功能强大安装简单,拥有丰富的主题和灵活的插件,可轻松完成个性化定制。支持 iOS 和 Android 客户端,让你可以随时随地上传、管理照片。2.SyncMusic(在线弹幕点歌台)项目地址:https://github.com/kasuganosoras/SyncMusic基于 PHP Swoole 开发的在线弹幕点歌台。支持自由点歌、切歌、调整排序、删除指定音乐以及基础权限分级3.freenom(免费域名自动续期工具)项目地址:https://github.com/luolongfei/freenom因为顶级免费域名供应商 Freenom,提供的免费域名需要每年续期,该项目可以自动完成域名续期,让你轻松拥有免费的顶级域名。4.dootask(在线项目管理平台)项目地址:https://github.com/kuaifan/dootask功能包括任务分配、文档协作、即时 IM、文档协作、文件管理等5.server(开源云存储平台)项目地址:https://github.com/nextcloud/server开源云存储平台,功能齐全,可以用于搭建公司内部的云存储平台来自微信 -

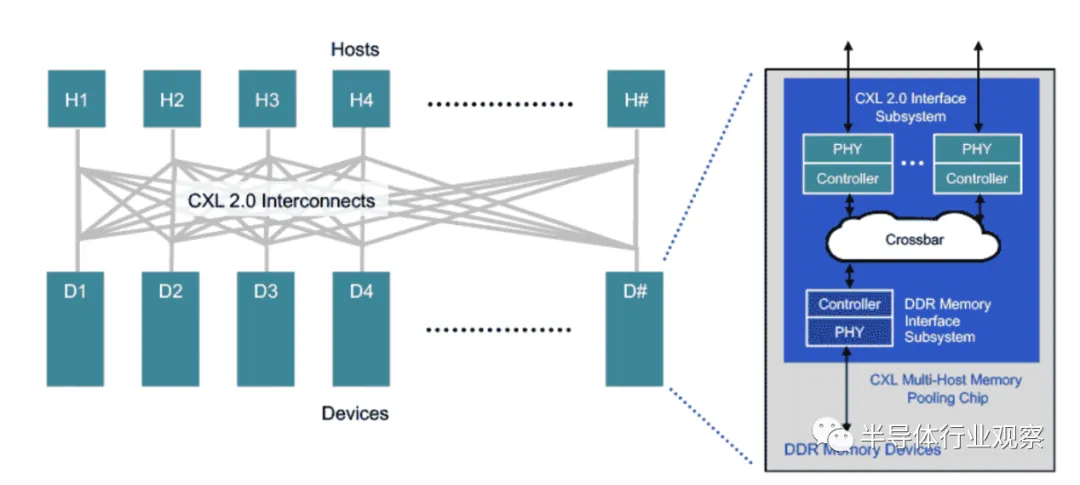

关于CXL,你想知道的都在这里 半导体行业观察2023年03月08日09:59安徽指数级的数据增长促使计算行业开始进行突破性的架构转变,以从根本上改变数据中心的性能、效率和成本。为了继续提高性能,服务器正越来越多地转向异构计算架构,使用专门构建的加速器从 CPU 卸载专门的工作负载。CXL 的内存缓存一致性允许在 CPU 和加速器之间共享内存资源。此外,CXL 支持部署新的内存层,可以弥合主内存和 SSD 存储之间的延迟差距。这些新的内存层将增加带宽、容量、提高效率并降低总体拥有成本 (TCO)。凭借这些诸多优势,业界果断地将 CXL 融合为处理器、内存和加速器的高速缓存一致性互连。CXL通过一个叫做CXL 联盟的开放行业标准组织开发技术规范,促进新兴使用模型的性能突破,同时支持数据中心加速器和其他高速增强功能的开放生态系统。CXL简介:什么是 Compute Express Link?CXL是一个开放标准的行业支持的缓存一致性互连,用于处理器、内存扩展和加速器。从本质上讲,CXL 技术在 CPU 内存空间和连接设备上的内存之间保持内存一致性。这支持资源共享(或池化)以获得更高的性能,降低软件堆栈的复杂性,并降低整体系统成本。CXL 联盟已经确定了将采用新互连的三类主要设备:类型1设备:智能 NIC 等加速器通常缺少本地内存。通过 CXL,这些设备可以与主机处理器的 DDR 内存进行通信。类型2设备:GPU、ASIC 和 FPGA 都配备了 DDR 或 HBM 内存,并且可以使用 CXL 使主机处理器的内存在本地可供加速器使用,并使加速器的内存在本地可供 CPU 使用。它们还共同位于同一个缓存一致域中,有助于提升异构工作负载。类型 3 设备:内存设备可以通过 CXL 连接,为主机处理器提供额外的带宽和容量。内存的类型独立于主机的主内存。CXL 协议和标准CXL 标准通过三种协议支持各种用例:CXL.io、CXL.cache 和 CXL.memory。CXL.io:该协议在功能上等同于 PCIe 协议,并利用了 PCIe 的广泛行业采用和熟悉度。作为基础通信协议,CXL.io 用途广泛,适用于广泛的用例。CXL.cache:该协议专为更具体的应用程序而设计,使加速器能够有效地访问和缓存主机内存以优化性能。CXL.memory:该协议使主机(例如处理器)能够使用加载/存储命令访问设备连接的内存。这三个协议共同促进了计算设备(例如 CPU 主机和 AI 加速器)之间内存资源的一致共享。从本质上讲,这通过共享内存实现通信简化了编程。用于设备和主机互连的协议如下:类型 1 设备:CXL.io + CXL.cache类型2设备:CXL.io + CXL.cache + CXL.memory类型 3 设备:CXL.io + CXL.memoryCompute Express Link 与 PCIe:这两者有什么关系?CXL 建立在PCIe的物理和电气接口之上,其协议建立了一致性、简化了软件堆栈并保持与现有标准的兼容性。具体来说,CXL 利用 PCIe 5 功能,允许备用协议使用物理 PCIe 层。当支持 CXL 的加速器插入 x16 插槽时,设备会以每秒 2.5 千兆传输 (GT/s) 的默认 PCI Express 1.0 传输速率与主机处理器的端口进行协商。只有双方都支持 CXL,CXL 交易协议才会被激活。否则,它们作为 PCIe 设备运行。CXL 1.1 和 2.0 使用 PCIe 5.0 物理层,允许通过 16 通道链路在每个方向上以 32 GT/s 或高达 64 GB/s 的速度传输数据。CXL 3.0 使用 PCIe 6.0 物理层将数据传输扩展到 64 GT/s,支持通过 x16 链路进行高达 128 GB/s 的双向通信。CXL 2.0 和 3.0 有什么新功能?首先在内存池方面,CXL 2.0 支持切换以启用内存池。使用 CXL 2.0 交换机,主机可以访问池中的一个或多个设备。尽管主机必须支持 CXL 2.0 才能利用此功能,但内存设备可以是支持 CXL 1.0、1.1 和 2.0 的硬件的组合。在 1.0/1.1 中,设备被限制为一次只能由一台主机访问的单个逻辑设备。然而,一个 2.0 级别的设备可以被划分为多个逻辑设备,允许多达 16 台主机同时访问内存的不同部分。例如,主机 1 (H1) 可以使用设备 1 (D1) 中一半的内存和设备 2 (D2) 中四分之一的内存,以将其工作负载的内存需求与内存池中的可用容量完美匹配. 设备 D1 和 D2 中的剩余容量可由一台或多台其他主机使用,最多可达 16 台。设备 D3 和 D4 分别启用了 CXL 1.0 和 1.1,一次只能由一台主机使用。CXL 3.0 引入了对等直接内存访问和对内存池的增强,其中多个主机可以一致地共享 CXL 3.0 设备上的内存空间。这些功能支持新的使用模型并提高数据中心架构的灵活性。其次来到交换方面;通过转向 CXL 2.0 直连架构,数据中心可以获得主内存扩展的性能优势,以及池内存的效率和总体拥有成本 (TCO) 优势。假设所有主机和设备都支持 CXL 2.0,则“切换”通过 CXL 内存池芯片中的交叉开关集成到内存设备中。这可以保持较低的延迟,但需要更强大的芯片,因为它现在负责交换机执行的控制平面功能。通过低延迟直接连接,连接的内存设备可以使用 DDR DRAM 来扩展主机主内存。这可以在非常灵活的基础上完成,因为主机能够访问处理特定工作负载所需的尽可能多的设备的全部或部分容量。CXL 3.0 引入了多层交换,支持交换结构的实施。CXL 2.0 支持单层交换。借助 CXL 3.0,启用了交换结构,其中交换机可以连接到其他交换机,从而大大增加了扩展的可能性。第三,“按需”内存范例;类似于拼车,CXL 2.0 和 3.0 在“按需”的基础上为主机分配内存,从而提供更高的内存利用率和效率。该架构提供了为标称工作负载(而不是最坏情况)配置服务器主内存的选项,能够在需要时访问池以处理高容量工作负载,并为 TCO 带来更多好处。最终,CXL 内存池模型可以支持向服务器分解和可组合性的根本转变。在此范例中,可以按需组合离散的计算、内存和存储单元,以有效地满足任何工作负载的需求。第四,完整性和数据加密 (IDE);分解——或分离服务器架构的组件——增加了攻击面。这正是 CXL 包含安全设计方法的原因。具体来说,所有三个 CXL 协议都通过完整性和数据加密 (IDE) 来保护,IDE 提供机密性、完整性和重放保护。IDE 在 CXL 主机和设备芯片中实例化的硬件级安全协议引擎中实现,以满足 CXL 的高速数据速率要求,而不会引入额外的延迟。应该注意的是,CXL 芯片和系统本身需要防止篡改和网络攻击的保护措施。在 CXL 芯片中实现的硬件信任根可以为安全启动和安全固件下载的安全和支持要求提供此基础。第五,将信令扩展到 64 GT/s;CXL 3.0 带来了标准数据速率的阶跃函数增加。如前所述,CXL 1.1 和 2.0 在其物理层使用 PCIe 5.0 电气:32 GT/s 的 NRZ 信号。CXL 3.0 秉承了以广泛采用的 PCIe 技术为基础构建的相同理念,并将其扩展到 2022 年初发布的最新 6.0 版 PCIe 标准。使用 PAM4 信号将 CXL 3.0 数据速率提高到 64 GT/s。我们涵盖了 PCIe 6 中 PAM4 信令的详细信息——您需要知道的一切。得益于CXL的出现,开发者可以简化和改进低延迟连接和内存一致性,显著提高计算性能和效率,同时降低 TCO。此外,CXL 内存扩展功能可在当今服务器中的直接连接 DIMM 插槽之上实现额外的容量和带宽。CXL 使得通过 CXL 连接设备向 CPU 主机处理器添加更多内存成为可能。当与持久内存配对时,低延迟 CXL 链路允许 CPU 主机将此额外内存与 DRAM 内存结合使用。大容量工作负载的性能取决于大内存容量,例如 AI。考虑到这些是大多数企业和数据中心运营商正在投资的工作负载类型,CXL 的优势显而易见。来自微信

关于CXL,你想知道的都在这里 半导体行业观察2023年03月08日09:59安徽指数级的数据增长促使计算行业开始进行突破性的架构转变,以从根本上改变数据中心的性能、效率和成本。为了继续提高性能,服务器正越来越多地转向异构计算架构,使用专门构建的加速器从 CPU 卸载专门的工作负载。CXL 的内存缓存一致性允许在 CPU 和加速器之间共享内存资源。此外,CXL 支持部署新的内存层,可以弥合主内存和 SSD 存储之间的延迟差距。这些新的内存层将增加带宽、容量、提高效率并降低总体拥有成本 (TCO)。凭借这些诸多优势,业界果断地将 CXL 融合为处理器、内存和加速器的高速缓存一致性互连。CXL通过一个叫做CXL 联盟的开放行业标准组织开发技术规范,促进新兴使用模型的性能突破,同时支持数据中心加速器和其他高速增强功能的开放生态系统。CXL简介:什么是 Compute Express Link?CXL是一个开放标准的行业支持的缓存一致性互连,用于处理器、内存扩展和加速器。从本质上讲,CXL 技术在 CPU 内存空间和连接设备上的内存之间保持内存一致性。这支持资源共享(或池化)以获得更高的性能,降低软件堆栈的复杂性,并降低整体系统成本。CXL 联盟已经确定了将采用新互连的三类主要设备:类型1设备:智能 NIC 等加速器通常缺少本地内存。通过 CXL,这些设备可以与主机处理器的 DDR 内存进行通信。类型2设备:GPU、ASIC 和 FPGA 都配备了 DDR 或 HBM 内存,并且可以使用 CXL 使主机处理器的内存在本地可供加速器使用,并使加速器的内存在本地可供 CPU 使用。它们还共同位于同一个缓存一致域中,有助于提升异构工作负载。类型 3 设备:内存设备可以通过 CXL 连接,为主机处理器提供额外的带宽和容量。内存的类型独立于主机的主内存。CXL 协议和标准CXL 标准通过三种协议支持各种用例:CXL.io、CXL.cache 和 CXL.memory。CXL.io:该协议在功能上等同于 PCIe 协议,并利用了 PCIe 的广泛行业采用和熟悉度。作为基础通信协议,CXL.io 用途广泛,适用于广泛的用例。CXL.cache:该协议专为更具体的应用程序而设计,使加速器能够有效地访问和缓存主机内存以优化性能。CXL.memory:该协议使主机(例如处理器)能够使用加载/存储命令访问设备连接的内存。这三个协议共同促进了计算设备(例如 CPU 主机和 AI 加速器)之间内存资源的一致共享。从本质上讲,这通过共享内存实现通信简化了编程。用于设备和主机互连的协议如下:类型 1 设备:CXL.io + CXL.cache类型2设备:CXL.io + CXL.cache + CXL.memory类型 3 设备:CXL.io + CXL.memoryCompute Express Link 与 PCIe:这两者有什么关系?CXL 建立在PCIe的物理和电气接口之上,其协议建立了一致性、简化了软件堆栈并保持与现有标准的兼容性。具体来说,CXL 利用 PCIe 5 功能,允许备用协议使用物理 PCIe 层。当支持 CXL 的加速器插入 x16 插槽时,设备会以每秒 2.5 千兆传输 (GT/s) 的默认 PCI Express 1.0 传输速率与主机处理器的端口进行协商。只有双方都支持 CXL,CXL 交易协议才会被激活。否则,它们作为 PCIe 设备运行。CXL 1.1 和 2.0 使用 PCIe 5.0 物理层,允许通过 16 通道链路在每个方向上以 32 GT/s 或高达 64 GB/s 的速度传输数据。CXL 3.0 使用 PCIe 6.0 物理层将数据传输扩展到 64 GT/s,支持通过 x16 链路进行高达 128 GB/s 的双向通信。CXL 2.0 和 3.0 有什么新功能?首先在内存池方面,CXL 2.0 支持切换以启用内存池。使用 CXL 2.0 交换机,主机可以访问池中的一个或多个设备。尽管主机必须支持 CXL 2.0 才能利用此功能,但内存设备可以是支持 CXL 1.0、1.1 和 2.0 的硬件的组合。在 1.0/1.1 中,设备被限制为一次只能由一台主机访问的单个逻辑设备。然而,一个 2.0 级别的设备可以被划分为多个逻辑设备,允许多达 16 台主机同时访问内存的不同部分。例如,主机 1 (H1) 可以使用设备 1 (D1) 中一半的内存和设备 2 (D2) 中四分之一的内存,以将其工作负载的内存需求与内存池中的可用容量完美匹配. 设备 D1 和 D2 中的剩余容量可由一台或多台其他主机使用,最多可达 16 台。设备 D3 和 D4 分别启用了 CXL 1.0 和 1.1,一次只能由一台主机使用。CXL 3.0 引入了对等直接内存访问和对内存池的增强,其中多个主机可以一致地共享 CXL 3.0 设备上的内存空间。这些功能支持新的使用模型并提高数据中心架构的灵活性。其次来到交换方面;通过转向 CXL 2.0 直连架构,数据中心可以获得主内存扩展的性能优势,以及池内存的效率和总体拥有成本 (TCO) 优势。假设所有主机和设备都支持 CXL 2.0,则“切换”通过 CXL 内存池芯片中的交叉开关集成到内存设备中。这可以保持较低的延迟,但需要更强大的芯片,因为它现在负责交换机执行的控制平面功能。通过低延迟直接连接,连接的内存设备可以使用 DDR DRAM 来扩展主机主内存。这可以在非常灵活的基础上完成,因为主机能够访问处理特定工作负载所需的尽可能多的设备的全部或部分容量。CXL 3.0 引入了多层交换,支持交换结构的实施。CXL 2.0 支持单层交换。借助 CXL 3.0,启用了交换结构,其中交换机可以连接到其他交换机,从而大大增加了扩展的可能性。第三,“按需”内存范例;类似于拼车,CXL 2.0 和 3.0 在“按需”的基础上为主机分配内存,从而提供更高的内存利用率和效率。该架构提供了为标称工作负载(而不是最坏情况)配置服务器主内存的选项,能够在需要时访问池以处理高容量工作负载,并为 TCO 带来更多好处。最终,CXL 内存池模型可以支持向服务器分解和可组合性的根本转变。在此范例中,可以按需组合离散的计算、内存和存储单元,以有效地满足任何工作负载的需求。第四,完整性和数据加密 (IDE);分解——或分离服务器架构的组件——增加了攻击面。这正是 CXL 包含安全设计方法的原因。具体来说,所有三个 CXL 协议都通过完整性和数据加密 (IDE) 来保护,IDE 提供机密性、完整性和重放保护。IDE 在 CXL 主机和设备芯片中实例化的硬件级安全协议引擎中实现,以满足 CXL 的高速数据速率要求,而不会引入额外的延迟。应该注意的是,CXL 芯片和系统本身需要防止篡改和网络攻击的保护措施。在 CXL 芯片中实现的硬件信任根可以为安全启动和安全固件下载的安全和支持要求提供此基础。第五,将信令扩展到 64 GT/s;CXL 3.0 带来了标准数据速率的阶跃函数增加。如前所述,CXL 1.1 和 2.0 在其物理层使用 PCIe 5.0 电气:32 GT/s 的 NRZ 信号。CXL 3.0 秉承了以广泛采用的 PCIe 技术为基础构建的相同理念,并将其扩展到 2022 年初发布的最新 6.0 版 PCIe 标准。使用 PAM4 信号将 CXL 3.0 数据速率提高到 64 GT/s。我们涵盖了 PCIe 6 中 PAM4 信令的详细信息——您需要知道的一切。得益于CXL的出现,开发者可以简化和改进低延迟连接和内存一致性,显著提高计算性能和效率,同时降低 TCO。此外,CXL 内存扩展功能可在当今服务器中的直接连接 DIMM 插槽之上实现额外的容量和带宽。CXL 使得通过 CXL 连接设备向 CPU 主机处理器添加更多内存成为可能。当与持久内存配对时,低延迟 CXL 链路允许 CPU 主机将此额外内存与 DRAM 内存结合使用。大容量工作负载的性能取决于大内存容量,例如 AI。考虑到这些是大多数企业和数据中心运营商正在投资的工作负载类型,CXL 的优势显而易见。来自微信 -