搜索到

344

篇与

的结果

-

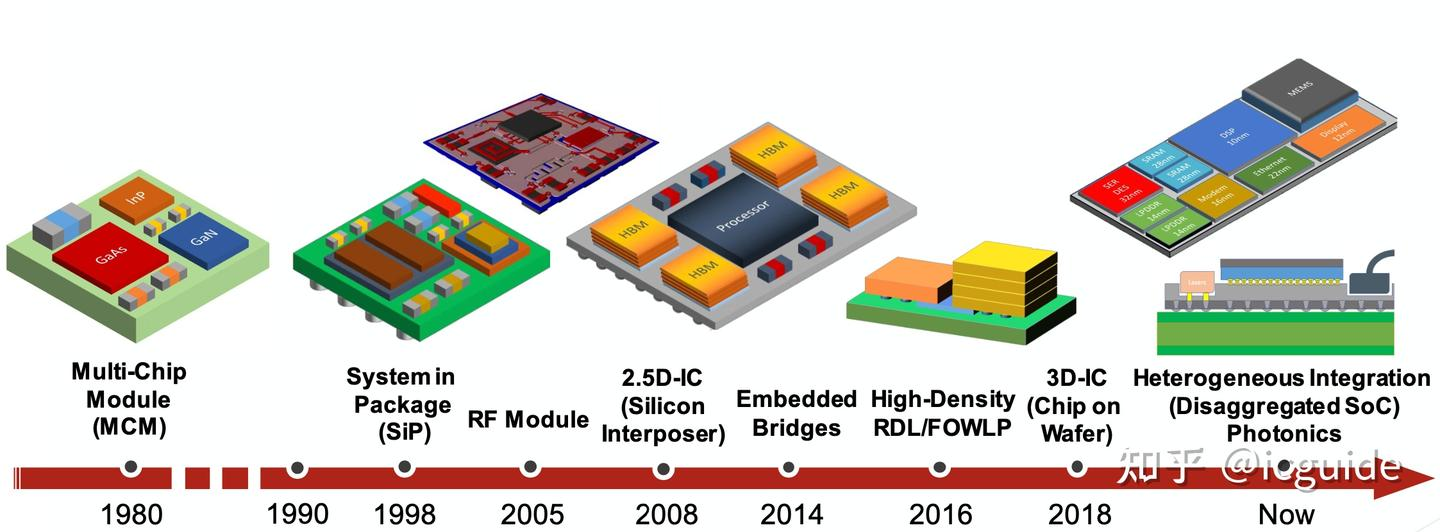

芯片封装简史 为什么封装现在很重要封装曾经是半导体制造过程中的事后想法,不被大家重视。当你创造了这一小块神奇的硅片之后,然后把他用某种方法封装起来,同时引出管脚,一颗芯片就诞生了。但是随着摩尔定律的延伸,工程师们意识到,他们可以利用对芯片的所有部分,包括封装在内进行优化和创新,来制造出最好的产品。更令人惊讶的是,过去没有一家封装公司被认为像传统的前端制造工艺那样重要。封装供应链通常被认为是"后端",并被视为成本中心,类似于银行业的前台和后台。但现在,随着前端难以更好的缩小芯片尺寸,一个全新的关注领域已经出现,这就是对先进封装的重视。接下来我们讨论一下封装的发展简史,从简单的DIP封装一直到先进的2.5D或3D封装。封装发展简介这是我从这个精彩的视频座中发现的封装技术的简要层次结构。如果你有一些时间,可以看一下。(视频发表于2012年,但是当时已经提到了现在最新的3D封装技术,所以并不过时) 芯片封装简史@eetop@创芯大讲堂 #封装#芯片#3D封装封装介绍 封装技术一个简化的演变过程是:DIP>QFP>BGA>POP/SiP>WLP 显然,有很多不同的封装技术,但我们要讨论的是大致能代表每种类型的简单技术,然后慢慢将其带到现在。我也非常喜欢下图这个高层次的概述(不过它已经过时了,但仍然正确)。在封装的最初阶段,裸片通常采用陶瓷或金属罐封(气密),以实现最大的可靠性。这主要适用于航空航天和军事应用,这些功能需要最高水平的可靠性。然而,对于我们的大多数日常用例来说,这并不是真正可行的,所以我们开始使用塑料封装和双列直插封装(DIP)。DIP封装(1964-1980年代)最早的DIP包装元件是由仙童半导体司的Bryant Buck Rogers在1964年时发明,在表面贴装技术问世之前的十年里,它被广泛应用。DIP在实际的裸片周围使用塑料封装外壳(编辑注:实际上陶瓷封装的军品芯片也大批采用了DIP封装),并有两排平行的突出的引脚,称为引线框架,与下面的PCB(印刷电路板)相连。实际的芯片通过键合线连接到两个引线框架,两个引线框架可以连接到印刷电路板(PCB)。DIP封装以复古的方式具有标志性,设计选择是可以理解的。实际的裸片将完全密封在树脂中,因此它带来了高可靠性和低成本,并且许多首批标志性的半导体都是以这种方式封装的。请注意,芯片通过导线连接到外部引线框架,这使其成为一种"引线键合"封装方法。稍后将对此进行详细介绍。下面是英特尔8008--实际上是第一批现代微处理器之一。注意它的标志性DIP封装。因此,如果你看到那些看起来像小蜘蛛的半导体的时髦照片,这只是一个DIP封装类的半导体。英特尔的原始微处理器,8008 家族然后,这些小金插针中的每一个都被焊接到PCB上,在那里它与其他电气元件和系统的其余部分接触。以下是封装如何焊接到PCB板上。PCB本身通常是由铜或其他电气元件由非导电材料层压而成。然后,PCB板可以将电信号从一个地方输送到另一个地方,并让个元件相互连接和通信。虽然DIP还有其他演绎版,但实际上是时候转向始于20世纪80年代的下一个封装技术范式或表面贴装封装了。表面贴装封装(1980-1990年代)下一步的变化不是通过DIP安装产品,而是引入表面贴装技术(SMT)。正如所暗示的那样,封装直接安装在PCB的表面上,并允许在一块基板上使用更多的元件并降低成本。下图是典型的表面贴装封装。这种封装有许多变体,在半导体创新的鼎盛时期,这一直是很长一段时间的主力。值得注意的是,大部分芯片都是4个侧面都有引脚。这遵循了封装的一般愿望,即占用更少的空间并增加连接带宽或I / O。每一项额外的进步都会考虑到这一点,并且是一种值得关注的模式。这个过程曾经是手动的,但现在是高度自动化的。此外,这实际上为PCB创造了相当多的问题,如popcorning。封装爆裂是指在焊接过程中,塑料封装内的水分被加热,由于快速加热和冷却,水分在PCB上造成问题。另一件需要注意的事情是,随着封装工艺的每一次提升,复杂性和故障也会随之增加球栅封装和芯片级封装(1990年代至2000年代)随着对半导体速度的需求不断提高,对更好封装的需求也在不断增加。虽然出现了QFN(四方扁平无引线)和其他表面贴装技术,但我想向你介绍一种我们在未来必须了解的封装设计的开端,这就是广泛使用的球栅阵列(BGA)封装的开始。这些焊球或凸起被称为焊料凸起/球这就是球栅阵列的外观,可以从下面直接将一块硅片安装到PCB或基板上,而不是像以前的表面贴装技术那样简单地将所有4端的角落贴上胶带。因此,这只是我上面列出的趋势的另一个延续,占用更少的空间,有更多的连接。现在,我们不再是用电线细细地连接每一侧的封装,而是直接将一个封装连接到另一个。这导致了密度的增加,更好的I/O性能,以及现在增加的复杂性,即你如何检查BGA封装是否工作。在这之前,封装主要是通过视觉检查和测试。现在我们无法看到封装,所以没有办法进行测试。我们可以X射线进行检查,以及更复杂的技术。现代封装(2000-2010年代)我们现在走进了现代封装的时代。上面描述的许多封装方案今天仍在使用,但是,您将开始看到越来越多的封装类型,并且这些封装类型将来会变得更加相关。公平地说,许多这些即将到来的技术是在过去几十年中发明的,但由于成本原因,直到后来才被广泛使用。倒装芯片这是你可能会读到或听到的最常见的封装之一。我很高兴能为你定义它,因为到目前为止,我读过的入门书中还没有一个令人满意的解释。倒装芯片是IBM很早就发明的,通常会被缩写为C4。就倒装芯片而言,它确实不是一种独立的封装形式,而是一种封装风格。它几乎就是只要在芯片上有一个焊接凸点就可以了。芯片不是用线粘合互连,而是翻转过来面对另一个芯片,中间有一个连接基板,所以叫 "倒装芯片"。从维基百科上的解释内容可以更好的理解什么是倒装芯片:在晶圆上创建集成电路芯片表面的焊盘被金属化每个焊盘上都沉积一个焊点芯片被切割芯片被翻转和定位,以便焊球面向电路然后将焊球重新熔化安装好的芯片用电绝缘胶进行底部填充引线键合请注意倒装芯片与引线键合有何不同。上面介绍的DIP封装这就是引线键合,其中芯片使用导线键合到另一种金属上,然后焊接到PCB上。引线键合不是一种特定的技术,而是一套较旧的技术,涵盖了许多不同类型的封装。引线键合是倒装芯片的前身。先进封装(2010年代至今)我们一直在缓慢地进入"先进封装"半导体时代,我现在想谈谈一些更高级的概念。实际上,有各种层次的"封装"适合这个思维过程。我们之前讲过的大多数封装,都集中在芯片封装到PCB上,但先进封装的开始其实是从手机开始的。手机在很多方面都是先进封装诸多方面的巨大前奏。这是有道理的!对于手机需要在尽可能小的空间内集成大量的芯片,比笔记本电脑或台式电脑密度大得多。所有东西都必须被动冷却,当然也要尽可能薄。这将封装推向了新的极限。我们讨论的许多概念都是从智能手机封装开始的,现在已经将自己推向了半导体行业的其他部分。芯片级封装(CSP)芯片级封装实际上比听起来要宽一些,最初意味着芯片大小的封装。技术定义是封装尺寸不超过芯片本身的1.2倍,并且必须是单芯片且可连接的。实际上,我已经向您介绍了CSP的概念,那就是通过倒装芯片。但CSP确实通过智能手机提升到了一个新的水平。这张照片中的所有东西都是芯片芯片的1.2倍大小,并且专注于节省尽可能多的空间。CSP时代有很多不同的风格,包括倒装芯片、右基板和其他技术,都属于这一类。晶圆级封装(WLP)但还有一个更小的级别--这就是 "终极 "芯片规模的封装尺寸,或在晶圆级封装。这几乎就是把封装放在实际的硅片本身。封装的就是硅片。它更薄,具有最高水平的I/O,而且显然会非常热,很难制造。先进的封装革命目前是在CSP的规模上,但未来将集中在晶圆上。这是一个有趣的演变,封装被实际的硅本身所包含。芯片是封装,反之亦然。与仅仅将一些球焊接到芯片上相比,这真的很昂贵,那么我们为什么要这样做呢?为什么现在对先进封装如此痴迷?先进封装:未来这是我长期以来一直在描述的趋势的一个顶峰。异构计算不仅是专业化要做的事,而且是我们如何将所有这些专业化的碎片放在一起的事。先进的封装是使这一切发挥作用的关键推动因素。让我们来看看苹果M1 - 一种经典的异构计算配置,特别是其统一的内存结构。对我来说,M1的诞生不是一个 "哗众取宠 "的时刻,而是异构计算即将爆发的一个奇特时刻。M1正在敲响未来的样子,许多人很快就会效仿苹果的做法。请注意,实际的SOC(片上系统)不是异构的--但是将内存靠近SOC的定制封装是异构的。M1采用2.5D封装将内存直接封装到处理旁边,不需要PCB连线,另一个非常好的高级封装的好例子是Nvidia的新款A100。再次注意到PCB上没有电线。HBM2 不像传统的 GDDR5 GPU 板设计那样需要围绕 GPU 的大量离散内存芯片,而是包括一个或多个多个内存芯片的垂直堆栈。存储芯片使用微小的导线进行连接,这些导线由硅通孔和微凸起形成。一个 8 Gb HBM2 芯片包含 5,000 多个硅通孔。然后使用无源硅中介层连接内存堆栈和GPU芯片。HBM2 堆栈、GPU 芯片和硅中介层的组合封装在单个 55mm x 55mm BGA 封装中。有关 GP100 和两个 HBM2 堆栈的图示,请参见图 9;有关具有 GPU 和内存的实际 P100 的显微照片,请参见图 10。这里的结论是,世界上最好的芯片都是用一种方式制造出来的,而且这种革命不会停止。接下来介绍高级封装的两个主要类别,2.5D和3D封装。2.5D封装2.5D有点像我们上面提到的倒装芯片的turbo版,但不是将单个裸片堆叠到PCB上,而是将裸片堆叠在单个中介层的顶部。我想这张图很好地说明了这一点。2.5D就像有一个地下室的门进入你邻居的房子,物理上是一个凸点或TSV(通过硅通孔)进入你下面的硅插板,这就把你和你的邻居连接起来。这并不比你实际的片上通信快,但由于你的净输出是由总的封装性能决定的,降低的距离和增加的两个硅片之间的互连超过了没有在一个单一的SOC上的所有缺点。这样做的好处是你可以使用 设计好的“小芯片”来快速拼凑更大更复杂的封装。如果能在一块硅片上完成就更好了,但这种工艺使制造变得更容易,特别是在较小的尺寸上。“小芯片”和2.5D封装可能会使用很长时间,它比3D封装更容易制造,也便宜得多。此外,它可以很好地扩展,并且可以与新的小芯片一起重复使用,从而通过更换小芯片来制造相同封装格式的新芯片。AMD的新的Zen3改进就是这样的,其中封装相似,但一些小芯片得到了升级。3D封装3D封装是一个“圣杯”圣杯,是封装的终极终结。可以这样比喻,现在,与其在地面上拥有所有1层楼高并由地下室连接的独立小房子,不如拥有一座巨大的摩天大楼,该摩天大楼是用适合功能所需的任何工艺定制的。这是3D封装 - 现在所有的封装都是在硅片本身上完成的。它是驱动更大、更复杂结构的最快、最节能的方法,这些结构是为任务而构建的,并将显著延长摩尔定律。未来我们可能无法获得更多的芯片尺寸收缩,但现在有了3D封装,我们仍然可以在未来改进我们的芯片,类似于以前的摩尔定律。而有趣的是,我们有一个整个半导体市场走向3D的明显例子--内存。存储器向3D结构的推进是对未来发展的一个很好的说明。NAND不得不采用3D结构的部分原因是它们在较小的几何尺寸上难以扩展。想象一下,内存是一座大型的3D摩天大楼,每一层都由一个电梯连接起来。这些被称为 "TSV "或通硅孔。这就是未来的样子,我们甚至有可能将GPU / CPU芯片堆叠在彼此上或在CPU上堆叠内存。这是最后的边疆,而现在我们正在迅速接近的边疆。在接下来的5年里,你可能会开始看到3D封装一遍又一遍地出现。2.5D/3D 封装解决方案快速概述我认为,与其进一步了解3D和2.5D封装,不如直接介绍一些正在使用的、你可能已经听说过的工艺。我想在这里重点谈谈晶圆厂所做的工艺,这些工艺是推动了3D/2.5D集成发展的。台积电的CoWoS这似乎是 2.5D 集成工艺的主力,由 Xilinx 率先推出。该过程主要集中在将所有逻辑芯片放入硅中介层上,然后放到封装基板上。一切都通过微凸起或球连接。这是一个经典的2.5D结构。台积电SOIC这个台积电的3D封装平台, 是一个相对较新的技术。。注意这个关于凸点密度和接合间距的惊人图表,SoIC在尺寸上甚至没有接近Flipchip或2.5D,而是在密度和特征尺寸方面几乎是一个前端工艺。这是对他们技术的一个很好的比较,但请注意,SoIC实际上有一个类似于3D堆叠的芯片堆叠,而不是中阶层2.5D集成。三星 XCube近年来,三星已成为更重要的代工厂合作伙伴,当然,为了不被超越,三星拥有了新的3D封装方案。在下面查看他们的XCube的视频。这里没有太多的信息,但我想强调的是,A100是在三星工艺上制造的,所以这可能是为Nvidia最近的芯片提供动力的技术。此外,在这里所有的公司中,三星可能有最丰富的tsv经验。英特尔 Foveros最后是英特尔的Foveros 3D封装。我们可能会看到英特尔在未来7nm及以后的"混合CPU"工艺中实现更多。他们在架构日已经非常明确地表示,这是他们前进的重点。有趣的是,在3D封装过程中,三星,台积电或英特尔之间并没有太大的区别。原文:https://semiwiki.com/semiconductor-services/308968-semiconductor-packaging-history-primer/

芯片封装简史 为什么封装现在很重要封装曾经是半导体制造过程中的事后想法,不被大家重视。当你创造了这一小块神奇的硅片之后,然后把他用某种方法封装起来,同时引出管脚,一颗芯片就诞生了。但是随着摩尔定律的延伸,工程师们意识到,他们可以利用对芯片的所有部分,包括封装在内进行优化和创新,来制造出最好的产品。更令人惊讶的是,过去没有一家封装公司被认为像传统的前端制造工艺那样重要。封装供应链通常被认为是"后端",并被视为成本中心,类似于银行业的前台和后台。但现在,随着前端难以更好的缩小芯片尺寸,一个全新的关注领域已经出现,这就是对先进封装的重视。接下来我们讨论一下封装的发展简史,从简单的DIP封装一直到先进的2.5D或3D封装。封装发展简介这是我从这个精彩的视频座中发现的封装技术的简要层次结构。如果你有一些时间,可以看一下。(视频发表于2012年,但是当时已经提到了现在最新的3D封装技术,所以并不过时) 芯片封装简史@eetop@创芯大讲堂 #封装#芯片#3D封装封装介绍 封装技术一个简化的演变过程是:DIP>QFP>BGA>POP/SiP>WLP 显然,有很多不同的封装技术,但我们要讨论的是大致能代表每种类型的简单技术,然后慢慢将其带到现在。我也非常喜欢下图这个高层次的概述(不过它已经过时了,但仍然正确)。在封装的最初阶段,裸片通常采用陶瓷或金属罐封(气密),以实现最大的可靠性。这主要适用于航空航天和军事应用,这些功能需要最高水平的可靠性。然而,对于我们的大多数日常用例来说,这并不是真正可行的,所以我们开始使用塑料封装和双列直插封装(DIP)。DIP封装(1964-1980年代)最早的DIP包装元件是由仙童半导体司的Bryant Buck Rogers在1964年时发明,在表面贴装技术问世之前的十年里,它被广泛应用。DIP在实际的裸片周围使用塑料封装外壳(编辑注:实际上陶瓷封装的军品芯片也大批采用了DIP封装),并有两排平行的突出的引脚,称为引线框架,与下面的PCB(印刷电路板)相连。实际的芯片通过键合线连接到两个引线框架,两个引线框架可以连接到印刷电路板(PCB)。DIP封装以复古的方式具有标志性,设计选择是可以理解的。实际的裸片将完全密封在树脂中,因此它带来了高可靠性和低成本,并且许多首批标志性的半导体都是以这种方式封装的。请注意,芯片通过导线连接到外部引线框架,这使其成为一种"引线键合"封装方法。稍后将对此进行详细介绍。下面是英特尔8008--实际上是第一批现代微处理器之一。注意它的标志性DIP封装。因此,如果你看到那些看起来像小蜘蛛的半导体的时髦照片,这只是一个DIP封装类的半导体。英特尔的原始微处理器,8008 家族然后,这些小金插针中的每一个都被焊接到PCB上,在那里它与其他电气元件和系统的其余部分接触。以下是封装如何焊接到PCB板上。PCB本身通常是由铜或其他电气元件由非导电材料层压而成。然后,PCB板可以将电信号从一个地方输送到另一个地方,并让个元件相互连接和通信。虽然DIP还有其他演绎版,但实际上是时候转向始于20世纪80年代的下一个封装技术范式或表面贴装封装了。表面贴装封装(1980-1990年代)下一步的变化不是通过DIP安装产品,而是引入表面贴装技术(SMT)。正如所暗示的那样,封装直接安装在PCB的表面上,并允许在一块基板上使用更多的元件并降低成本。下图是典型的表面贴装封装。这种封装有许多变体,在半导体创新的鼎盛时期,这一直是很长一段时间的主力。值得注意的是,大部分芯片都是4个侧面都有引脚。这遵循了封装的一般愿望,即占用更少的空间并增加连接带宽或I / O。每一项额外的进步都会考虑到这一点,并且是一种值得关注的模式。这个过程曾经是手动的,但现在是高度自动化的。此外,这实际上为PCB创造了相当多的问题,如popcorning。封装爆裂是指在焊接过程中,塑料封装内的水分被加热,由于快速加热和冷却,水分在PCB上造成问题。另一件需要注意的事情是,随着封装工艺的每一次提升,复杂性和故障也会随之增加球栅封装和芯片级封装(1990年代至2000年代)随着对半导体速度的需求不断提高,对更好封装的需求也在不断增加。虽然出现了QFN(四方扁平无引线)和其他表面贴装技术,但我想向你介绍一种我们在未来必须了解的封装设计的开端,这就是广泛使用的球栅阵列(BGA)封装的开始。这些焊球或凸起被称为焊料凸起/球这就是球栅阵列的外观,可以从下面直接将一块硅片安装到PCB或基板上,而不是像以前的表面贴装技术那样简单地将所有4端的角落贴上胶带。因此,这只是我上面列出的趋势的另一个延续,占用更少的空间,有更多的连接。现在,我们不再是用电线细细地连接每一侧的封装,而是直接将一个封装连接到另一个。这导致了密度的增加,更好的I/O性能,以及现在增加的复杂性,即你如何检查BGA封装是否工作。在这之前,封装主要是通过视觉检查和测试。现在我们无法看到封装,所以没有办法进行测试。我们可以X射线进行检查,以及更复杂的技术。现代封装(2000-2010年代)我们现在走进了现代封装的时代。上面描述的许多封装方案今天仍在使用,但是,您将开始看到越来越多的封装类型,并且这些封装类型将来会变得更加相关。公平地说,许多这些即将到来的技术是在过去几十年中发明的,但由于成本原因,直到后来才被广泛使用。倒装芯片这是你可能会读到或听到的最常见的封装之一。我很高兴能为你定义它,因为到目前为止,我读过的入门书中还没有一个令人满意的解释。倒装芯片是IBM很早就发明的,通常会被缩写为C4。就倒装芯片而言,它确实不是一种独立的封装形式,而是一种封装风格。它几乎就是只要在芯片上有一个焊接凸点就可以了。芯片不是用线粘合互连,而是翻转过来面对另一个芯片,中间有一个连接基板,所以叫 "倒装芯片"。从维基百科上的解释内容可以更好的理解什么是倒装芯片:在晶圆上创建集成电路芯片表面的焊盘被金属化每个焊盘上都沉积一个焊点芯片被切割芯片被翻转和定位,以便焊球面向电路然后将焊球重新熔化安装好的芯片用电绝缘胶进行底部填充引线键合请注意倒装芯片与引线键合有何不同。上面介绍的DIP封装这就是引线键合,其中芯片使用导线键合到另一种金属上,然后焊接到PCB上。引线键合不是一种特定的技术,而是一套较旧的技术,涵盖了许多不同类型的封装。引线键合是倒装芯片的前身。先进封装(2010年代至今)我们一直在缓慢地进入"先进封装"半导体时代,我现在想谈谈一些更高级的概念。实际上,有各种层次的"封装"适合这个思维过程。我们之前讲过的大多数封装,都集中在芯片封装到PCB上,但先进封装的开始其实是从手机开始的。手机在很多方面都是先进封装诸多方面的巨大前奏。这是有道理的!对于手机需要在尽可能小的空间内集成大量的芯片,比笔记本电脑或台式电脑密度大得多。所有东西都必须被动冷却,当然也要尽可能薄。这将封装推向了新的极限。我们讨论的许多概念都是从智能手机封装开始的,现在已经将自己推向了半导体行业的其他部分。芯片级封装(CSP)芯片级封装实际上比听起来要宽一些,最初意味着芯片大小的封装。技术定义是封装尺寸不超过芯片本身的1.2倍,并且必须是单芯片且可连接的。实际上,我已经向您介绍了CSP的概念,那就是通过倒装芯片。但CSP确实通过智能手机提升到了一个新的水平。这张照片中的所有东西都是芯片芯片的1.2倍大小,并且专注于节省尽可能多的空间。CSP时代有很多不同的风格,包括倒装芯片、右基板和其他技术,都属于这一类。晶圆级封装(WLP)但还有一个更小的级别--这就是 "终极 "芯片规模的封装尺寸,或在晶圆级封装。这几乎就是把封装放在实际的硅片本身。封装的就是硅片。它更薄,具有最高水平的I/O,而且显然会非常热,很难制造。先进的封装革命目前是在CSP的规模上,但未来将集中在晶圆上。这是一个有趣的演变,封装被实际的硅本身所包含。芯片是封装,反之亦然。与仅仅将一些球焊接到芯片上相比,这真的很昂贵,那么我们为什么要这样做呢?为什么现在对先进封装如此痴迷?先进封装:未来这是我长期以来一直在描述的趋势的一个顶峰。异构计算不仅是专业化要做的事,而且是我们如何将所有这些专业化的碎片放在一起的事。先进的封装是使这一切发挥作用的关键推动因素。让我们来看看苹果M1 - 一种经典的异构计算配置,特别是其统一的内存结构。对我来说,M1的诞生不是一个 "哗众取宠 "的时刻,而是异构计算即将爆发的一个奇特时刻。M1正在敲响未来的样子,许多人很快就会效仿苹果的做法。请注意,实际的SOC(片上系统)不是异构的--但是将内存靠近SOC的定制封装是异构的。M1采用2.5D封装将内存直接封装到处理旁边,不需要PCB连线,另一个非常好的高级封装的好例子是Nvidia的新款A100。再次注意到PCB上没有电线。HBM2 不像传统的 GDDR5 GPU 板设计那样需要围绕 GPU 的大量离散内存芯片,而是包括一个或多个多个内存芯片的垂直堆栈。存储芯片使用微小的导线进行连接,这些导线由硅通孔和微凸起形成。一个 8 Gb HBM2 芯片包含 5,000 多个硅通孔。然后使用无源硅中介层连接内存堆栈和GPU芯片。HBM2 堆栈、GPU 芯片和硅中介层的组合封装在单个 55mm x 55mm BGA 封装中。有关 GP100 和两个 HBM2 堆栈的图示,请参见图 9;有关具有 GPU 和内存的实际 P100 的显微照片,请参见图 10。这里的结论是,世界上最好的芯片都是用一种方式制造出来的,而且这种革命不会停止。接下来介绍高级封装的两个主要类别,2.5D和3D封装。2.5D封装2.5D有点像我们上面提到的倒装芯片的turbo版,但不是将单个裸片堆叠到PCB上,而是将裸片堆叠在单个中介层的顶部。我想这张图很好地说明了这一点。2.5D就像有一个地下室的门进入你邻居的房子,物理上是一个凸点或TSV(通过硅通孔)进入你下面的硅插板,这就把你和你的邻居连接起来。这并不比你实际的片上通信快,但由于你的净输出是由总的封装性能决定的,降低的距离和增加的两个硅片之间的互连超过了没有在一个单一的SOC上的所有缺点。这样做的好处是你可以使用 设计好的“小芯片”来快速拼凑更大更复杂的封装。如果能在一块硅片上完成就更好了,但这种工艺使制造变得更容易,特别是在较小的尺寸上。“小芯片”和2.5D封装可能会使用很长时间,它比3D封装更容易制造,也便宜得多。此外,它可以很好地扩展,并且可以与新的小芯片一起重复使用,从而通过更换小芯片来制造相同封装格式的新芯片。AMD的新的Zen3改进就是这样的,其中封装相似,但一些小芯片得到了升级。3D封装3D封装是一个“圣杯”圣杯,是封装的终极终结。可以这样比喻,现在,与其在地面上拥有所有1层楼高并由地下室连接的独立小房子,不如拥有一座巨大的摩天大楼,该摩天大楼是用适合功能所需的任何工艺定制的。这是3D封装 - 现在所有的封装都是在硅片本身上完成的。它是驱动更大、更复杂结构的最快、最节能的方法,这些结构是为任务而构建的,并将显著延长摩尔定律。未来我们可能无法获得更多的芯片尺寸收缩,但现在有了3D封装,我们仍然可以在未来改进我们的芯片,类似于以前的摩尔定律。而有趣的是,我们有一个整个半导体市场走向3D的明显例子--内存。存储器向3D结构的推进是对未来发展的一个很好的说明。NAND不得不采用3D结构的部分原因是它们在较小的几何尺寸上难以扩展。想象一下,内存是一座大型的3D摩天大楼,每一层都由一个电梯连接起来。这些被称为 "TSV "或通硅孔。这就是未来的样子,我们甚至有可能将GPU / CPU芯片堆叠在彼此上或在CPU上堆叠内存。这是最后的边疆,而现在我们正在迅速接近的边疆。在接下来的5年里,你可能会开始看到3D封装一遍又一遍地出现。2.5D/3D 封装解决方案快速概述我认为,与其进一步了解3D和2.5D封装,不如直接介绍一些正在使用的、你可能已经听说过的工艺。我想在这里重点谈谈晶圆厂所做的工艺,这些工艺是推动了3D/2.5D集成发展的。台积电的CoWoS这似乎是 2.5D 集成工艺的主力,由 Xilinx 率先推出。该过程主要集中在将所有逻辑芯片放入硅中介层上,然后放到封装基板上。一切都通过微凸起或球连接。这是一个经典的2.5D结构。台积电SOIC这个台积电的3D封装平台, 是一个相对较新的技术。。注意这个关于凸点密度和接合间距的惊人图表,SoIC在尺寸上甚至没有接近Flipchip或2.5D,而是在密度和特征尺寸方面几乎是一个前端工艺。这是对他们技术的一个很好的比较,但请注意,SoIC实际上有一个类似于3D堆叠的芯片堆叠,而不是中阶层2.5D集成。三星 XCube近年来,三星已成为更重要的代工厂合作伙伴,当然,为了不被超越,三星拥有了新的3D封装方案。在下面查看他们的XCube的视频。这里没有太多的信息,但我想强调的是,A100是在三星工艺上制造的,所以这可能是为Nvidia最近的芯片提供动力的技术。此外,在这里所有的公司中,三星可能有最丰富的tsv经验。英特尔 Foveros最后是英特尔的Foveros 3D封装。我们可能会看到英特尔在未来7nm及以后的"混合CPU"工艺中实现更多。他们在架构日已经非常明确地表示,这是他们前进的重点。有趣的是,在3D封装过程中,三星,台积电或英特尔之间并没有太大的区别。原文:https://semiwiki.com/semiconductor-services/308968-semiconductor-packaging-history-primer/ -

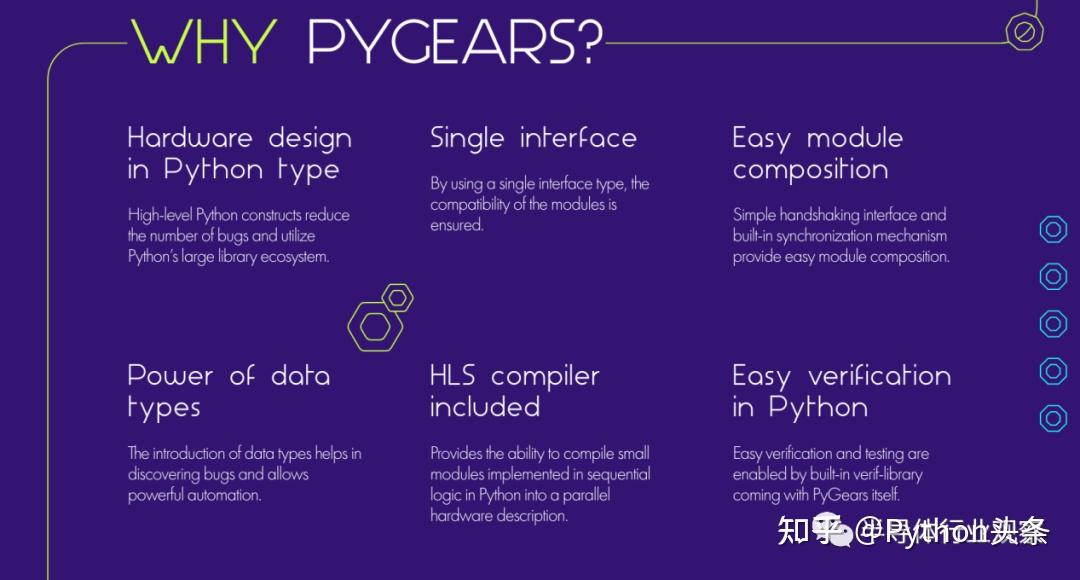

用Python设计芯片?开源设计语言PyGears亮相! 近日,加州大学洛杉矶分校引入了一种新的硬件描述语言PyGears,以实现基于可重用组件和高级 Python 构造的敏捷芯片设计理念。PyGears 是对快速发展的软件世界的回应,这要求硬件设计与可扩展和智能未来的需求保持同步。据官网介绍PyGears 是一种免费的开源硬件描述语言 (HDL),该门语言可作为 Python 库实现,专注于函数式编程、模块组合和同步。按照他们的说法,PyGears 的出现旨在将芯片设计的复杂性转变为简单、灵活且具有成本效益的开发过程,该过程遵循可扩展和智能的方式来构建未来。该框架允许您使用 Python 结构设计硬件并将其编译为可综合的 SystemVerilog 或 Verilog 代码。内置模拟器允许您使用任意 Python 代码及其大量库来验证您的硬件模块。PyGears 使连接模块 得容易 ,并具有内置的同步机制,可帮助您构建正确的并行系统。PYGEAR 的创造者Bogdan Vukobratovic表示:“PyGears 的诞生是为了捕捉我在职业生涯中发现的所有有用的良好实践,该工具可以显着加快复杂架构的硬件实现,尤其是当它们与 AI 范式相关时。这应该是创建下一代芯片设计的一个良好开端,但这个目标需要我们所有人为硬件开发做出贡献并确定其方向。否则,未来的人工智能世界将不可持续。”据报道,通过在 VLSI 信号处理课程中采用它, 加州大学洛杉矶分校 Samueli 工程学院 开始建立一个通过软件范式观察硬件的社区,目标是通过使用更灵活和可组合的模块来加速硬件设计和验证。“芯片设计变得越来越复杂,成本越来越高,开发周期越来越长,”加州大学洛杉矶分校电气和计算机工程教授 Dejan Markovic博士说。“PyGears 通过采用由志同道合的贡献者社区构建的可重用组件的模块化硬件构建来解决这些挑战。这对于小型和大型工程团队都非常有效。硬件设计和验证基于Python环境,减少了软硬件领域的壁垒。我们的愿景是让软件人员能够编写硬件代码。”“软件的最大限制是硬件发展速度相对较慢,” Lux Capital 的合伙人Shahin Farshchi说。“PyGears 站在巨人的肩膀上,将硬件设计加速到接近‘编码’的速度,这将带来神奇的新用例,为定义市场的产品和公司提供支持。”PyGears的创建者兼 Anari AI 研发负责人Bogdan Vukobratovic博士表示,当前的工具行业倾向于对硬件开发中的所有组件进行低级优化和低级控制。另一方面,PyGears 提供对所有方面直至最低层的控制,使流程效率提高数倍。他还强调,构建复杂的架构需要具有更高开发敏捷性的系统。根据斯坦福大学教授 Boris Murmann博士的说法。,“新硬件设计工具的开发可以极大地受益于开源解决方案。为了让硬件行业摆脱石器时代并使其更加敏捷,我们需要社区塑造的新概念。”除了 UCLA 学生和其他大学,PyGears 团队已经 向硬件团队和有兴趣改进 HDL 的个人开放社区,使硬件设计更加高效和以结果为导向。附部分说明截图

用Python设计芯片?开源设计语言PyGears亮相! 近日,加州大学洛杉矶分校引入了一种新的硬件描述语言PyGears,以实现基于可重用组件和高级 Python 构造的敏捷芯片设计理念。PyGears 是对快速发展的软件世界的回应,这要求硬件设计与可扩展和智能未来的需求保持同步。据官网介绍PyGears 是一种免费的开源硬件描述语言 (HDL),该门语言可作为 Python 库实现,专注于函数式编程、模块组合和同步。按照他们的说法,PyGears 的出现旨在将芯片设计的复杂性转变为简单、灵活且具有成本效益的开发过程,该过程遵循可扩展和智能的方式来构建未来。该框架允许您使用 Python 结构设计硬件并将其编译为可综合的 SystemVerilog 或 Verilog 代码。内置模拟器允许您使用任意 Python 代码及其大量库来验证您的硬件模块。PyGears 使连接模块 得容易 ,并具有内置的同步机制,可帮助您构建正确的并行系统。PYGEAR 的创造者Bogdan Vukobratovic表示:“PyGears 的诞生是为了捕捉我在职业生涯中发现的所有有用的良好实践,该工具可以显着加快复杂架构的硬件实现,尤其是当它们与 AI 范式相关时。这应该是创建下一代芯片设计的一个良好开端,但这个目标需要我们所有人为硬件开发做出贡献并确定其方向。否则,未来的人工智能世界将不可持续。”据报道,通过在 VLSI 信号处理课程中采用它, 加州大学洛杉矶分校 Samueli 工程学院 开始建立一个通过软件范式观察硬件的社区,目标是通过使用更灵活和可组合的模块来加速硬件设计和验证。“芯片设计变得越来越复杂,成本越来越高,开发周期越来越长,”加州大学洛杉矶分校电气和计算机工程教授 Dejan Markovic博士说。“PyGears 通过采用由志同道合的贡献者社区构建的可重用组件的模块化硬件构建来解决这些挑战。这对于小型和大型工程团队都非常有效。硬件设计和验证基于Python环境,减少了软硬件领域的壁垒。我们的愿景是让软件人员能够编写硬件代码。”“软件的最大限制是硬件发展速度相对较慢,” Lux Capital 的合伙人Shahin Farshchi说。“PyGears 站在巨人的肩膀上,将硬件设计加速到接近‘编码’的速度,这将带来神奇的新用例,为定义市场的产品和公司提供支持。”PyGears的创建者兼 Anari AI 研发负责人Bogdan Vukobratovic博士表示,当前的工具行业倾向于对硬件开发中的所有组件进行低级优化和低级控制。另一方面,PyGears 提供对所有方面直至最低层的控制,使流程效率提高数倍。他还强调,构建复杂的架构需要具有更高开发敏捷性的系统。根据斯坦福大学教授 Boris Murmann博士的说法。,“新硬件设计工具的开发可以极大地受益于开源解决方案。为了让硬件行业摆脱石器时代并使其更加敏捷,我们需要社区塑造的新概念。”除了 UCLA 学生和其他大学,PyGears 团队已经 向硬件团队和有兴趣改进 HDL 的个人开放社区,使硬件设计更加高效和以结果为导向。附部分说明截图 -

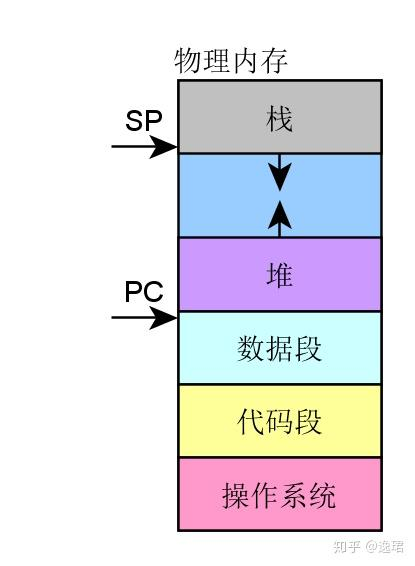

MMU那些事儿 EET0P2020年12月27日03:47MMU 诞生之前:在传统的批处理系统如 DOS 系统,应用程序与操作系统在内存中的布局大致如下图:应用程序直接访问物理内存,操作系统占用一部分内存区。操作系统的职责是“加载”应用程序,“运行”或“卸载”应用程序。如果我们一直是单任务处理,则不会有任何问题,也或者应用程序所需的内存总是非常小,则这种架构是不会有任何问题的。然而随着计算机科学技术的发展,所需解决的问题越来越复杂,单任务批处理已不能满足需求了。而且应用程序需要的内存量也越来越大。而且伴随着多任务同时处理的需求,这种技术架构已然不能满足需求了,早先的多任务处理系统是怎么运作的呢?程序员将应用程序分段加载执行,但是分段是一个苦力活。而且死板枯燥。此时聪明的计算机科学家想到了好办法,提出来虚拟内存的思想。程序所需的内存可以远超物理内存的大小,将当前需要执行的留在内存中,而不需要执行的部分留在磁盘中,这样同时就可以满足多应用程序同时驻留内存能并发执行了。从总体上而言,需要实现哪些大的策略呢?所有的应用程序能同时驻留内存,并由操作系统调度并发执行。需要提供机制管理 I/O 重叠,CPU 资源竞争访问。虚实内存映射及交换管理,可以将真实的物理内存,有可变或固定的分区,分页或者分段与虚拟内存建立交换映射关系,并且有效的管理这种映射,实现交换管理。这样,衍生而来的一些实现上的更具体的需求:竞争访问保护管理需求:需要严格的访问保护,动态管理哪些内存页/段或区,为哪些应用程序所用。这属于资源的竞争访问管理需求。高效的翻译转换管理需求:需要实现快速高效的映射翻译转换,否则系统的运行效率将会低下。高效的虚实内存交换需求:需要在实际的虚拟内存与物理内存进行内存页/段交换过程中快速高效。总之,在这样的背景下,MMU 应运而生,也由此可见,任何一项技术的发展壮大,都必然是需求驱动的。这是技术本身发展的客观规律。内存管理的好处为编程提供方便统一的内存空间抽象,在应用开发而言,好似都完全拥有各自独立的用户内存空间的访问权限,这样隐藏了底层实现细节,提供了统一可移植用户抽象。 以最小的开销换取性能最大化,利用 MMU 管理内存肯定不如直接对内存进行访问效率高,为什么需要用这样的机制进行内存管理,是因为并发进程每个进程都拥有完整且相互独立的内存空间。那么实际上内存是昂贵的,即使内存成本远比从前便宜,但是应用进程对内存的寻求仍然无法在实际硬件中,设计足够大的内存实现直接访问,即使能满足,CPU 利用地址总线直接寻址空间也是有限的。内存管理实现总体策略从操作系统角度来看,虚拟内存的基本抽象由操作系统实现完成:处理器内存空间不必与真实的所连接的物理内存空间一致。 当应用程序请求访问内存时,操作系统将虚拟内存地址翻译成物理内存地址,然后完成访问。 从应用程序角度来看,应用程序(往往是进程)所使用的地址是虚拟内存地址,从概念上就如下示意图所示,MMU 在操作系统的控制下负责将虚拟内存实际翻译成物理内存。从而这样的机制,虚拟内存使得应用程序不用将其全部内容都一次性驻留在内存中执行: 节省内存:很多应用程序都不必让其全部内容一次性加载驻留在内存中,那么这样的好处是显而易见,即使硬件系统配置多大的内存,内存在系统中仍然是最为珍贵的资源。所以这种技术节省内存的好处是显而易见的。 使得应用程序以及操作系统更具灵活性。操作系统根据应用程序的动态运行时行为灵活的分配内存给应用程序。使得应用程序可以使用比实际物理内存多或少的内存空间。MMU 以及 TLBMMU(Memory Management Unit)内存管理单元:一种硬件电路单元负责将虚拟内存地址转换为物理内存地址所有的内存访问都将通过 MMU 进行转换,除非没有使能 MMU。TLB(Translation Lookaside Buffer)转译后备缓冲器: 本质上是 MMU 用于虚拟地址到物理地址转换表的缓存这样一种架构,其最终运行时目的,是为主要满足下面这样运行需求:多进程并发同时并发运行在实际物理内存空间中,而 MMU 充当了一个至关重要的虚拟内存到物理内存的桥梁作用。那么,这种框架具体从高层级的概念上是怎么做到的呢?事实上,是将物理内存采用分片管理的策略来实现的,那么,从实现的角度将有两种可选的策略:固定大小分区机制可变大小分区机制固定大小区片机制通过这样一种概念上的策略,将物理内存分成固定等大小的片: 每一个片提供一个基地址 实际寻址,物理地址=某片基址+虚拟地址 片基址由操作系统在进程动态运行时动态加载这种策略实现,其优势在于简易,切换快速。但是该策略也带来明显的劣势: 内部碎片:一个进程不使用的分区中的内存对其他进程而言无法使用 一种分区大小并不能满足所有应用进程所需。可变大小分区机制内存被划分为可变大小的区块进行映射交换管理: 需要提供基址以及可变大小边界,可变大小边界用于越界保护。实 际寻址,物理地址=某片基址+虚拟地址那么这种策略其优势在于没有内部内存碎片,分配刚好够进程所需的大小。但是劣势在于,在加载和卸载的动态过程中会产生碎片。分页机制分页机制采用在虚拟内存空间以及物理内存空间都使用固定大小的分区进行映射管理。从应用程序(进程)角度看内存是连续的 0-N 的分页的虚拟地址空间。物理内存角度看,内存页是分散在整个物理存储中这种映射关系对应用程序不可见,隐藏了实现细节。分页机制是如何寻址的呢?这里介绍的设计理念,具体的处理器实现各有细微差异:虚拟地址包含了两个部分:虚拟页序号 VPN(virtual paging number)以及偏移量虚拟页序号 VPN是页表(Page Table)的索引页表(Page Table)维护了页框号(Page frame number PFN)物理地址由PFN::Offset进行解析。举个栗子,如下图所示:还没有查到具体的物理地址,憋急,再看一下完整解析示例:如何管理页表对于 32 位地址空间而言,假定 4K 为分页大小,则页表的大小为 100MB,这对于页表的查询而言是一个很大的开销。那么如何减小这种开销呢?实际运行过程中发现,事实上只需要映射实际使用的很小一部分地址空间。那么在一级页机制基础上,延伸出多级页表机制。 以二级分页机制为例:单级页表已然有不小的开销,查询页表以及取数,而二级分页机制,因为需要查询两次页表,则将这种开销再加一倍。那么如何提高效率呢?其实前面提到一个概念一直还没有深入描述 TLB,将翻译工作由硬件缓存 cache,这就是 TLB 存在的意义。 TLB 将虚拟页翻译成 PTE,这个工作可在单周期指令完成。TLB 由硬件实现完全关联缓存(并行查找所有条目)缓存索引是虚拟页码缓存内容是 PTE则由 PTE+offset,可直接计算出物理地址TLB 加载谁负责加载 TLB 呢?这里可供选择的有两种策略:由操作系统加载,操作系统找到对应的 PTE,而后加载到 TLB。格式比较灵活。MMU 硬件负责,由操作系统维护页表,MMU 直接访问页表,页表格式严格依赖硬件设计格式。总结一下从计算机大致发展历程来了解内存管理的大致发展策略,如何衍生出 MMU,以及固定分片管理、可变分片管理等不同机制的差异,最后衍生出单级分页管理机制、多级分页管理机制、TLB 的作用。从概念上相对比较易懂的角度描述了 MMU 的诞生、机制,而忽略了处理器的具体实现细节。作为从概念上更深入的理解 MMU 的工作机理的角度,还是不失为一篇浅显易懂的文章。

MMU那些事儿 EET0P2020年12月27日03:47MMU 诞生之前:在传统的批处理系统如 DOS 系统,应用程序与操作系统在内存中的布局大致如下图:应用程序直接访问物理内存,操作系统占用一部分内存区。操作系统的职责是“加载”应用程序,“运行”或“卸载”应用程序。如果我们一直是单任务处理,则不会有任何问题,也或者应用程序所需的内存总是非常小,则这种架构是不会有任何问题的。然而随着计算机科学技术的发展,所需解决的问题越来越复杂,单任务批处理已不能满足需求了。而且应用程序需要的内存量也越来越大。而且伴随着多任务同时处理的需求,这种技术架构已然不能满足需求了,早先的多任务处理系统是怎么运作的呢?程序员将应用程序分段加载执行,但是分段是一个苦力活。而且死板枯燥。此时聪明的计算机科学家想到了好办法,提出来虚拟内存的思想。程序所需的内存可以远超物理内存的大小,将当前需要执行的留在内存中,而不需要执行的部分留在磁盘中,这样同时就可以满足多应用程序同时驻留内存能并发执行了。从总体上而言,需要实现哪些大的策略呢?所有的应用程序能同时驻留内存,并由操作系统调度并发执行。需要提供机制管理 I/O 重叠,CPU 资源竞争访问。虚实内存映射及交换管理,可以将真实的物理内存,有可变或固定的分区,分页或者分段与虚拟内存建立交换映射关系,并且有效的管理这种映射,实现交换管理。这样,衍生而来的一些实现上的更具体的需求:竞争访问保护管理需求:需要严格的访问保护,动态管理哪些内存页/段或区,为哪些应用程序所用。这属于资源的竞争访问管理需求。高效的翻译转换管理需求:需要实现快速高效的映射翻译转换,否则系统的运行效率将会低下。高效的虚实内存交换需求:需要在实际的虚拟内存与物理内存进行内存页/段交换过程中快速高效。总之,在这样的背景下,MMU 应运而生,也由此可见,任何一项技术的发展壮大,都必然是需求驱动的。这是技术本身发展的客观规律。内存管理的好处为编程提供方便统一的内存空间抽象,在应用开发而言,好似都完全拥有各自独立的用户内存空间的访问权限,这样隐藏了底层实现细节,提供了统一可移植用户抽象。 以最小的开销换取性能最大化,利用 MMU 管理内存肯定不如直接对内存进行访问效率高,为什么需要用这样的机制进行内存管理,是因为并发进程每个进程都拥有完整且相互独立的内存空间。那么实际上内存是昂贵的,即使内存成本远比从前便宜,但是应用进程对内存的寻求仍然无法在实际硬件中,设计足够大的内存实现直接访问,即使能满足,CPU 利用地址总线直接寻址空间也是有限的。内存管理实现总体策略从操作系统角度来看,虚拟内存的基本抽象由操作系统实现完成:处理器内存空间不必与真实的所连接的物理内存空间一致。 当应用程序请求访问内存时,操作系统将虚拟内存地址翻译成物理内存地址,然后完成访问。 从应用程序角度来看,应用程序(往往是进程)所使用的地址是虚拟内存地址,从概念上就如下示意图所示,MMU 在操作系统的控制下负责将虚拟内存实际翻译成物理内存。从而这样的机制,虚拟内存使得应用程序不用将其全部内容都一次性驻留在内存中执行: 节省内存:很多应用程序都不必让其全部内容一次性加载驻留在内存中,那么这样的好处是显而易见,即使硬件系统配置多大的内存,内存在系统中仍然是最为珍贵的资源。所以这种技术节省内存的好处是显而易见的。 使得应用程序以及操作系统更具灵活性。操作系统根据应用程序的动态运行时行为灵活的分配内存给应用程序。使得应用程序可以使用比实际物理内存多或少的内存空间。MMU 以及 TLBMMU(Memory Management Unit)内存管理单元:一种硬件电路单元负责将虚拟内存地址转换为物理内存地址所有的内存访问都将通过 MMU 进行转换,除非没有使能 MMU。TLB(Translation Lookaside Buffer)转译后备缓冲器: 本质上是 MMU 用于虚拟地址到物理地址转换表的缓存这样一种架构,其最终运行时目的,是为主要满足下面这样运行需求:多进程并发同时并发运行在实际物理内存空间中,而 MMU 充当了一个至关重要的虚拟内存到物理内存的桥梁作用。那么,这种框架具体从高层级的概念上是怎么做到的呢?事实上,是将物理内存采用分片管理的策略来实现的,那么,从实现的角度将有两种可选的策略:固定大小分区机制可变大小分区机制固定大小区片机制通过这样一种概念上的策略,将物理内存分成固定等大小的片: 每一个片提供一个基地址 实际寻址,物理地址=某片基址+虚拟地址 片基址由操作系统在进程动态运行时动态加载这种策略实现,其优势在于简易,切换快速。但是该策略也带来明显的劣势: 内部碎片:一个进程不使用的分区中的内存对其他进程而言无法使用 一种分区大小并不能满足所有应用进程所需。可变大小分区机制内存被划分为可变大小的区块进行映射交换管理: 需要提供基址以及可变大小边界,可变大小边界用于越界保护。实 际寻址,物理地址=某片基址+虚拟地址那么这种策略其优势在于没有内部内存碎片,分配刚好够进程所需的大小。但是劣势在于,在加载和卸载的动态过程中会产生碎片。分页机制分页机制采用在虚拟内存空间以及物理内存空间都使用固定大小的分区进行映射管理。从应用程序(进程)角度看内存是连续的 0-N 的分页的虚拟地址空间。物理内存角度看,内存页是分散在整个物理存储中这种映射关系对应用程序不可见,隐藏了实现细节。分页机制是如何寻址的呢?这里介绍的设计理念,具体的处理器实现各有细微差异:虚拟地址包含了两个部分:虚拟页序号 VPN(virtual paging number)以及偏移量虚拟页序号 VPN是页表(Page Table)的索引页表(Page Table)维护了页框号(Page frame number PFN)物理地址由PFN::Offset进行解析。举个栗子,如下图所示:还没有查到具体的物理地址,憋急,再看一下完整解析示例:如何管理页表对于 32 位地址空间而言,假定 4K 为分页大小,则页表的大小为 100MB,这对于页表的查询而言是一个很大的开销。那么如何减小这种开销呢?实际运行过程中发现,事实上只需要映射实际使用的很小一部分地址空间。那么在一级页机制基础上,延伸出多级页表机制。 以二级分页机制为例:单级页表已然有不小的开销,查询页表以及取数,而二级分页机制,因为需要查询两次页表,则将这种开销再加一倍。那么如何提高效率呢?其实前面提到一个概念一直还没有深入描述 TLB,将翻译工作由硬件缓存 cache,这就是 TLB 存在的意义。 TLB 将虚拟页翻译成 PTE,这个工作可在单周期指令完成。TLB 由硬件实现完全关联缓存(并行查找所有条目)缓存索引是虚拟页码缓存内容是 PTE则由 PTE+offset,可直接计算出物理地址TLB 加载谁负责加载 TLB 呢?这里可供选择的有两种策略:由操作系统加载,操作系统找到对应的 PTE,而后加载到 TLB。格式比较灵活。MMU 硬件负责,由操作系统维护页表,MMU 直接访问页表,页表格式严格依赖硬件设计格式。总结一下从计算机大致发展历程来了解内存管理的大致发展策略,如何衍生出 MMU,以及固定分片管理、可变分片管理等不同机制的差异,最后衍生出单级分页管理机制、多级分页管理机制、TLB 的作用。从概念上相对比较易懂的角度描述了 MMU 的诞生、机制,而忽略了处理器的具体实现细节。作为从概念上更深入的理解 MMU 的工作机理的角度,还是不失为一篇浅显易懂的文章。 -

Python 必杀技:用 print() 函数实现的三个特效 print() 应该是初学者最先接触到的第一个 Python 函数,因为几乎所有的启蒙课程都是从 print('Hello world') 开始的。事实上, print() 也是程序员使用频率最高的函数之一,同时也是很多程序员喜欢的代码调试利器。但是关于 print() 函数,你真的了解吗?打字机效果不了解 print() 的 flush 参数,很难实现下图所示的打字机效果:动图封面print() 像个调皮的小朋友,你让他帮你打印,他一定会做,但未必是立即去做,也许会攒够了多个打印任务才执行一次。设置 flush=True,可以让这位小朋友立刻去执行命令。 import time def printer(text, delay=0.2): """打字机效果""" for ch in text: print(ch, end='', flush=True) time.sleep(delay) printer('玄铁重剑,是金庸小说笔下第一神剑,持之则无敌于天下。')旋转式进度指示Linux 系统文本界面下,最常用的进度指示是用横竖斜杠构成的旋转图案。动图封面Python也可以轻松实现这个效果,秘诀就在于 '\b' 字符。 '\b' 相当于键盘上的退格键,可以让我们把刚刚打印过的最后一个字符擦掉重新打印。这个效果,同样需要设置参数 flush 为真。 import time def waiting(cycle=20, delay=0.1): """旋转式进度指示""" for i in range(cycle): for ch in ['-', '\\', '|', '/']: print('\b%s'%ch, end='', flush=True) time.sleep(delay) waiting() 反转字符顺序,就可以改变旋转方向。将第一个字符 '-' 改成 '-- ',还可以实现这样的效果:动图封面覆盖式打印效果'\b' 的作用是回退一个字符,'\r' 则可以退回到行首。借助于 '\r',可以实现整行覆盖式的打印效果:动图封面需要注意的是,整行覆盖的话,新的字符串长度不能小于原字符串长度,否则会留下前一次的打印内容。这个效果,同样需要设置参数 flush 为真。 import time def cover(cycle=100, delay=0.2): """覆盖式打印效果""" for i in range(cycle): s = '\r%d'%i print(s.ljust(3), end='', flush=True) time.sleep(delay) cover()

Python 必杀技:用 print() 函数实现的三个特效 print() 应该是初学者最先接触到的第一个 Python 函数,因为几乎所有的启蒙课程都是从 print('Hello world') 开始的。事实上, print() 也是程序员使用频率最高的函数之一,同时也是很多程序员喜欢的代码调试利器。但是关于 print() 函数,你真的了解吗?打字机效果不了解 print() 的 flush 参数,很难实现下图所示的打字机效果:动图封面print() 像个调皮的小朋友,你让他帮你打印,他一定会做,但未必是立即去做,也许会攒够了多个打印任务才执行一次。设置 flush=True,可以让这位小朋友立刻去执行命令。 import time def printer(text, delay=0.2): """打字机效果""" for ch in text: print(ch, end='', flush=True) time.sleep(delay) printer('玄铁重剑,是金庸小说笔下第一神剑,持之则无敌于天下。')旋转式进度指示Linux 系统文本界面下,最常用的进度指示是用横竖斜杠构成的旋转图案。动图封面Python也可以轻松实现这个效果,秘诀就在于 '\b' 字符。 '\b' 相当于键盘上的退格键,可以让我们把刚刚打印过的最后一个字符擦掉重新打印。这个效果,同样需要设置参数 flush 为真。 import time def waiting(cycle=20, delay=0.1): """旋转式进度指示""" for i in range(cycle): for ch in ['-', '\\', '|', '/']: print('\b%s'%ch, end='', flush=True) time.sleep(delay) waiting() 反转字符顺序,就可以改变旋转方向。将第一个字符 '-' 改成 '-- ',还可以实现这样的效果:动图封面覆盖式打印效果'\b' 的作用是回退一个字符,'\r' 则可以退回到行首。借助于 '\r',可以实现整行覆盖式的打印效果:动图封面需要注意的是,整行覆盖的话,新的字符串长度不能小于原字符串长度,否则会留下前一次的打印内容。这个效果,同样需要设置参数 flush 为真。 import time def cover(cycle=100, delay=0.2): """覆盖式打印效果""" for i in range(cycle): s = '\r%d'%i print(s.ljust(3), end='', flush=True) time.sleep(delay) cover() -