搜索到

6

篇与

的结果

-

vivado与vscode完美结合 vivado虽然非常优秀,但是也有一个缺点就是vivado的编辑器很难用1、没有高亮(不完整的)2、不能自动补全3、背景白色很伤眼4、没有自动跳转到定义功能5、没有括号定位功能这篇文章,我将把这几个全部解决,同时也不是完全使用vscode编写verilog工程,因为ip核的部分必须用vivado才方便,所以我推荐编写代码用vscode,其余功能还在vivado实现,这样就需要把vivado的代码文件用vscode打开,同时跟我在vscode中进行一些设置,让vscode成为vivado的专属编辑软件,提升编写代码效率。废话不多说直接上干货!!!!1、下载安装vscode(安装过的可以忽略)下载地址:vscode官方下载地址感觉官方下载速度慢的,也给大家准备好了安装包 :vscode安装包安装教程:傻瓜式安装,一路点下一步即可安装成功。2、插件安装(1)中文语言包 Language Pack for Visual Studio Code(2)代码高亮 Code formatter(3)verilog 支持包 Verilog-HDL/SystemVerilog/Bluespec SystemVerilog其余还有很多插件,我认为安装这三个足够了,其余用到的时候再安装,这三个已经完全够用!3、实现自动纠错在其他编辑器,编写verilog最大的问题就是不能自动纠错,下面介绍一个最简单的方法(1)提前你的PC需要安装vivado,并把下面的路径复制(我的为例)D:\Xilinx\Vivado\2018.3\bin(2)并把这个地址添加到系统环境变量的Path中:(3)在PC的cmd窗口输入:xvlog --version 查看是否生效,如果没有打印出未找到该命令,那么你可能需要重启您的电脑。(4)接下来我们在vscode设置里,搜索Linter,将verilog的Linter更换成xvlog。设置完成之后,就能实现语法的纠错,在平常的工程编写中非常舒服。4、自动跳转到定义变量的位置在编写verilog有一个跟头疼的问题,就是不能像C那样直接跳转到定义变量的位置,有时候定义的变量多了,就不知道位宽和这个变量的意义了,还有从头去找,很是麻烦,下面介绍一种非常简单的就能跳转到定义位置的方法。(1)下载插件ctags.exe文件下载地址:ctags.exe下载并把他复制到vivado安装目录下:(2)复制ctags.exe文件位置D:\Xilinx\ctags-p6.1.20240114.0-x64(3)把ctags.exe地址添加到系统环境变量Path中(4)打开vscode搜索ctags,并把地址添进去D:\Xilinx\ctags-p6.1.20240114.0-x64||ctags.exe(5)重新打开vscode即可实现变量快速跳转5、括号自动匹配(1)打开设置搜索,然后把这两个都勾选上即可@id:editor.bracketPairColorization.enabled @id:editor.guides.bracketPairs(2)重新打开vscode即可实现括号自动匹配(也包括begin end)6、代码里面中文乱码换一个编辑器打开代码,里面的中文注释全部变成不认识的符号,这种问题大家是不是经常遇到,今天教大家一次性解决这个的问题vivado中代码形式默认为GB2312模式,所以我们只需要把vscode中默认代码形式改为GB2312即可打开vscode设置界面,搜索 encoding,把这个改为GB2312即可这样代码里的注释,都能显示出来了这样一个只属于vivado的vscode已经设置完成了,就可以很轻松愉快的在vscode和vivado中间穿梭,非常的丝滑,后续如果有更好的插件或者设置,还是会在这个文章上面继续更新!!如果感觉文章对您有用,麻烦三连支持一下,方便下次用到的时候,就可以快速找到我,非常感谢您的支持!!!————————————————版权声明:本文为CSDN博主「FPGAmaster创新者」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。原文链接:https://blog.csdn.net/w18864443115/article/details/135604467

vivado与vscode完美结合 vivado虽然非常优秀,但是也有一个缺点就是vivado的编辑器很难用1、没有高亮(不完整的)2、不能自动补全3、背景白色很伤眼4、没有自动跳转到定义功能5、没有括号定位功能这篇文章,我将把这几个全部解决,同时也不是完全使用vscode编写verilog工程,因为ip核的部分必须用vivado才方便,所以我推荐编写代码用vscode,其余功能还在vivado实现,这样就需要把vivado的代码文件用vscode打开,同时跟我在vscode中进行一些设置,让vscode成为vivado的专属编辑软件,提升编写代码效率。废话不多说直接上干货!!!!1、下载安装vscode(安装过的可以忽略)下载地址:vscode官方下载地址感觉官方下载速度慢的,也给大家准备好了安装包 :vscode安装包安装教程:傻瓜式安装,一路点下一步即可安装成功。2、插件安装(1)中文语言包 Language Pack for Visual Studio Code(2)代码高亮 Code formatter(3)verilog 支持包 Verilog-HDL/SystemVerilog/Bluespec SystemVerilog其余还有很多插件,我认为安装这三个足够了,其余用到的时候再安装,这三个已经完全够用!3、实现自动纠错在其他编辑器,编写verilog最大的问题就是不能自动纠错,下面介绍一个最简单的方法(1)提前你的PC需要安装vivado,并把下面的路径复制(我的为例)D:\Xilinx\Vivado\2018.3\bin(2)并把这个地址添加到系统环境变量的Path中:(3)在PC的cmd窗口输入:xvlog --version 查看是否生效,如果没有打印出未找到该命令,那么你可能需要重启您的电脑。(4)接下来我们在vscode设置里,搜索Linter,将verilog的Linter更换成xvlog。设置完成之后,就能实现语法的纠错,在平常的工程编写中非常舒服。4、自动跳转到定义变量的位置在编写verilog有一个跟头疼的问题,就是不能像C那样直接跳转到定义变量的位置,有时候定义的变量多了,就不知道位宽和这个变量的意义了,还有从头去找,很是麻烦,下面介绍一种非常简单的就能跳转到定义位置的方法。(1)下载插件ctags.exe文件下载地址:ctags.exe下载并把他复制到vivado安装目录下:(2)复制ctags.exe文件位置D:\Xilinx\ctags-p6.1.20240114.0-x64(3)把ctags.exe地址添加到系统环境变量Path中(4)打开vscode搜索ctags,并把地址添进去D:\Xilinx\ctags-p6.1.20240114.0-x64||ctags.exe(5)重新打开vscode即可实现变量快速跳转5、括号自动匹配(1)打开设置搜索,然后把这两个都勾选上即可@id:editor.bracketPairColorization.enabled @id:editor.guides.bracketPairs(2)重新打开vscode即可实现括号自动匹配(也包括begin end)6、代码里面中文乱码换一个编辑器打开代码,里面的中文注释全部变成不认识的符号,这种问题大家是不是经常遇到,今天教大家一次性解决这个的问题vivado中代码形式默认为GB2312模式,所以我们只需要把vscode中默认代码形式改为GB2312即可打开vscode设置界面,搜索 encoding,把这个改为GB2312即可这样代码里的注释,都能显示出来了这样一个只属于vivado的vscode已经设置完成了,就可以很轻松愉快的在vscode和vivado中间穿梭,非常的丝滑,后续如果有更好的插件或者设置,还是会在这个文章上面继续更新!!如果感觉文章对您有用,麻烦三连支持一下,方便下次用到的时候,就可以快速找到我,非常感谢您的支持!!!————————————————版权声明:本文为CSDN博主「FPGAmaster创新者」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。原文链接:https://blog.csdn.net/w18864443115/article/details/135604467 -

如何使用vsCode+Icarus verilog+GTKwave编写并仿真verilog 用VS Code + iverilog + GTKwave仿真Verilog【下载地址】用VSCodeiverilogGTKwave仿真Verilog分享用VS Code + iverilog + GTKwave仿真Verilog本资源文件提供了一个详细的教程,指导如何在VS Code中使用iverilog和GTKwave工具进行Verilog代码的仿真 项目地址: https://gitcode.com/Resource-Bundle-Collection/9dfab本资源文件提供了一个详细的教程,指导如何在VS Code中使用iverilog和GTKwave工具进行Verilog代码的仿真。通过本教程,您将学会如何配置VS Code环境,编写和编译Verilog代码,并使用GTKwave查看仿真波形。内容概述VS Code部分安装VS Code并配置Verilog插件。创建Verilog源代码文件并进行编辑。iverilog部分下载并安装iverilog编译器。使用iverilog编译Verilog代码生成VVP文件。GTKwave部分使用GTKwave查看仿真生成的VCD文件。调整波形显示以方便分析。使用步骤安装VS Code首先,下载并安装VS Code。安装完成后,打开VS Code并安装Verilog插件,以便在编辑Verilog代码时获得语法高亮和错误检查功能。编写Verilog代码在VS Code中创建一个新的Verilog文件,编写您的Verilog代码。您可以参考教程中的示例代码,编写一个简单的计数器模块。编写测试文件创建一个测试文件(testbench),用于测试您的Verilog模块。测试文件中应包含初始化代码、时钟生成代码以及仿真结束的控制代码。编译Verilog代码使用iverilog编译器将Verilog代码和测试文件编译成VVP文件。编译命令如下:iverilog -o "test_tb.vvp" test_tb.v test.v运行仿真在命令行中运行生成的VVP文件,生成VCD波形文件:vvp test_tb.vvp查看波形使用GTKwave打开生成的VCD文件,查看仿真波形。您可以通过调整波形显示来分析仿真结果。注意事项确保iverilog和GTKwave已正确安装并配置好环境变量。在编写Verilog代码时,注意模块的输入输出定义和时序逻辑的正确性。在仿真过程中,可以通过调整测试文件中的参数来验证不同条件下的仿真结果。通过本教程,您将能够熟练使用VS Code、iverilog和GTKwave进行Verilog代码的仿真,为硬件设计提供强大的支持。【下载地址】用VSCodeiverilogGTKwave仿真Verilog分享用VS Code + iverilog + GTKwave仿真Verilog本资源文件提供了一个详细的教程,指导如何在VS Code中使用iverilog和GTKwave工具进行Verilog代码的仿真 项目地址: https://gitcode.com/Resource-Bundle-Collection/9dfab————————————————版权声明:本文为CSDN博主「邱蒙励」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。原文链接:https://blog.csdn.net/gitblog_06576/article/details/143385319

如何使用vsCode+Icarus verilog+GTKwave编写并仿真verilog 用VS Code + iverilog + GTKwave仿真Verilog【下载地址】用VSCodeiverilogGTKwave仿真Verilog分享用VS Code + iverilog + GTKwave仿真Verilog本资源文件提供了一个详细的教程,指导如何在VS Code中使用iverilog和GTKwave工具进行Verilog代码的仿真 项目地址: https://gitcode.com/Resource-Bundle-Collection/9dfab本资源文件提供了一个详细的教程,指导如何在VS Code中使用iverilog和GTKwave工具进行Verilog代码的仿真。通过本教程,您将学会如何配置VS Code环境,编写和编译Verilog代码,并使用GTKwave查看仿真波形。内容概述VS Code部分安装VS Code并配置Verilog插件。创建Verilog源代码文件并进行编辑。iverilog部分下载并安装iverilog编译器。使用iverilog编译Verilog代码生成VVP文件。GTKwave部分使用GTKwave查看仿真生成的VCD文件。调整波形显示以方便分析。使用步骤安装VS Code首先,下载并安装VS Code。安装完成后,打开VS Code并安装Verilog插件,以便在编辑Verilog代码时获得语法高亮和错误检查功能。编写Verilog代码在VS Code中创建一个新的Verilog文件,编写您的Verilog代码。您可以参考教程中的示例代码,编写一个简单的计数器模块。编写测试文件创建一个测试文件(testbench),用于测试您的Verilog模块。测试文件中应包含初始化代码、时钟生成代码以及仿真结束的控制代码。编译Verilog代码使用iverilog编译器将Verilog代码和测试文件编译成VVP文件。编译命令如下:iverilog -o "test_tb.vvp" test_tb.v test.v运行仿真在命令行中运行生成的VVP文件,生成VCD波形文件:vvp test_tb.vvp查看波形使用GTKwave打开生成的VCD文件,查看仿真波形。您可以通过调整波形显示来分析仿真结果。注意事项确保iverilog和GTKwave已正确安装并配置好环境变量。在编写Verilog代码时,注意模块的输入输出定义和时序逻辑的正确性。在仿真过程中,可以通过调整测试文件中的参数来验证不同条件下的仿真结果。通过本教程,您将能够熟练使用VS Code、iverilog和GTKwave进行Verilog代码的仿真,为硬件设计提供强大的支持。【下载地址】用VSCodeiverilogGTKwave仿真Verilog分享用VS Code + iverilog + GTKwave仿真Verilog本资源文件提供了一个详细的教程,指导如何在VS Code中使用iverilog和GTKwave工具进行Verilog代码的仿真 项目地址: https://gitcode.com/Resource-Bundle-Collection/9dfab————————————————版权声明:本文为CSDN博主「邱蒙励」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。原文链接:https://blog.csdn.net/gitblog_06576/article/details/143385319 -

Vscode自动生成verilog例化 前言veirlog模块例化的时候,辣么多的信号端子,手动例化又慢又容易出错,葵花妈妈开课啦,孩子手残老犯错怎么办?当然是脚本一劳永逸,妈妈再也不担心手残党。流程(1)在vscode中安装如下插件。(2)在电脑中安装python3以上的环境。下载地址:https://www.python.org/downloads/release/python-373/安装记得一定要勾选添加路径,记得管理员安装。重启你的电脑。在cmd窗口输入python即可验证是否安装成功!(3)安装chardet。为确保插件可用,这个需要安装。参考链接:https://blog.csdn.net/sinat_28631741/article/details/80483064方式一 源码按照:第一步:下载压缩文件,例如: 'chardet-3.0.4.tar.gz'; 第二步:解压文件到python安装位置下的‘site-packages’目录下,例如:‘D:\python2.7\Lib\site-packages’; 第三步:打开终端命令窗口,进入解压的‘chardet’目录下,执行命令:python setup.py install (4)修改插件的原始py文件,觉得开发者的py有瑕疵,让帅气的同事重新整了个,把以下代码替换进原始py文件即可。在打开v文件的vscode下按ctrl+p,输入instance可出现下述界面。替换此py文件的代码即可。 #! /usr/bin/env python ''' vTbgenerator.py -- generate verilog module Testbench generated bench file like this: fifo_sc #( .DATA_WIDTH ( 8 ), .ADDR_WIDTH ( 8 ) ) u_fifo_sc ( .CLK ( CLK ), .RST_N ( RST_N ), .RD_EN ( RD_EN ), .WR_EN ( WR_EN ), .DIN ( DIN [DATA_WIDTH-1 :0] ), .DOUT ( DOUT [DATA_WIDTH-1 :0] ), .EMPTY ( EMPTY ), .FULL ( FULL ) ); Usage: python vTbgenerator.py ModuleFileName.v ''' import random import re import sys from queue import Queue import chardet def delComment(Text): """ removed comment """ single_line_comment = re.compile(r"//(.*)$", re.MULTILINE) multi_line_comment = re.compile(r"/\*(.*?)\*/", re.DOTALL) Text = multi_line_comment.sub('\n', Text) Text = single_line_comment.sub('\n', Text) return Text def delBlock(Text): """ removed task and function block """ Text = re.sub(r'\Wtask\W[\W\w]*?\Wendtask\W', '\n', Text) Text = re.sub(r'\Wfunction\W[\W\w]*?\Wendfunction\W', '\n', Text) return Text def findName(inText): """ find module name and port list""" p = re.search(r'([a-zA-Z_][a-zA-Z_0-9]*)\s*', inText) mo_Name = p.group(0).strip() return mo_Name def paraDeclare(inText, portArr): """ find parameter declare """ pat = r'\s' + portArr + r'\s[\w\W]*?[;,)]' ParaList = re.findall(pat, inText) return ParaList def portDeclare(inText, portArr): """find port declare, Syntax: input [ net_type ] [ signed ] [ range ] list_of_port_identifiers return list as : (port, [range]) """ port_definition = re.compile( r'\b' + portArr + r''' (\s+(wire|reg)\s+)* (\s*signed\s+)* (\s*\[.*?:.*?\]\s*)* (?P<port_list>.*?) (?= \binput\b | \boutput\b | \binout\b | ; | \) ) ''', re.VERBOSE | re.MULTILINE | re.DOTALL ) pList = port_definition.findall(inText) t = [] for ls in pList: if len(ls) >= 2: t = t + portDic(ls[-2:]) return t def portDic(port): """delet as : input a =c &d; return list as : (port, [range]) """ pRe = re.compile(r'(.*?)\s*=.*', re.DOTALL) pRange = port[0] pList = port[1].split(',') pList = [i.strip() for i in pList if i.strip() != ''] pList = [(pRe.sub(r'\1', p), pRange.strip()) for p in pList] return pList def formatPort(AllPortList, isPortRange=1): PortList = AllPortList str = '' if PortList != []: l1 = max([len(i[0]) for i in PortList])+2 l3 = max(18, l1) strList = [] str = ',\n'.join([' ' * 4 + '.' + i[0].ljust(l3) + '(' + (i[0]) + ')' for i in AllPortList]) strList = strList + [str] str = ',\n\n'.join(strList) return str def formatDeclare(PortList, portArr, initial=""): str = '' if PortList != []: str = '\n'.join([portArr.ljust(4) + ' '+(i[1]+min(len(i[1]), 1)*' ' + i[0]) + ';' for i in PortList]) return str def formatPara(ParaList): paraDec = '' paraDef = '' if ParaList != []: s = '\n'.join(ParaList) pat = r'([a-zA-Z_][a-zA-Z_0-9]*)\s*=\s*([\w\W]*?)\s*[;,)]' p = re.findall(pat, s) l1 = max([len(i[0]) for i in p]) l2 = max([len(i[1]) for i in p]) paraDec = '\n'.join(['parameter %s = %s;' % (i[0].ljust(l1 + 1), i[1].ljust(l2)) for i in p]) paraDef = '#(\n' + ',\n'.join([' .' + i[0].ljust(l1 + 1) + '( ' + i[1].ljust(l2)+' )' for i in p]) + ')\n' return paraDec, paraDef def portT(inText, ioPadAttr): x = {} count_list = [] order_list = [] for i in ioPadAttr: p = port_index_list(inText, i) for j in p: count_list.append(j) x[j] = i count_list = quick_sort(count_list, 0, len(count_list)-1) for c in count_list: order_list.append(x.get(c)) return order_list def quick_sort(myList, start, end): if start < end: i, j = start, end base = myList[i] while i < j: while (i < j) and (myList[j] >= base): j = j - 1 myList[i] = myList[j] while (i < j) and (myList[i] <= base): i = i + 1 myList[j] = myList[i] myList[i] = base quick_sort(myList, start, i - 1) quick_sort(myList, j + 1, end) return myList def formatPort_order(padAttr, orderList): for p in padAttr: q = Queue() for i in padAttr.get(p): q.put(i) padAttr[p] = q AllPortList = [] for o in orderList: AllPortList.append(padAttr.get(o).get()) return AllPortList def port_index_list(intext, text): l = [] t = intext index = t.find(text) while index > -1: t = t.replace(text, random_str(len(text)), 1) l.append(index) index = t.find(text) return l def random_str(size): s = '' for i in range(size): s += str(random.randint(0, 9)) return s def getPortMap(AllPortList, ioPadAttr): if len(AllPortList) != len(ioPadAttr): return p_map = {} for i in range(len(AllPortList)): p_map[ioPadAttr[i]] = AllPortList[i] return p_map def writeTestBench(input_file): """ write testbench to file """ with open(input_file, 'rb') as f: f_info = chardet.detect(f.read()) f_encoding = f_info['encoding'] with open(input_file, encoding=f_encoding) as inFile: inText = inFile.read() # removed comment,task,function inText = delComment(inText) inText = delBlock(inText) # moduel ... endmodule # moPos_begin = re.search(r'(\b|^)module\b', inText).end() moPos_end = re.search(r'\bendmodule\b', inText).start() inText = inText[moPos_begin:moPos_end] name = findName(inText) paraList = paraDeclare(inText, 'parameter') paraDec, paraDef = formatPara(paraList) ioPadAttr = ['input', 'output', 'inout'] orlder = portT(inText, ioPadAttr) input = portDeclare(inText, ioPadAttr[0]) output = portDeclare(inText, ioPadAttr[1]) inout = portDeclare(inText, ioPadAttr[2]) portList = formatPort(formatPort_order( getPortMap([input, output, inout], ioPadAttr), orlder)) input = formatDeclare(input, 'reg') output = formatDeclare(output, 'wire') inout = formatDeclare(inout, 'wire') # write Instance # module_parameter_port_list if(paraDec != ''): print("// %s Parameters\n%s\n" % (name, paraDec)) # list_of_port_declarations #print("// %s Inputs\n%s\n" % (name, input)) #print("// %s Outputs\n%s\n" % (name, output)) #if(inout != ''): # print("// %s Bidirs\n%s\n" % (name, inout)) print("\n") # UUT print("%s %s inst_%s (\n%s\n);" % (name, paraDef, name, portList)) if __name__ == '__main__': writeTestBench(sys.argv[1]) (5)享受一下吧。比如我们有如下代码:crtl+p,输入instance,按回车即可。 复制粘贴大发好。以上。转载于:https://www.cnblogs.com/kingstacker/p/9944259.html

Vscode自动生成verilog例化 前言veirlog模块例化的时候,辣么多的信号端子,手动例化又慢又容易出错,葵花妈妈开课啦,孩子手残老犯错怎么办?当然是脚本一劳永逸,妈妈再也不担心手残党。流程(1)在vscode中安装如下插件。(2)在电脑中安装python3以上的环境。下载地址:https://www.python.org/downloads/release/python-373/安装记得一定要勾选添加路径,记得管理员安装。重启你的电脑。在cmd窗口输入python即可验证是否安装成功!(3)安装chardet。为确保插件可用,这个需要安装。参考链接:https://blog.csdn.net/sinat_28631741/article/details/80483064方式一 源码按照:第一步:下载压缩文件,例如: 'chardet-3.0.4.tar.gz'; 第二步:解压文件到python安装位置下的‘site-packages’目录下,例如:‘D:\python2.7\Lib\site-packages’; 第三步:打开终端命令窗口,进入解压的‘chardet’目录下,执行命令:python setup.py install (4)修改插件的原始py文件,觉得开发者的py有瑕疵,让帅气的同事重新整了个,把以下代码替换进原始py文件即可。在打开v文件的vscode下按ctrl+p,输入instance可出现下述界面。替换此py文件的代码即可。 #! /usr/bin/env python ''' vTbgenerator.py -- generate verilog module Testbench generated bench file like this: fifo_sc #( .DATA_WIDTH ( 8 ), .ADDR_WIDTH ( 8 ) ) u_fifo_sc ( .CLK ( CLK ), .RST_N ( RST_N ), .RD_EN ( RD_EN ), .WR_EN ( WR_EN ), .DIN ( DIN [DATA_WIDTH-1 :0] ), .DOUT ( DOUT [DATA_WIDTH-1 :0] ), .EMPTY ( EMPTY ), .FULL ( FULL ) ); Usage: python vTbgenerator.py ModuleFileName.v ''' import random import re import sys from queue import Queue import chardet def delComment(Text): """ removed comment """ single_line_comment = re.compile(r"//(.*)$", re.MULTILINE) multi_line_comment = re.compile(r"/\*(.*?)\*/", re.DOTALL) Text = multi_line_comment.sub('\n', Text) Text = single_line_comment.sub('\n', Text) return Text def delBlock(Text): """ removed task and function block """ Text = re.sub(r'\Wtask\W[\W\w]*?\Wendtask\W', '\n', Text) Text = re.sub(r'\Wfunction\W[\W\w]*?\Wendfunction\W', '\n', Text) return Text def findName(inText): """ find module name and port list""" p = re.search(r'([a-zA-Z_][a-zA-Z_0-9]*)\s*', inText) mo_Name = p.group(0).strip() return mo_Name def paraDeclare(inText, portArr): """ find parameter declare """ pat = r'\s' + portArr + r'\s[\w\W]*?[;,)]' ParaList = re.findall(pat, inText) return ParaList def portDeclare(inText, portArr): """find port declare, Syntax: input [ net_type ] [ signed ] [ range ] list_of_port_identifiers return list as : (port, [range]) """ port_definition = re.compile( r'\b' + portArr + r''' (\s+(wire|reg)\s+)* (\s*signed\s+)* (\s*\[.*?:.*?\]\s*)* (?P<port_list>.*?) (?= \binput\b | \boutput\b | \binout\b | ; | \) ) ''', re.VERBOSE | re.MULTILINE | re.DOTALL ) pList = port_definition.findall(inText) t = [] for ls in pList: if len(ls) >= 2: t = t + portDic(ls[-2:]) return t def portDic(port): """delet as : input a =c &d; return list as : (port, [range]) """ pRe = re.compile(r'(.*?)\s*=.*', re.DOTALL) pRange = port[0] pList = port[1].split(',') pList = [i.strip() for i in pList if i.strip() != ''] pList = [(pRe.sub(r'\1', p), pRange.strip()) for p in pList] return pList def formatPort(AllPortList, isPortRange=1): PortList = AllPortList str = '' if PortList != []: l1 = max([len(i[0]) for i in PortList])+2 l3 = max(18, l1) strList = [] str = ',\n'.join([' ' * 4 + '.' + i[0].ljust(l3) + '(' + (i[0]) + ')' for i in AllPortList]) strList = strList + [str] str = ',\n\n'.join(strList) return str def formatDeclare(PortList, portArr, initial=""): str = '' if PortList != []: str = '\n'.join([portArr.ljust(4) + ' '+(i[1]+min(len(i[1]), 1)*' ' + i[0]) + ';' for i in PortList]) return str def formatPara(ParaList): paraDec = '' paraDef = '' if ParaList != []: s = '\n'.join(ParaList) pat = r'([a-zA-Z_][a-zA-Z_0-9]*)\s*=\s*([\w\W]*?)\s*[;,)]' p = re.findall(pat, s) l1 = max([len(i[0]) for i in p]) l2 = max([len(i[1]) for i in p]) paraDec = '\n'.join(['parameter %s = %s;' % (i[0].ljust(l1 + 1), i[1].ljust(l2)) for i in p]) paraDef = '#(\n' + ',\n'.join([' .' + i[0].ljust(l1 + 1) + '( ' + i[1].ljust(l2)+' )' for i in p]) + ')\n' return paraDec, paraDef def portT(inText, ioPadAttr): x = {} count_list = [] order_list = [] for i in ioPadAttr: p = port_index_list(inText, i) for j in p: count_list.append(j) x[j] = i count_list = quick_sort(count_list, 0, len(count_list)-1) for c in count_list: order_list.append(x.get(c)) return order_list def quick_sort(myList, start, end): if start < end: i, j = start, end base = myList[i] while i < j: while (i < j) and (myList[j] >= base): j = j - 1 myList[i] = myList[j] while (i < j) and (myList[i] <= base): i = i + 1 myList[j] = myList[i] myList[i] = base quick_sort(myList, start, i - 1) quick_sort(myList, j + 1, end) return myList def formatPort_order(padAttr, orderList): for p in padAttr: q = Queue() for i in padAttr.get(p): q.put(i) padAttr[p] = q AllPortList = [] for o in orderList: AllPortList.append(padAttr.get(o).get()) return AllPortList def port_index_list(intext, text): l = [] t = intext index = t.find(text) while index > -1: t = t.replace(text, random_str(len(text)), 1) l.append(index) index = t.find(text) return l def random_str(size): s = '' for i in range(size): s += str(random.randint(0, 9)) return s def getPortMap(AllPortList, ioPadAttr): if len(AllPortList) != len(ioPadAttr): return p_map = {} for i in range(len(AllPortList)): p_map[ioPadAttr[i]] = AllPortList[i] return p_map def writeTestBench(input_file): """ write testbench to file """ with open(input_file, 'rb') as f: f_info = chardet.detect(f.read()) f_encoding = f_info['encoding'] with open(input_file, encoding=f_encoding) as inFile: inText = inFile.read() # removed comment,task,function inText = delComment(inText) inText = delBlock(inText) # moduel ... endmodule # moPos_begin = re.search(r'(\b|^)module\b', inText).end() moPos_end = re.search(r'\bendmodule\b', inText).start() inText = inText[moPos_begin:moPos_end] name = findName(inText) paraList = paraDeclare(inText, 'parameter') paraDec, paraDef = formatPara(paraList) ioPadAttr = ['input', 'output', 'inout'] orlder = portT(inText, ioPadAttr) input = portDeclare(inText, ioPadAttr[0]) output = portDeclare(inText, ioPadAttr[1]) inout = portDeclare(inText, ioPadAttr[2]) portList = formatPort(formatPort_order( getPortMap([input, output, inout], ioPadAttr), orlder)) input = formatDeclare(input, 'reg') output = formatDeclare(output, 'wire') inout = formatDeclare(inout, 'wire') # write Instance # module_parameter_port_list if(paraDec != ''): print("// %s Parameters\n%s\n" % (name, paraDec)) # list_of_port_declarations #print("// %s Inputs\n%s\n" % (name, input)) #print("// %s Outputs\n%s\n" % (name, output)) #if(inout != ''): # print("// %s Bidirs\n%s\n" % (name, inout)) print("\n") # UUT print("%s %s inst_%s (\n%s\n);" % (name, paraDef, name, portList)) if __name__ == '__main__': writeTestBench(sys.argv[1]) (5)享受一下吧。比如我们有如下代码:crtl+p,输入instance,按回车即可。 复制粘贴大发好。以上。转载于:https://www.cnblogs.com/kingstacker/p/9944259.html -

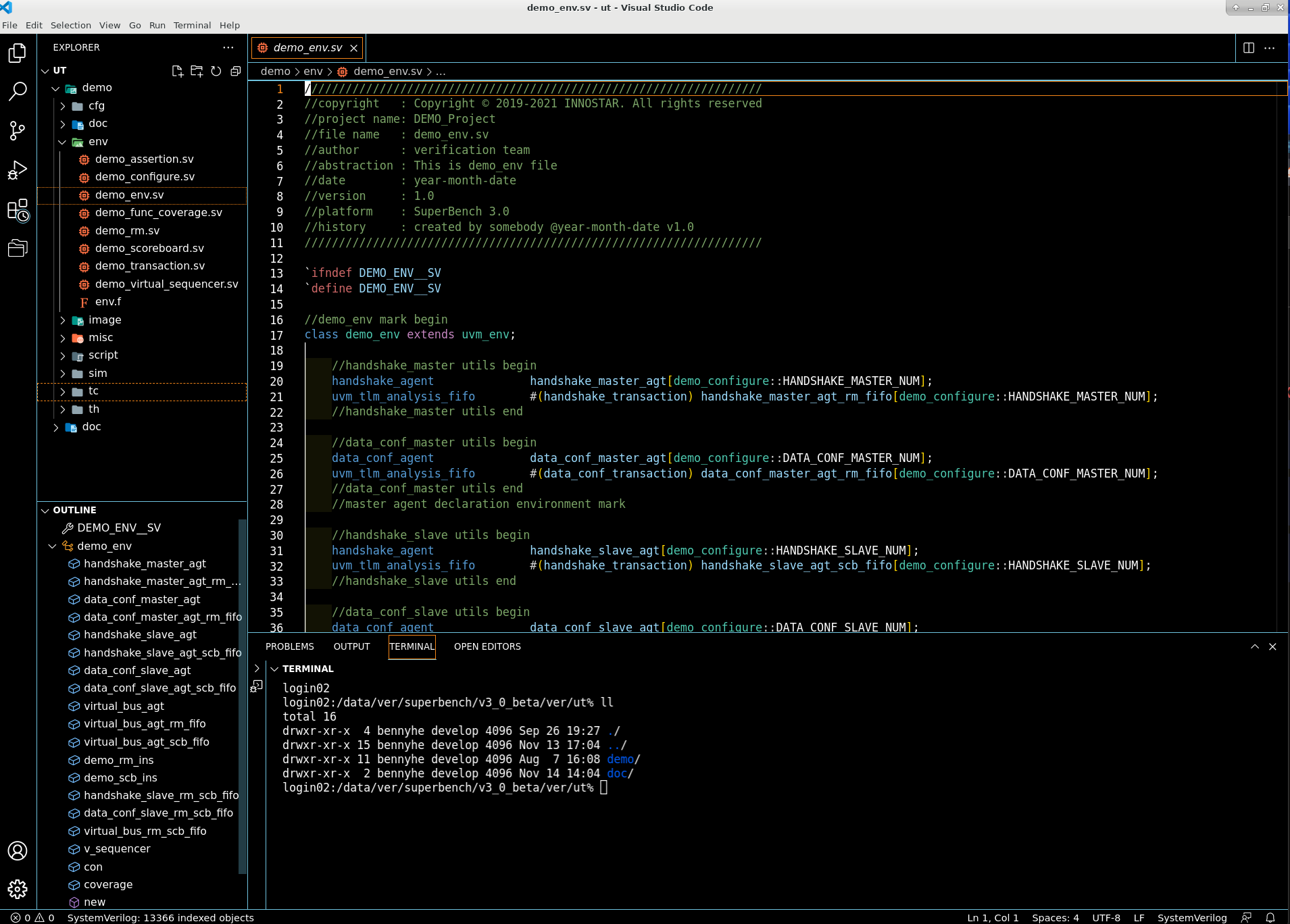

gvim+tmux 和vscode+neovim 的ide 模式 vscode 界面安装的插件:vscode+neovim 设置参考这篇文档:http://bennyhe.cn/index.php/archives/327/gvim 的界面:常用功能都有,文件浏览、语法高亮、彩虹括号、括号自动补齐、输入关键词提示,ctag 函数跳转、文档状态、多terminal(tmux)集成等等常用功能。terminal界面采用tmux,配合clipper 工具可以和gvim 文本窗口互相粘贴,可以分页多个terminal。gvim 按照的插件~/.vim/ 下文件夹结构~/.vim/ 下文件(插件)acp.vim auto-pairs.vim grep.vim mark.vim NERD_tree.vim scala.vim Tabular.vim verilog_systemverilog.vim vtreeexplorer.vimairline.vim ctrlp.vim marksbrowser.vim matchit.vim rainbow_parentheses.vim showmarks.vim taglist.vim visual-increment.vim~/.vimrc 文件如下:if v:version >= 900 set scroll=1 let g:airline_scroll_size = 1 " 覆盖插件默认值 endif set number syntax on set showmode set showcmd set hlsearch set autoindent set smartindent set cindent set ts=4 set softtabstop=4 set shiftwidth=4 set noexpandtab set tabstop=4 set cursorline set cursorcolumn set lines=35 columns=100 set ruler set showmatch set wrap noremap <C-S-A> gggH<C-O>G inoremap <C-S-A> <C-O>gg<C-O>gH<C-O>G cnoremap <C-S-A> <C-C>gggH<C-O>G onoremap <C-S-A> <C-C>gggH<C-O>G snoremap <C-S-A> <C-C>gggH<C-O>G xnoremap <C-S-A> <C-C>ggVG noremap <C-S> :update<CR> vnoremap <C-S> <C-C>:update<CR> inoremap <C-S> <Esc>:update<CR>gi if has("clipboard") " CTRL-X and SHIFT-Del are Cut vnoremap <C-A-X> "+x vnoremap <S-Del> "+x " CTRL-C and CTRL-Insert are Copy vnoremap <C-A-C> "+y vnoremap <C-Insert> "+y " CTRL-V and SHIFT-Insert are Paste map <C-A-V> "+gP map <S-Insert> "+gP cmap <C-A-V> <C-R>+ cmap <S-Insert> <C-R>+ endif "source $VIMRUNTIME/mswin.vim behave mswin set guifont=Monospace\ 14 set linespace=4 colorscheme evening "unmap <C-V> "unmap <C-A> "unmap <C-C> "unmap <C-X> " copy paste map <C-Insert> "+y map <S-Insert> "+gP "Mouse could be controled when INSERT model set mouse=a set selection=exclusive set selectmode=mouse,key "============================= " showmarks setting "============================= " Enable ShowMarks let showmarks_enable = 1 " Show which marks let showmarks_include = "abcdefghijklmnopqrstuvwxyzABCDEFGHIJKLMNOPQRSTUVWXYZ" " Ignore help, quickfix, non-modifiable buffers let showmarks_ignore_type = "hqm" " Hilight lower & upper marks let showmarks_hlline_lower = 1 let showmarks_hlline_upper = 1 hi ShowMarksHLl ctermbg=Yellow ctermfg=Black guibg=#FFDB72 guifg=Black hi ShowMarksHLu ctermbg=Magenta ctermfg=Black guibg=#FFB3FF guifg=Black "============================= " markbrowser setting "============================= nmap <silent> <leader>mk :MarksBrowser<cr> "Config for treeExplorer plugin let g:treeExplVertical=0 let g:treeExplDirSort=1 let g:treeExplWinSize=20 nmap vt :VSTreeExplore<cr> set autoread nmap <S-F> :call Verilog_format()<cr> function! Verilog_format() :w :silent execute '!~/.vim/tool/verible-verilog-format --column_limit=120 --indentation_spaces=4 --assignment_statement_alignment=align --named_port_alignment=align --port_declarations_alignment=align --module_net_variable_alignment=align --distribution_items_alignment=align --formal_parameters_indentation=indent --port_declarations_right_align_packed_dimensions=true --port_declarations_right_align_unpacked_dimensions=true --inplace=true --verify_convergence=true' expand('%:p') endfunction "ctrlp let g:ctrlp_map = '<c-p>' let g:ctrlp_cmd = 'CtrlP' "Grep hot key nnoremap <silent><C-F> :Grep -r<CR> "filetype, 'indent on' is necessary for smartindent filetype on filetype plugin on filetype indent on "header nmap <C-H> :call AddHeader()<cr> function! AddHeader() call append(0, '///////////////////////////////////////////////////////////////////') call append(1, '//copyright : Copyright © 2019-2023 INNOSTAR. All rights reserved') call append(2, '//project name: demo') call append(3, '//file name : '.expand('%:t')) call append(4, '//author : bennyhe') call append(5, '//abstraction : ') call append(6, '//date : '.strftime('%Y-%m-%d %H:%M:%S')) call append(7, '//version : 2.0') call append(8, '//platform : SuperBench 2.0') call append(9, '//history : created by bennyhe @'.strftime('%Y-%m-%d %H:%M:%S').expand(' v2.0')) call append(10, '///////////////////////////////////////////////////////////////////') endfunction "function nmap <C-L> :call AddFunction()<cr> function! AddFunction() call append(line(".")-1, ' /*****************************************************************') call append(line(".")-1, ' *') call append(line(".")-1, ' *****************************************************************/') endfunction set tags=tags; set tags+=~/.vim/tags/tags; set tags+=~/.vim/tags/tags_uvm; set tags+=~/.vim/tags/tags_vip; set autochdir "config for tlist plugin let Tlist_Ctags_Cmd = '/usr/bin/ctags' let Tlist_Use_Right_Window=0 let Tlist_Max_Tag_Length=1 let g:Tlist_Compact_Format=1 "let g:Tlist_WinHeight=5 let g:Tlist_WinWidth=15 let g:Tlist_Use_Horiz_Window=0 let g:Tlist_Show_One_File=1 "let g:Tlist_Exit_OnlyWindow=1 nmap tl :Tlist<cr> "terminal noremap <F8> :close!<cr> noremap <S-M-p> :sp<cr> noremap <S-M-q> :vs<cr> "noremap <F3> :belowright term ++rows=5 d:\msys64\msys2_shell.cmd -msys -defterm -no-start <cr> noremap <F3> :belowright term ++rows=5 powershell ubuntu2204.exe<cr> noremap <F4> :belowright term ++rows=5 powershell<cr> let b:match_words='\<begin\>:\<end\>' let g:rbpt_colorpairs = [ \ ['brown', 'RoyalBlue3'], \ ['Darkblue', 'SeaGreen3'], \ ['darkgray', 'DarkOrchid3'], \ ['darkgreen', 'firebrick3'], \ ['darkcyan', 'RoyalBlue3'], \ ['darkred', 'SeaGreen3'], \ ['darkmagenta', 'DarkOrchid3'], \ ['brown', 'firebrick3'], \ ['gray', 'RoyalBlue3'], \ ['black', 'SeaGreen3'], \ ['darkmagenta', 'DarkOrchid3'], \ ['Darkblue', 'firebrick3'], \ ['darkgreen', 'RoyalBlue3'], \ ['darkcyan', 'SeaGreen3'], \ ['darkred', 'DarkOrchid3'], \ ['red', 'firebrick3'], \ ] let g:rbpt_max = 16 let g:rbpt_loadcmd_toggle = 0 ""update ctags nmap <F10> :call UpdateCtags()<CR> function! UpdateCtags() let curdir=getcwd() while !filereadable("./tags") cd .. if getcwd() == "/" break endif endwhile if filewritable("./tags") silent !ctags -R --file-scope=yes --languages=systemverilog --links=yes --fields=+iaS --extra=+q TlistUpdate endif execute ":cd " . curdir endfunction nmap <F11> :call UpdateCtags_vip()<CR> function! UpdateCtags_vip() silent !ctags -R --languages=systemverilog -f ~/.vim/tags/tags_vip /data/ver/powervip/v2_0/ endfunction "autocmd BufWritePost *.sv,*.svh,*.v call UpdateCtags() "auto exce "set lines=999 columns=999 augroup initial autocmd! "autocmd VimEnter * VSTreeExplore "autocmd VimEnter * bo terminal ++rows=5 autocmd VimEnter * wincmd k autocmd VimEnter * Tlist autocmd VimEnter * wincmd h autocmd VimEnter * sp autocmd VimEnter * VSTreeExplore autocmd VimEnter * wincmd l autocmd VimEnter * q autocmd VimEnter * wincmd l au VimEnter * RainbowParenthesesToggleAll au Syntax * RainbowParenthesesLoadRound au Syntax * RainbowParenthesesLoadSquare au Syntax * RainbowParenthesesLoadBraces augroup END ":autocmd GUIEnter * VSTreeExplore "let g:airline_powerline_fonts = 1 let g:airline_theme = 'dark' let g:airline#extensions#tabline#enabled = 1 let g:airline#extensions#tabline#show_splits = 1 let g:airline#extensions#tabline#buffer_nr_show = 0 let g:airline#extensions#tabline#buffer_idx_mode = 3 let g:airline#extensions#tabline#show_tab_nr = 1 let g:airline#extensions#tabline#tab_nr_type = 1 let g:airline#extensions#branch#format =2 let g:airline_left_sep='>' let g:airline_inactive_collapse=0 let g:airline#extensions#tabline#formatter = 'unique_tail' let g:airline#extensions#tabline#buffer_idx_format = { \ '0': '0', \ '1': '1', \ '2': '2', \ '3': '3', \ '4': '4', \ '5': '5', \ '6': '6', \ '7': '7', \ '8': '8', \ '9': '9', \ ' ': ' ' \} let mapleader = "\<space>" let g:mapleader = "\<space>" set foldenable set foldmethod=marker set foldlevel=99 "" 代码折叠自定义快捷键 <leader>zz let g:FoldMethod = 0 map <leader>zz :call ToggleFold()<cr> fun! ToggleFold() if g:FoldMethod == 0 exe "normal! zM" let g:FoldMethod = 1 else exe "normal! zR" let g:FoldMethod = 0 endif endfun "set nocompatible "autocmd! bufwritepost .vimrc source % nmap <tab> :bn<cr> nmap <S-Tab> :bp<CR> "nmap <leader>1 :b 1<CR> nmap <leader>1 <Plug>AirlineSelectTab1 "{{{ nmap <leader>2 <Plug>AirlineSelectTab2 nmap <leader>3 <Plug>AirlineSelectTab3 nmap <leader>4 <Plug>AirlineSelectTab4 nmap <leader>5 <Plug>AirlineSelectTab5 nmap <leader>6 <Plug>AirlineSelectTab6 nmap <leader>7 <Plug>AirlineSelectTab7 nmap <leader>8 <Plug>AirlineSelectTab8 nmap <leader>9 <Plug>AirlineSelectTab9 nmap <leader>10 <Plug>AirlineSelectTab10 nmap <leader>11 <Plug>AirlineSelectTab11 nmap <leader>12 <Plug>AirlineSelectTab12 nmap <leader>13 <Plug>AirlineSelectTab13 nmap <leader>14 <Plug>AirlineSelectTab14 nmap <leader>15 <Plug>AirlineSelectTab15 nmap <leader>16 <Plug>AirlineSelectTab16 nmap <leader>17 <Plug>AirlineSelectTab17 nmap <leader>18 <Plug>AirlineSelectTab18 nmap <leader>19 <Plug>AirlineSelectTab19 nmap <leader>20 <Plug>AirlineSelectTab20 nmap <leader>21 <Plug>AirlineSelectTab21 nmap <leader>22 <Plug>AirlineSelectTab22 nmap <leader>23 <Plug>AirlineSelectTab23 nmap <leader>24 <Plug>AirlineSelectTab24 nmap <leader>25 <Plug>AirlineSelectTab25 nmap <leader>26 <Plug>AirlineSelectTab26 nmap <leader>27 <Plug>AirlineSelectTab27 nmap <leader>28 <Plug>AirlineSelectTab28 nmap <leader>29 <Plug>AirlineSelectTab29 nmap <leader>30 <Plug>AirlineSelectTab30 nmap <leader>31 <Plug>AirlineSelectTab31 nmap <leader>32 <Plug>AirlineSelectTab32 nmap <leader>33 <Plug>AirlineSelectTab33 nmap <leader>34 <Plug>AirlineSelectTab34 nmap <leader>35 <Plug>AirlineSelectTab35 nmap <leader>36 <Plug>AirlineSelectTab36 nmap <leader>37 <Plug>AirlineSelectTab37 nmap <leader>38 <Plug>AirlineSelectTab38 nmap <leader>39 <Plug>AirlineSelectTab39 nmap <leader>40 <Plug>AirlineSelectTab40 nmap <leader>41 <Plug>AirlineSelectTab41 nmap <leader>42 <Plug>AirlineSelectTab42 nmap <leader>43 <Plug>AirlineSelectTab43 nmap <leader>44 <Plug>AirlineSelectTab44 nmap <leader>45 <Plug>AirlineSelectTab45 nmap <leader>46 <Plug>AirlineSelectTab46 nmap <leader>47 <Plug>AirlineSelectTab47 nmap <leader>48 <Plug>AirlineSelectTab48 nmap <leader>49 <Plug>AirlineSelectTab49 nmap <leader>50 <Plug>AirlineSelectTab50 nmap <leader>51 <Plug>AirlineSelectTab51 nmap <leader>52 <Plug>AirlineSelectTab52 nmap <leader>53 <Plug>AirlineSelectTab53 nmap <leader>54 <Plug>AirlineSelectTab54 nmap <leader>55 <Plug>AirlineSelectTab55 nmap <leader>56 <Plug>AirlineSelectTab56 nmap <leader>57 <Plug>AirlineSelectTab57 nmap <leader>58 <Plug>AirlineSelectTab58 nmap <leader>59 <Plug>AirlineSelectTab59 nmap <leader>60 <Plug>AirlineSelectTab60 nmap <leader>61 <Plug>AirlineSelectTab61 nmap <leader>62 <Plug>AirlineSelectTab62 nmap <leader>63 <Plug>AirlineSelectTab63 nmap <leader>64 <Plug>AirlineSelectTab64 nmap <leader>65 <Plug>AirlineSelectTab65 nmap <leader>66 <Plug>AirlineSelectTab66 nmap <leader>67 <Plug>AirlineSelectTab67 nmap <leader>68 <Plug>AirlineSelectTab68 nmap <leader>69 <Plug>AirlineSelectTab69 nmap <leader>70 <Plug>AirlineSelectTab70 nmap <leader>71 <Plug>AirlineSelectTab71 nmap <leader>72 <Plug>AirlineSelectTab72 nmap <leader>73 <Plug>AirlineSelectTab73 nmap <leader>74 <Plug>AirlineSelectTab74 nmap <leader>75 <Plug>AirlineSelectTab75 nmap <leader>76 <Plug>AirlineSelectTab76 nmap <leader>77 <Plug>AirlineSelectTab77 nmap <leader>78 <Plug>AirlineSelectTab78 nmap <leader>79 <Plug>AirlineSelectTab79 nmap <leader>80 <Plug>AirlineSelectTab80 nmap <leader>81 <Plug>AirlineSelectTab81 nmap <leader>82 <Plug>AirlineSelectTab82 nmap <leader>83 <Plug>AirlineSelectTab83 nmap <leader>84 <Plug>AirlineSelectTab84 nmap <leader>85 <Plug>AirlineSelectTab85 nmap <leader>86 <Plug>AirlineSelectTab86 nmap <leader>87 <Plug>AirlineSelectTab87 nmap <leader>88 <Plug>AirlineSelectTab88 nmap <leader>89 <Plug>AirlineSelectTab89 nmap <leader>90 <Plug>AirlineSelectTab90 nmap <leader>91 <Plug>AirlineSelectTab91 nmap <leader>92 <Plug>AirlineSelectTab92 nmap <leader>93 <Plug>AirlineSelectTab93 nmap <leader>94 <Plug>AirlineSelectTab94 nmap <leader>95 <Plug>AirlineSelectTab95 nmap <leader>96 <Plug>AirlineSelectTab96 nmap <leader>97 <Plug>AirlineSelectTab97 nmap <leader>98 <Plug>AirlineSelectTab98 nmap <leader>99 <Plug>AirlineSelectTab99 "nmap <leader>- <Plug>AirlineSelectPrevTab "nmap <leader>+ <Plug>AirlineSelectNextTab "}}}

gvim+tmux 和vscode+neovim 的ide 模式 vscode 界面安装的插件:vscode+neovim 设置参考这篇文档:http://bennyhe.cn/index.php/archives/327/gvim 的界面:常用功能都有,文件浏览、语法高亮、彩虹括号、括号自动补齐、输入关键词提示,ctag 函数跳转、文档状态、多terminal(tmux)集成等等常用功能。terminal界面采用tmux,配合clipper 工具可以和gvim 文本窗口互相粘贴,可以分页多个terminal。gvim 按照的插件~/.vim/ 下文件夹结构~/.vim/ 下文件(插件)acp.vim auto-pairs.vim grep.vim mark.vim NERD_tree.vim scala.vim Tabular.vim verilog_systemverilog.vim vtreeexplorer.vimairline.vim ctrlp.vim marksbrowser.vim matchit.vim rainbow_parentheses.vim showmarks.vim taglist.vim visual-increment.vim~/.vimrc 文件如下:if v:version >= 900 set scroll=1 let g:airline_scroll_size = 1 " 覆盖插件默认值 endif set number syntax on set showmode set showcmd set hlsearch set autoindent set smartindent set cindent set ts=4 set softtabstop=4 set shiftwidth=4 set noexpandtab set tabstop=4 set cursorline set cursorcolumn set lines=35 columns=100 set ruler set showmatch set wrap noremap <C-S-A> gggH<C-O>G inoremap <C-S-A> <C-O>gg<C-O>gH<C-O>G cnoremap <C-S-A> <C-C>gggH<C-O>G onoremap <C-S-A> <C-C>gggH<C-O>G snoremap <C-S-A> <C-C>gggH<C-O>G xnoremap <C-S-A> <C-C>ggVG noremap <C-S> :update<CR> vnoremap <C-S> <C-C>:update<CR> inoremap <C-S> <Esc>:update<CR>gi if has("clipboard") " CTRL-X and SHIFT-Del are Cut vnoremap <C-A-X> "+x vnoremap <S-Del> "+x " CTRL-C and CTRL-Insert are Copy vnoremap <C-A-C> "+y vnoremap <C-Insert> "+y " CTRL-V and SHIFT-Insert are Paste map <C-A-V> "+gP map <S-Insert> "+gP cmap <C-A-V> <C-R>+ cmap <S-Insert> <C-R>+ endif "source $VIMRUNTIME/mswin.vim behave mswin set guifont=Monospace\ 14 set linespace=4 colorscheme evening "unmap <C-V> "unmap <C-A> "unmap <C-C> "unmap <C-X> " copy paste map <C-Insert> "+y map <S-Insert> "+gP "Mouse could be controled when INSERT model set mouse=a set selection=exclusive set selectmode=mouse,key "============================= " showmarks setting "============================= " Enable ShowMarks let showmarks_enable = 1 " Show which marks let showmarks_include = "abcdefghijklmnopqrstuvwxyzABCDEFGHIJKLMNOPQRSTUVWXYZ" " Ignore help, quickfix, non-modifiable buffers let showmarks_ignore_type = "hqm" " Hilight lower & upper marks let showmarks_hlline_lower = 1 let showmarks_hlline_upper = 1 hi ShowMarksHLl ctermbg=Yellow ctermfg=Black guibg=#FFDB72 guifg=Black hi ShowMarksHLu ctermbg=Magenta ctermfg=Black guibg=#FFB3FF guifg=Black "============================= " markbrowser setting "============================= nmap <silent> <leader>mk :MarksBrowser<cr> "Config for treeExplorer plugin let g:treeExplVertical=0 let g:treeExplDirSort=1 let g:treeExplWinSize=20 nmap vt :VSTreeExplore<cr> set autoread nmap <S-F> :call Verilog_format()<cr> function! Verilog_format() :w :silent execute '!~/.vim/tool/verible-verilog-format --column_limit=120 --indentation_spaces=4 --assignment_statement_alignment=align --named_port_alignment=align --port_declarations_alignment=align --module_net_variable_alignment=align --distribution_items_alignment=align --formal_parameters_indentation=indent --port_declarations_right_align_packed_dimensions=true --port_declarations_right_align_unpacked_dimensions=true --inplace=true --verify_convergence=true' expand('%:p') endfunction "ctrlp let g:ctrlp_map = '<c-p>' let g:ctrlp_cmd = 'CtrlP' "Grep hot key nnoremap <silent><C-F> :Grep -r<CR> "filetype, 'indent on' is necessary for smartindent filetype on filetype plugin on filetype indent on "header nmap <C-H> :call AddHeader()<cr> function! AddHeader() call append(0, '///////////////////////////////////////////////////////////////////') call append(1, '//copyright : Copyright © 2019-2023 INNOSTAR. All rights reserved') call append(2, '//project name: demo') call append(3, '//file name : '.expand('%:t')) call append(4, '//author : bennyhe') call append(5, '//abstraction : ') call append(6, '//date : '.strftime('%Y-%m-%d %H:%M:%S')) call append(7, '//version : 2.0') call append(8, '//platform : SuperBench 2.0') call append(9, '//history : created by bennyhe @'.strftime('%Y-%m-%d %H:%M:%S').expand(' v2.0')) call append(10, '///////////////////////////////////////////////////////////////////') endfunction "function nmap <C-L> :call AddFunction()<cr> function! AddFunction() call append(line(".")-1, ' /*****************************************************************') call append(line(".")-1, ' *') call append(line(".")-1, ' *****************************************************************/') endfunction set tags=tags; set tags+=~/.vim/tags/tags; set tags+=~/.vim/tags/tags_uvm; set tags+=~/.vim/tags/tags_vip; set autochdir "config for tlist plugin let Tlist_Ctags_Cmd = '/usr/bin/ctags' let Tlist_Use_Right_Window=0 let Tlist_Max_Tag_Length=1 let g:Tlist_Compact_Format=1 "let g:Tlist_WinHeight=5 let g:Tlist_WinWidth=15 let g:Tlist_Use_Horiz_Window=0 let g:Tlist_Show_One_File=1 "let g:Tlist_Exit_OnlyWindow=1 nmap tl :Tlist<cr> "terminal noremap <F8> :close!<cr> noremap <S-M-p> :sp<cr> noremap <S-M-q> :vs<cr> "noremap <F3> :belowright term ++rows=5 d:\msys64\msys2_shell.cmd -msys -defterm -no-start <cr> noremap <F3> :belowright term ++rows=5 powershell ubuntu2204.exe<cr> noremap <F4> :belowright term ++rows=5 powershell<cr> let b:match_words='\<begin\>:\<end\>' let g:rbpt_colorpairs = [ \ ['brown', 'RoyalBlue3'], \ ['Darkblue', 'SeaGreen3'], \ ['darkgray', 'DarkOrchid3'], \ ['darkgreen', 'firebrick3'], \ ['darkcyan', 'RoyalBlue3'], \ ['darkred', 'SeaGreen3'], \ ['darkmagenta', 'DarkOrchid3'], \ ['brown', 'firebrick3'], \ ['gray', 'RoyalBlue3'], \ ['black', 'SeaGreen3'], \ ['darkmagenta', 'DarkOrchid3'], \ ['Darkblue', 'firebrick3'], \ ['darkgreen', 'RoyalBlue3'], \ ['darkcyan', 'SeaGreen3'], \ ['darkred', 'DarkOrchid3'], \ ['red', 'firebrick3'], \ ] let g:rbpt_max = 16 let g:rbpt_loadcmd_toggle = 0 ""update ctags nmap <F10> :call UpdateCtags()<CR> function! UpdateCtags() let curdir=getcwd() while !filereadable("./tags") cd .. if getcwd() == "/" break endif endwhile if filewritable("./tags") silent !ctags -R --file-scope=yes --languages=systemverilog --links=yes --fields=+iaS --extra=+q TlistUpdate endif execute ":cd " . curdir endfunction nmap <F11> :call UpdateCtags_vip()<CR> function! UpdateCtags_vip() silent !ctags -R --languages=systemverilog -f ~/.vim/tags/tags_vip /data/ver/powervip/v2_0/ endfunction "autocmd BufWritePost *.sv,*.svh,*.v call UpdateCtags() "auto exce "set lines=999 columns=999 augroup initial autocmd! "autocmd VimEnter * VSTreeExplore "autocmd VimEnter * bo terminal ++rows=5 autocmd VimEnter * wincmd k autocmd VimEnter * Tlist autocmd VimEnter * wincmd h autocmd VimEnter * sp autocmd VimEnter * VSTreeExplore autocmd VimEnter * wincmd l autocmd VimEnter * q autocmd VimEnter * wincmd l au VimEnter * RainbowParenthesesToggleAll au Syntax * RainbowParenthesesLoadRound au Syntax * RainbowParenthesesLoadSquare au Syntax * RainbowParenthesesLoadBraces augroup END ":autocmd GUIEnter * VSTreeExplore "let g:airline_powerline_fonts = 1 let g:airline_theme = 'dark' let g:airline#extensions#tabline#enabled = 1 let g:airline#extensions#tabline#show_splits = 1 let g:airline#extensions#tabline#buffer_nr_show = 0 let g:airline#extensions#tabline#buffer_idx_mode = 3 let g:airline#extensions#tabline#show_tab_nr = 1 let g:airline#extensions#tabline#tab_nr_type = 1 let g:airline#extensions#branch#format =2 let g:airline_left_sep='>' let g:airline_inactive_collapse=0 let g:airline#extensions#tabline#formatter = 'unique_tail' let g:airline#extensions#tabline#buffer_idx_format = { \ '0': '0', \ '1': '1', \ '2': '2', \ '3': '3', \ '4': '4', \ '5': '5', \ '6': '6', \ '7': '7', \ '8': '8', \ '9': '9', \ ' ': ' ' \} let mapleader = "\<space>" let g:mapleader = "\<space>" set foldenable set foldmethod=marker set foldlevel=99 "" 代码折叠自定义快捷键 <leader>zz let g:FoldMethod = 0 map <leader>zz :call ToggleFold()<cr> fun! ToggleFold() if g:FoldMethod == 0 exe "normal! zM" let g:FoldMethod = 1 else exe "normal! zR" let g:FoldMethod = 0 endif endfun "set nocompatible "autocmd! bufwritepost .vimrc source % nmap <tab> :bn<cr> nmap <S-Tab> :bp<CR> "nmap <leader>1 :b 1<CR> nmap <leader>1 <Plug>AirlineSelectTab1 "{{{ nmap <leader>2 <Plug>AirlineSelectTab2 nmap <leader>3 <Plug>AirlineSelectTab3 nmap <leader>4 <Plug>AirlineSelectTab4 nmap <leader>5 <Plug>AirlineSelectTab5 nmap <leader>6 <Plug>AirlineSelectTab6 nmap <leader>7 <Plug>AirlineSelectTab7 nmap <leader>8 <Plug>AirlineSelectTab8 nmap <leader>9 <Plug>AirlineSelectTab9 nmap <leader>10 <Plug>AirlineSelectTab10 nmap <leader>11 <Plug>AirlineSelectTab11 nmap <leader>12 <Plug>AirlineSelectTab12 nmap <leader>13 <Plug>AirlineSelectTab13 nmap <leader>14 <Plug>AirlineSelectTab14 nmap <leader>15 <Plug>AirlineSelectTab15 nmap <leader>16 <Plug>AirlineSelectTab16 nmap <leader>17 <Plug>AirlineSelectTab17 nmap <leader>18 <Plug>AirlineSelectTab18 nmap <leader>19 <Plug>AirlineSelectTab19 nmap <leader>20 <Plug>AirlineSelectTab20 nmap <leader>21 <Plug>AirlineSelectTab21 nmap <leader>22 <Plug>AirlineSelectTab22 nmap <leader>23 <Plug>AirlineSelectTab23 nmap <leader>24 <Plug>AirlineSelectTab24 nmap <leader>25 <Plug>AirlineSelectTab25 nmap <leader>26 <Plug>AirlineSelectTab26 nmap <leader>27 <Plug>AirlineSelectTab27 nmap <leader>28 <Plug>AirlineSelectTab28 nmap <leader>29 <Plug>AirlineSelectTab29 nmap <leader>30 <Plug>AirlineSelectTab30 nmap <leader>31 <Plug>AirlineSelectTab31 nmap <leader>32 <Plug>AirlineSelectTab32 nmap <leader>33 <Plug>AirlineSelectTab33 nmap <leader>34 <Plug>AirlineSelectTab34 nmap <leader>35 <Plug>AirlineSelectTab35 nmap <leader>36 <Plug>AirlineSelectTab36 nmap <leader>37 <Plug>AirlineSelectTab37 nmap <leader>38 <Plug>AirlineSelectTab38 nmap <leader>39 <Plug>AirlineSelectTab39 nmap <leader>40 <Plug>AirlineSelectTab40 nmap <leader>41 <Plug>AirlineSelectTab41 nmap <leader>42 <Plug>AirlineSelectTab42 nmap <leader>43 <Plug>AirlineSelectTab43 nmap <leader>44 <Plug>AirlineSelectTab44 nmap <leader>45 <Plug>AirlineSelectTab45 nmap <leader>46 <Plug>AirlineSelectTab46 nmap <leader>47 <Plug>AirlineSelectTab47 nmap <leader>48 <Plug>AirlineSelectTab48 nmap <leader>49 <Plug>AirlineSelectTab49 nmap <leader>50 <Plug>AirlineSelectTab50 nmap <leader>51 <Plug>AirlineSelectTab51 nmap <leader>52 <Plug>AirlineSelectTab52 nmap <leader>53 <Plug>AirlineSelectTab53 nmap <leader>54 <Plug>AirlineSelectTab54 nmap <leader>55 <Plug>AirlineSelectTab55 nmap <leader>56 <Plug>AirlineSelectTab56 nmap <leader>57 <Plug>AirlineSelectTab57 nmap <leader>58 <Plug>AirlineSelectTab58 nmap <leader>59 <Plug>AirlineSelectTab59 nmap <leader>60 <Plug>AirlineSelectTab60 nmap <leader>61 <Plug>AirlineSelectTab61 nmap <leader>62 <Plug>AirlineSelectTab62 nmap <leader>63 <Plug>AirlineSelectTab63 nmap <leader>64 <Plug>AirlineSelectTab64 nmap <leader>65 <Plug>AirlineSelectTab65 nmap <leader>66 <Plug>AirlineSelectTab66 nmap <leader>67 <Plug>AirlineSelectTab67 nmap <leader>68 <Plug>AirlineSelectTab68 nmap <leader>69 <Plug>AirlineSelectTab69 nmap <leader>70 <Plug>AirlineSelectTab70 nmap <leader>71 <Plug>AirlineSelectTab71 nmap <leader>72 <Plug>AirlineSelectTab72 nmap <leader>73 <Plug>AirlineSelectTab73 nmap <leader>74 <Plug>AirlineSelectTab74 nmap <leader>75 <Plug>AirlineSelectTab75 nmap <leader>76 <Plug>AirlineSelectTab76 nmap <leader>77 <Plug>AirlineSelectTab77 nmap <leader>78 <Plug>AirlineSelectTab78 nmap <leader>79 <Plug>AirlineSelectTab79 nmap <leader>80 <Plug>AirlineSelectTab80 nmap <leader>81 <Plug>AirlineSelectTab81 nmap <leader>82 <Plug>AirlineSelectTab82 nmap <leader>83 <Plug>AirlineSelectTab83 nmap <leader>84 <Plug>AirlineSelectTab84 nmap <leader>85 <Plug>AirlineSelectTab85 nmap <leader>86 <Plug>AirlineSelectTab86 nmap <leader>87 <Plug>AirlineSelectTab87 nmap <leader>88 <Plug>AirlineSelectTab88 nmap <leader>89 <Plug>AirlineSelectTab89 nmap <leader>90 <Plug>AirlineSelectTab90 nmap <leader>91 <Plug>AirlineSelectTab91 nmap <leader>92 <Plug>AirlineSelectTab92 nmap <leader>93 <Plug>AirlineSelectTab93 nmap <leader>94 <Plug>AirlineSelectTab94 nmap <leader>95 <Plug>AirlineSelectTab95 nmap <leader>96 <Plug>AirlineSelectTab96 nmap <leader>97 <Plug>AirlineSelectTab97 nmap <leader>98 <Plug>AirlineSelectTab98 nmap <leader>99 <Plug>AirlineSelectTab99 "nmap <leader>- <Plug>AirlineSelectPrevTab "nmap <leader>+ <Plug>AirlineSelectNextTab "}}} -

VSCode搭建Python开发环境 文章所需的部署环境为Windows10 64位.这篇文章将演示如何搭建一个VSCode编写Python代码的环境。第一步. 安装Python环境(如果已经安装过的可以略过)下载地址:https://www.python.org/downloads/www.python.org/downloads/目前Python最新版本是3.8.5, 但是该版本还处于BUGFIX阶段,所以我们使用稳定的最新版本3.7.8。python2.7 已经在2020-01-01停止维护,如果还在使用Python2的要及时更新哦点击Download后,我们在新页面选择64位安装程序如果下载速度慢的话可以使用代理下载下来打开后,根据图示安装下一步.Documentation:python文档,建议勾上.pip: python安装其他库的工具,必勾.tcl/tk and IDLE: 安装tkinter库和IDLE开发环境, IDLE就是个编辑器,tkinter以后也可以装,这里不推荐勾选.Python test suite:Python标准库测试测试套装,不是必须下一步安装路径自行调整,其余按图示即可。安装成功测试是否有效,win+r 输入cmd 打开控制台,输入python -V,输出了安装的python版本即成功!如果没有输出或者出错,可能是安装时没有勾选添加python安装路径到环境变量,百度一下如何添加即可。VSCode配置Python开发环境接下来就是配置VSCode了,首先打开VSCode, 搜索插件Python并安装。或者直接打开某个.py文件,VSCode右下角将会自动提示你安装。安装完毕后,VSCode应该会出现这个提示需要你选择一个Python的解析器,点击Select Python Interpreter不出意外的话,你已经将Python路径添加到环境变量,于是VSCode可以自动识别到,图中即是你安装的Python解析器的位置了,选择即可。如果VSCode没有提示你选择,那你可以使用ctrl+shift+p, 输入Python Select Python Interpreter 即可。这一步做完后,VSCode可能还会出现这个提示这是VSCode需要你选择一个代码检查插件,你可以直接点击Install来安装pylint,也可以点击Select Linter选择其他的代码检查插件。这里我选择点击Select Linter。或者直接在setting 中输入interpret, 填写pythona安装后的路径VSCode的Python插件默认是使用pylint作为代码检查插件,我更习惯使用pycodestyle。选择后VSCode应该会提示你该插件未安装,点击Install安装即可。python会调用pip去安装,如下图所示即是安装成功了。黄字WARNING是提示pip版本可更新,无大碍。到这里,你已经可以使用VSCode编写python代码了,来试试看!右键可以点击出许多Python插件提供的功能,试试运行该python文件于终端。或者在终端输入 python hello.py 来运行hello.py文件。或者在python文件点击右键,选择“Run Python File in Terminal”成功输出( ̄︶ ̄*))。可以看到Python插件还提供了很多的功能, 比如选中函数后跳转到其实现。

VSCode搭建Python开发环境 文章所需的部署环境为Windows10 64位.这篇文章将演示如何搭建一个VSCode编写Python代码的环境。第一步. 安装Python环境(如果已经安装过的可以略过)下载地址:https://www.python.org/downloads/www.python.org/downloads/目前Python最新版本是3.8.5, 但是该版本还处于BUGFIX阶段,所以我们使用稳定的最新版本3.7.8。python2.7 已经在2020-01-01停止维护,如果还在使用Python2的要及时更新哦点击Download后,我们在新页面选择64位安装程序如果下载速度慢的话可以使用代理下载下来打开后,根据图示安装下一步.Documentation:python文档,建议勾上.pip: python安装其他库的工具,必勾.tcl/tk and IDLE: 安装tkinter库和IDLE开发环境, IDLE就是个编辑器,tkinter以后也可以装,这里不推荐勾选.Python test suite:Python标准库测试测试套装,不是必须下一步安装路径自行调整,其余按图示即可。安装成功测试是否有效,win+r 输入cmd 打开控制台,输入python -V,输出了安装的python版本即成功!如果没有输出或者出错,可能是安装时没有勾选添加python安装路径到环境变量,百度一下如何添加即可。VSCode配置Python开发环境接下来就是配置VSCode了,首先打开VSCode, 搜索插件Python并安装。或者直接打开某个.py文件,VSCode右下角将会自动提示你安装。安装完毕后,VSCode应该会出现这个提示需要你选择一个Python的解析器,点击Select Python Interpreter不出意外的话,你已经将Python路径添加到环境变量,于是VSCode可以自动识别到,图中即是你安装的Python解析器的位置了,选择即可。如果VSCode没有提示你选择,那你可以使用ctrl+shift+p, 输入Python Select Python Interpreter 即可。这一步做完后,VSCode可能还会出现这个提示这是VSCode需要你选择一个代码检查插件,你可以直接点击Install来安装pylint,也可以点击Select Linter选择其他的代码检查插件。这里我选择点击Select Linter。或者直接在setting 中输入interpret, 填写pythona安装后的路径VSCode的Python插件默认是使用pylint作为代码检查插件,我更习惯使用pycodestyle。选择后VSCode应该会提示你该插件未安装,点击Install安装即可。python会调用pip去安装,如下图所示即是安装成功了。黄字WARNING是提示pip版本可更新,无大碍。到这里,你已经可以使用VSCode编写python代码了,来试试看!右键可以点击出许多Python插件提供的功能,试试运行该python文件于终端。或者在终端输入 python hello.py 来运行hello.py文件。或者在python文件点击右键,选择“Run Python File in Terminal”成功输出( ̄︶ ̄*))。可以看到Python插件还提供了很多的功能, 比如选中函数后跳转到其实现。