搜索到

1

篇与

的结果

-

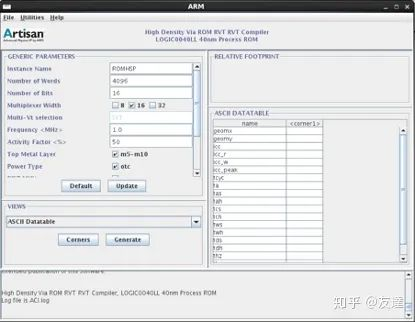

科普:Memory Compiler生成的Register file和SRAM有何区别? IP与S0C设计2021年09月03日04:01前两期,我们分别对OTP和MTP,RAM和ROM进行了比较。这一次,我们来谈谈Memory Compiler,以及通过它生成的Register file和SRAM。什么是Memory Compiler ?Memory Compiler,内存编译器。顾名思义,是用来生成不同容量memory的工具,输入参数,我们就可以得到生成的文件。生成的文件包括:前端设计verilog模型、逻辑综合的时序库、后端需要的电路网表和LEF/GDS版图文件、其他DFT验证相关的、datasheet手册等等。Memory Compiler由供应商提供,往往是不通用的,界面也不尽相同。同一个厂商的不同工艺下,Memory Compiler不同。相同工艺,不同厂商,Memory Compiler也不同。内存编译器通常是供应商的知识产权,其功能是根据客户的需求生成各种类型的memory。一般的Memory Compiler提供五个ram脚本(rf_sp,sram_sp,rf_tp,sram_dp,rom)。这意味着可以生成1 Port Register file、Single Port SRAM、2 Port Register file、Dual Port SRAM以及ROM。不同的厂商或许还拥有特殊工艺。一般来说,MC只生成常用的memory,特殊的往往需要定制或者组合。考虑到面积和性能,又可以划分为High Speed和High Density等等。图源知乎:SMIC 的Memory Compiler,由Artisan公司提供Memory Compiler使用介绍在使用Memory Compiler时,请务必确保你的RAM从头到位的规格与设定都相同,否则会造成一些不可避免的错误。首先在RTL代码阶段,要用到RAM就要用到verilog代码,此时不需要着急产生其他后阶段的必要数据,因为RTL代码阶段只需要行为级模型即可。当进入门级代码后,RAM compiler就要产生其他的相关数据了,同时要考虑RAM版图的位置与方向。由于重大的设计不会一蹴而就,所以有两个重点,第一个是每次使用RAM compiler时都一定要让它产生特性设置文档,避免忘记自己做过的设定。第二件事是对应的文件名要定义好,否则RAM的方向不同但是又用到了相同的文件名,就会把原始数据覆盖掉。RTL阶段在RTL阶段主要只是产生verilog行为级和设置文件。因为在RTL阶段不需要考虑RAM的位置信息。Memory Compiler提供多种选择,在这个阶段,选择生成RF或是SRAM,以及确定端口数量。如果容量比较大的话,相同设置下,单端口比双端口面积要小,速度也要快,功耗要低。综合与布局布线阶段为了避免重新启用Memory Compiler与以前设置有出入,所以最好一次性将Memory Compiler能够产生的相关数据一并输出。在这里,Memory Compiler还需要产生3种数据。 .LIB 该数据是RAM的时序信息文件 .VCLEF 布局布线工具需要使用的物理信息文件 .SPEC RAM的注释文件在布局布线前,需要考虑RAM的长与宽,估计它的位置与方向,尽量让功能想关的模块靠近一些。将产生的.LIB文件转换成.DB文件,就可以把Memory Compiler生成的RAM加入到代码中进行综合了。在综合工具的脚本中的serch_path下加入RAM的DB文件地址即可。以上为Memory Compiler大致的使用流程,不同的工具在细节上或许有所区别,但大体流程如此。苏州腾芯微电子的Memory Compiler界面接下来,我们来聊一聊,生成的memory——Register file和SRAM。Register file与SRAM的比较首先,厘清一下概念上的问题,Register file和很多的registers不是同一个概念。我们在IC设计里谈到register时,常常是指D触发器,而Register file是一种memory。那么,同为Memory Compiler生成,RF和SRAM有什么区别呢?在比较中,不同规格相比较显然不够客观,也不能让我们更清晰地认识到它们的差异。在比较前,我们需要先把端口的概念搞清楚: 1 port / single port:单端口,读写同端口,需要WE控制输入输出 2 port:双端口,读写分开,输入输出端口固定,可以不用WE控制 dual port:同样是双端口,但读写端口不固定,且都可读可写 RF 的端口示意图SRAM 的端口示意图所以我们应当把1P RF和SP SRAM,2P RF和DP SRAM比较,才有意义。1 Port Register file 和 Single Port SRAM同为单端口,从外部端口看,难以区分1P RF和SP SRAM的区别,但是我们可以从以下几个方面,来进行区分。首先我们以Memory Size:512*32的1P RF和SP SRAM为例。此为1P RF此为SP SRAM从datasheet直观上来看,SRAM比Register file多了OEN(输出使能)。除此之外,Register file和SRAM两者相比,SRAM的最大容量比RF要大。相同配置下,RF的面积更大,功耗更低。在mem比较小的情况下用RF划算,并且同样的mem,RF的长宽比会更小,方便后端floorplan。大容量的时候,SRAM的速度是有优势的。并且SRAM速度快,面积小。同样大小的RF,面积就很大了,速度也慢下来了。所以简单来说,小容量选RF,大容量选SRAM。2P Register file 和 Dual Port SRAM比起1P RF与SP SRAM的比较,2P RF与DP SRAM的差异较为直观。2P RF有一个输入数据总线,一个输出的数据总线。DP SRAM有两个数据输入总线,两个数据输出总线。换句话说,2P RF是一组信号,读写端口固定;而DP SRAM则有两组信号,读写不分开。且两组信号,每组都有自己的地址,输入数据总线,输出数据总线,时钟,读/写控制。这两组可以分别往存储单元写,或从存储单元读出。读可以一直读,写时数据可能存储单元数据更新,数据也可能输出端口。DP SRAM就好像2个SP SRAM共用存储单元。具体的应用,需要结合设计人员和项目自身的需求来选用。小容量,地址少的用RF。有两个外设要同时读写SRAM的,就要用DP SRAM。涉及到具体的选取,则需要由设计人员自己做判断了。以下为读写时序图:图源:数字IC自修室来自微信

科普:Memory Compiler生成的Register file和SRAM有何区别? IP与S0C设计2021年09月03日04:01前两期,我们分别对OTP和MTP,RAM和ROM进行了比较。这一次,我们来谈谈Memory Compiler,以及通过它生成的Register file和SRAM。什么是Memory Compiler ?Memory Compiler,内存编译器。顾名思义,是用来生成不同容量memory的工具,输入参数,我们就可以得到生成的文件。生成的文件包括:前端设计verilog模型、逻辑综合的时序库、后端需要的电路网表和LEF/GDS版图文件、其他DFT验证相关的、datasheet手册等等。Memory Compiler由供应商提供,往往是不通用的,界面也不尽相同。同一个厂商的不同工艺下,Memory Compiler不同。相同工艺,不同厂商,Memory Compiler也不同。内存编译器通常是供应商的知识产权,其功能是根据客户的需求生成各种类型的memory。一般的Memory Compiler提供五个ram脚本(rf_sp,sram_sp,rf_tp,sram_dp,rom)。这意味着可以生成1 Port Register file、Single Port SRAM、2 Port Register file、Dual Port SRAM以及ROM。不同的厂商或许还拥有特殊工艺。一般来说,MC只生成常用的memory,特殊的往往需要定制或者组合。考虑到面积和性能,又可以划分为High Speed和High Density等等。图源知乎:SMIC 的Memory Compiler,由Artisan公司提供Memory Compiler使用介绍在使用Memory Compiler时,请务必确保你的RAM从头到位的规格与设定都相同,否则会造成一些不可避免的错误。首先在RTL代码阶段,要用到RAM就要用到verilog代码,此时不需要着急产生其他后阶段的必要数据,因为RTL代码阶段只需要行为级模型即可。当进入门级代码后,RAM compiler就要产生其他的相关数据了,同时要考虑RAM版图的位置与方向。由于重大的设计不会一蹴而就,所以有两个重点,第一个是每次使用RAM compiler时都一定要让它产生特性设置文档,避免忘记自己做过的设定。第二件事是对应的文件名要定义好,否则RAM的方向不同但是又用到了相同的文件名,就会把原始数据覆盖掉。RTL阶段在RTL阶段主要只是产生verilog行为级和设置文件。因为在RTL阶段不需要考虑RAM的位置信息。Memory Compiler提供多种选择,在这个阶段,选择生成RF或是SRAM,以及确定端口数量。如果容量比较大的话,相同设置下,单端口比双端口面积要小,速度也要快,功耗要低。综合与布局布线阶段为了避免重新启用Memory Compiler与以前设置有出入,所以最好一次性将Memory Compiler能够产生的相关数据一并输出。在这里,Memory Compiler还需要产生3种数据。 .LIB 该数据是RAM的时序信息文件 .VCLEF 布局布线工具需要使用的物理信息文件 .SPEC RAM的注释文件在布局布线前,需要考虑RAM的长与宽,估计它的位置与方向,尽量让功能想关的模块靠近一些。将产生的.LIB文件转换成.DB文件,就可以把Memory Compiler生成的RAM加入到代码中进行综合了。在综合工具的脚本中的serch_path下加入RAM的DB文件地址即可。以上为Memory Compiler大致的使用流程,不同的工具在细节上或许有所区别,但大体流程如此。苏州腾芯微电子的Memory Compiler界面接下来,我们来聊一聊,生成的memory——Register file和SRAM。Register file与SRAM的比较首先,厘清一下概念上的问题,Register file和很多的registers不是同一个概念。我们在IC设计里谈到register时,常常是指D触发器,而Register file是一种memory。那么,同为Memory Compiler生成,RF和SRAM有什么区别呢?在比较中,不同规格相比较显然不够客观,也不能让我们更清晰地认识到它们的差异。在比较前,我们需要先把端口的概念搞清楚: 1 port / single port:单端口,读写同端口,需要WE控制输入输出 2 port:双端口,读写分开,输入输出端口固定,可以不用WE控制 dual port:同样是双端口,但读写端口不固定,且都可读可写 RF 的端口示意图SRAM 的端口示意图所以我们应当把1P RF和SP SRAM,2P RF和DP SRAM比较,才有意义。1 Port Register file 和 Single Port SRAM同为单端口,从外部端口看,难以区分1P RF和SP SRAM的区别,但是我们可以从以下几个方面,来进行区分。首先我们以Memory Size:512*32的1P RF和SP SRAM为例。此为1P RF此为SP SRAM从datasheet直观上来看,SRAM比Register file多了OEN(输出使能)。除此之外,Register file和SRAM两者相比,SRAM的最大容量比RF要大。相同配置下,RF的面积更大,功耗更低。在mem比较小的情况下用RF划算,并且同样的mem,RF的长宽比会更小,方便后端floorplan。大容量的时候,SRAM的速度是有优势的。并且SRAM速度快,面积小。同样大小的RF,面积就很大了,速度也慢下来了。所以简单来说,小容量选RF,大容量选SRAM。2P Register file 和 Dual Port SRAM比起1P RF与SP SRAM的比较,2P RF与DP SRAM的差异较为直观。2P RF有一个输入数据总线,一个输出的数据总线。DP SRAM有两个数据输入总线,两个数据输出总线。换句话说,2P RF是一组信号,读写端口固定;而DP SRAM则有两组信号,读写不分开。且两组信号,每组都有自己的地址,输入数据总线,输出数据总线,时钟,读/写控制。这两组可以分别往存储单元写,或从存储单元读出。读可以一直读,写时数据可能存储单元数据更新,数据也可能输出端口。DP SRAM就好像2个SP SRAM共用存储单元。具体的应用,需要结合设计人员和项目自身的需求来选用。小容量,地址少的用RF。有两个外设要同时读写SRAM的,就要用DP SRAM。涉及到具体的选取,则需要由设计人员自己做判断了。以下为读写时序图:图源:数字IC自修室来自微信