搜索到

31

篇与

的结果

-

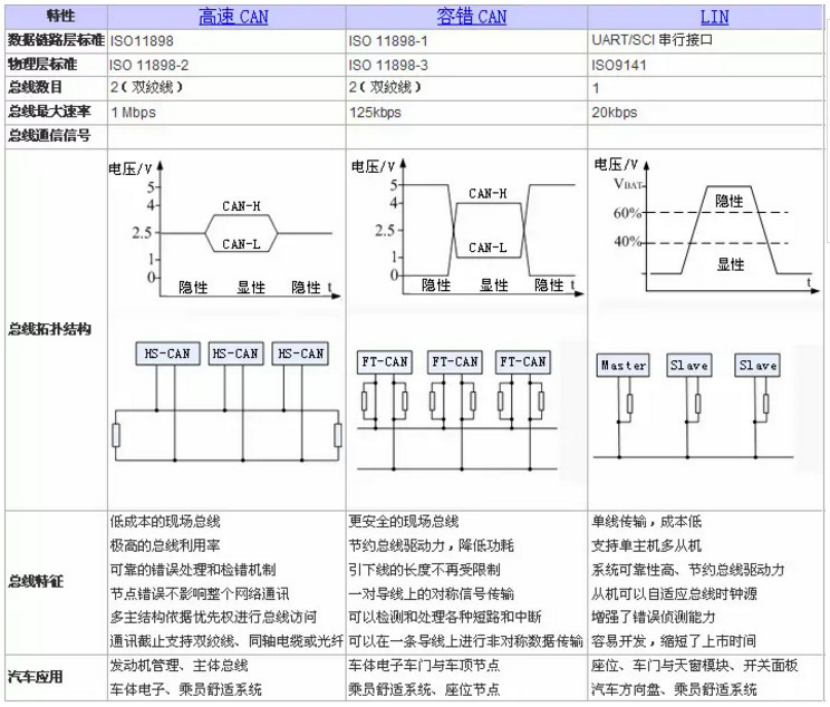

LIN总线详解(2021-11-17) 什么是LIN总线?LIN(Local Interconnect Network)总线是基于UART/SCI(通用异步收发器/串行接口)的低成本串行通讯协议。其目标定位于车身网络模块节点间的低端通信,主要用于智能传感器和执行器的串行通信,而这正是CAN总线的带宽和功能所不要求的部分。CAN/LIN总线区别由于LIN网络在汽车中一般不独立存在,通常会与上层CAN网络相连,形成CAN-LIN网关节点。2.1.LIN总线的主从关系LIN总线采用的是单线传输形式,应用了单主机多从机(有无主动上报的支持?)的概念,总线电平一般为12V,传输速率最高限制为20kbps。由于物理层的限制,一个LIN网络最多可以连接16个节点。总线任务负责:调度总线上帧的传输次序监测数据,处理错误作为标准时钟参考(不是异步通信?)接收从机节点发出的总线唤醒命令从机任务不能直接向总线发送数据,需要接受到主节点发送的帧头后,根据帧头所包含的信息来判断:发送应答接收应答既不接收也不应答LIN的特点网络由一个主节点与若干个从节点构成使用LIN总线可以大幅度削减成本(CAN和Lin都需要收发器,但是Lin属于单线制在线束上节省)传输具有确定性,传播时间可以提前计算LIN具有可预测的EMC(电磁兼容性)性能,为了限制EMC的强度,LIN协议规定最大传输速率为20kbpsLIN总线提供信号的配置、处理、识别和诊断功能(这些都是UART不具备的,可LIN是怎么实现的呢?)3.LIN报文帧结构LIN报文帧包括帧头(hearder)与应答(response)两部分。主机负责发送至帧头;从机负责接收帧头并作出解析,然后决定是发送应答,还是接收应答或不回复。(主机)帧头结构包括同步间隔段、同步段、PID段(受保护ID)段,应答部分包括数据段与效验和段。其中值“0”为显性电平、“1”为隐性电平,这点与CAN总线相类似。在总线上实行“线-与”:当总线有至少一个节点发送显性电平时,总线呈现显性电平;所有节点均发送隐性电平或者不发送信息时,总线呈隐性电平,即显性电平起着主导作用。3.1.1.同步间隔段同步间隔段至少是由13位的显性电平组成,由于帧中的所有间隙或者总线空闲时总线均保持隐性电平状态。所以同步间隔段可以标志一个帧的开始。其中同步间隔段的间隔符至少为1位隐性电平。3.1.2.同步段LIN同步以下降沿为判断标志,采用字节0x55(01010101b)进行同步。在从机节点上可以不采用高精度的时钟,由此带来的偏差,需要通过同步段来进行调整。3.1.3.PID段受保护的ID的前6位叫做帧ID,加上两个奇偶效验码后称作受保护的ID。帧ID的取值范围为0x00~0x3f总共64个,帧ID标识了帧的类别和目的地。从机任务会根据帧头ID作出反应(接收/发送/忽略应答)。其中P0与P1效验如下:LIN总线根据帧ID号的不同,把报文分为信号携带帧、诊断帧、保留帧。PS:从机应答帧是一个完整的帧,与(主节点)帧结构中的“应答”不同!3.1.4.数据段数据段可以包含1-8个字节,其中包含有两种数据类型,信号(singal)和诊断消息(diagnostic messages)。信号由信号携带帧传递,诊断消息由诊断帧传递。协议中并没有规定哪一部分显示数据长度码的信息(这点与CAN总线不同),数据的内容与长度均是由系统设计者根据帧ID事先约定好的。总线上的数据是以广播形式发出,任何节点均可以收到,但并非对每个节点有用(与CAN相同)。具体到发布与接听是由哪个节点进行完成这个取决于应用层的软件配置,一般情况下,对于一个帧中的应答,总线上只存在一个发布节点,否则就会出现错误。事件触发帧例外,可能出现0,1,多个发布节点。3.1.5.效验和段效验和段是为了对帧传输内容进行效验。效验分为标准型效验与增强型效验。采用标准型还是增强型是由主机节点管理,发布节点和收听节点根据帧ID来判断采用哪种效验和。4.LIN总线波形5.LIN总线的通讯上图展示的是LIN总线的通讯方式,可以看出无论什么时候帧头总是由主机节点发布,当主机节点想发布数据时,整个帧全部由主机节点发送。当从机节点想发布数据时,帧头部分由主机节点发布,应答部分由从机节点发布(主机怎么知道从机节点想发布数据,那肯定是主机节点无数据可发,故只发了帧头?),这样其余节点都能收到一个完整的报文帧。可以很直接的观察到,LIN总线的通讯都是由主机节点发起的,只要合理的规定要每个节点的配置,这样就不会存在总线冲突的情况(事件触发帧冲突时采用采用冲突解决进度表)。帧类型5.1.无条件帧无条件帧是具有单一发布节点的,无论信号是否发生变化,帧头均会被无条件应答的帧。如上图中帧ID=0x30应答部分的发布节点为从机节点1,收听节点为主机节点,应用在从机节点向主机节点报告自身状态;帧ID=0x31中,应答部分为主机节点,收听部分为从机节点,应用在主机节点向从机节点发送消息;帧ID=0x32中应答部分的发送节点为从机节点2,收听节点为从机节点1,应用与从机节点之间的通信。5.2.事件触发帧事件触发帧是主机节点在一个帧间隙中查询各从机节点的信号是否发生变化时使用的帧。当存在多个发布节点时,通过冲突解决进度表来解决冲突。当从机节点信号发生变化的频率较低的时候,主机任务一次次地查询各个节点信息会占用一定的带宽。为了减小带宽的占用,引入了事件触发帧的概念。其主要原理就是:当从机节点信息状态没有发生变化的时候,从机节点可以不应答主机发出的帧头;当有多个节点信息同时发生变化的时候,同时应答事件触发帧头会造成总线的冲突。当主机节点检测到冲突时,便会查询冲突解决进度表来依次向各个节点发送无条件帧(无条件帧只有能1个节点应答)来确定从机节点的信息状态。与事件触发帧关联的多个无条件帧需要满足以下5个条件:数据段所包含的数据字节数等长 使用相同的效验与类型 数据段的第一个字节为该无条件帧的受保护ID,这样才能够知道应答是哪个关联的无条件帧发送出来的 由不同的从机节点发布 不能与时间触发帧处于同一个进度表中5.2.1.偶发帧偶发帧是主机节点在同一帧时隙中当自身信号发生变化时向总线启动发送的帧。当存在多个关联的应答信号变化时,通过预先设定的的优先级来仲裁。与事件触发帧类似,偶发帧也定义了一组无条件帧。规定偶发帧只有由主机节点发布。偶发帧的传输可能出现三种情况:当关联的无条件帧没有信号发生变化,这是主机连帧头也不需要发送。当关联的一个无条件帧信号发生变化则发送该帧。当有多个无条件帧发生信号变化时,则按照事先规定要的优先级依次发送。5.2.2.诊断帧诊断帧包括主机请求帧和从机应答帧,主要用于配置、识别和诊断。主机请求帧ID=0x3c,应答部分的发布节点为主机节点;从机应答帧ID=0x3d,应答部分的发布节点为从机节点。数据段规定为8个字节,一律采用标准效验和。5.2.3.保留帧保留帧的ID=0x3e与0x3f,为将来扩张需求用。5.3.进度表进度表是帧的调度表,规定了总线上帧的传输次序以及传输时间。进度表位于主机节点,主机任务根据应用程需要进行调度。进度表可以有多个,一般情况下,轮到某个进度表执行的时候,从该进度表的入口处开始执行,到进度表的最后一个帧时,如果没有新的进度表启动则返回到当前进度表的第一个帧开始执行;也有可能在执行到某个进度表时发生中断,跳到另一个进度表后再返回,如事件触发帧就是一个典型的例子。6.状态机的实现6.1.主机状态机6.2.从机状态机从机任务负责发布或者接听帧的应答状态,包括连两个状态机:同步间隔段与同步段检查器、帧处理器。6.3.从机任务状态机6.4.帧处理任务状态机有道云笔记2021-11-17 15:22:32

LIN总线详解(2021-11-17) 什么是LIN总线?LIN(Local Interconnect Network)总线是基于UART/SCI(通用异步收发器/串行接口)的低成本串行通讯协议。其目标定位于车身网络模块节点间的低端通信,主要用于智能传感器和执行器的串行通信,而这正是CAN总线的带宽和功能所不要求的部分。CAN/LIN总线区别由于LIN网络在汽车中一般不独立存在,通常会与上层CAN网络相连,形成CAN-LIN网关节点。2.1.LIN总线的主从关系LIN总线采用的是单线传输形式,应用了单主机多从机(有无主动上报的支持?)的概念,总线电平一般为12V,传输速率最高限制为20kbps。由于物理层的限制,一个LIN网络最多可以连接16个节点。总线任务负责:调度总线上帧的传输次序监测数据,处理错误作为标准时钟参考(不是异步通信?)接收从机节点发出的总线唤醒命令从机任务不能直接向总线发送数据,需要接受到主节点发送的帧头后,根据帧头所包含的信息来判断:发送应答接收应答既不接收也不应答LIN的特点网络由一个主节点与若干个从节点构成使用LIN总线可以大幅度削减成本(CAN和Lin都需要收发器,但是Lin属于单线制在线束上节省)传输具有确定性,传播时间可以提前计算LIN具有可预测的EMC(电磁兼容性)性能,为了限制EMC的强度,LIN协议规定最大传输速率为20kbpsLIN总线提供信号的配置、处理、识别和诊断功能(这些都是UART不具备的,可LIN是怎么实现的呢?)3.LIN报文帧结构LIN报文帧包括帧头(hearder)与应答(response)两部分。主机负责发送至帧头;从机负责接收帧头并作出解析,然后决定是发送应答,还是接收应答或不回复。(主机)帧头结构包括同步间隔段、同步段、PID段(受保护ID)段,应答部分包括数据段与效验和段。其中值“0”为显性电平、“1”为隐性电平,这点与CAN总线相类似。在总线上实行“线-与”:当总线有至少一个节点发送显性电平时,总线呈现显性电平;所有节点均发送隐性电平或者不发送信息时,总线呈隐性电平,即显性电平起着主导作用。3.1.1.同步间隔段同步间隔段至少是由13位的显性电平组成,由于帧中的所有间隙或者总线空闲时总线均保持隐性电平状态。所以同步间隔段可以标志一个帧的开始。其中同步间隔段的间隔符至少为1位隐性电平。3.1.2.同步段LIN同步以下降沿为判断标志,采用字节0x55(01010101b)进行同步。在从机节点上可以不采用高精度的时钟,由此带来的偏差,需要通过同步段来进行调整。3.1.3.PID段受保护的ID的前6位叫做帧ID,加上两个奇偶效验码后称作受保护的ID。帧ID的取值范围为0x00~0x3f总共64个,帧ID标识了帧的类别和目的地。从机任务会根据帧头ID作出反应(接收/发送/忽略应答)。其中P0与P1效验如下:LIN总线根据帧ID号的不同,把报文分为信号携带帧、诊断帧、保留帧。PS:从机应答帧是一个完整的帧,与(主节点)帧结构中的“应答”不同!3.1.4.数据段数据段可以包含1-8个字节,其中包含有两种数据类型,信号(singal)和诊断消息(diagnostic messages)。信号由信号携带帧传递,诊断消息由诊断帧传递。协议中并没有规定哪一部分显示数据长度码的信息(这点与CAN总线不同),数据的内容与长度均是由系统设计者根据帧ID事先约定好的。总线上的数据是以广播形式发出,任何节点均可以收到,但并非对每个节点有用(与CAN相同)。具体到发布与接听是由哪个节点进行完成这个取决于应用层的软件配置,一般情况下,对于一个帧中的应答,总线上只存在一个发布节点,否则就会出现错误。事件触发帧例外,可能出现0,1,多个发布节点。3.1.5.效验和段效验和段是为了对帧传输内容进行效验。效验分为标准型效验与增强型效验。采用标准型还是增强型是由主机节点管理,发布节点和收听节点根据帧ID来判断采用哪种效验和。4.LIN总线波形5.LIN总线的通讯上图展示的是LIN总线的通讯方式,可以看出无论什么时候帧头总是由主机节点发布,当主机节点想发布数据时,整个帧全部由主机节点发送。当从机节点想发布数据时,帧头部分由主机节点发布,应答部分由从机节点发布(主机怎么知道从机节点想发布数据,那肯定是主机节点无数据可发,故只发了帧头?),这样其余节点都能收到一个完整的报文帧。可以很直接的观察到,LIN总线的通讯都是由主机节点发起的,只要合理的规定要每个节点的配置,这样就不会存在总线冲突的情况(事件触发帧冲突时采用采用冲突解决进度表)。帧类型5.1.无条件帧无条件帧是具有单一发布节点的,无论信号是否发生变化,帧头均会被无条件应答的帧。如上图中帧ID=0x30应答部分的发布节点为从机节点1,收听节点为主机节点,应用在从机节点向主机节点报告自身状态;帧ID=0x31中,应答部分为主机节点,收听部分为从机节点,应用在主机节点向从机节点发送消息;帧ID=0x32中应答部分的发送节点为从机节点2,收听节点为从机节点1,应用与从机节点之间的通信。5.2.事件触发帧事件触发帧是主机节点在一个帧间隙中查询各从机节点的信号是否发生变化时使用的帧。当存在多个发布节点时,通过冲突解决进度表来解决冲突。当从机节点信号发生变化的频率较低的时候,主机任务一次次地查询各个节点信息会占用一定的带宽。为了减小带宽的占用,引入了事件触发帧的概念。其主要原理就是:当从机节点信息状态没有发生变化的时候,从机节点可以不应答主机发出的帧头;当有多个节点信息同时发生变化的时候,同时应答事件触发帧头会造成总线的冲突。当主机节点检测到冲突时,便会查询冲突解决进度表来依次向各个节点发送无条件帧(无条件帧只有能1个节点应答)来确定从机节点的信息状态。与事件触发帧关联的多个无条件帧需要满足以下5个条件:数据段所包含的数据字节数等长 使用相同的效验与类型 数据段的第一个字节为该无条件帧的受保护ID,这样才能够知道应答是哪个关联的无条件帧发送出来的 由不同的从机节点发布 不能与时间触发帧处于同一个进度表中5.2.1.偶发帧偶发帧是主机节点在同一帧时隙中当自身信号发生变化时向总线启动发送的帧。当存在多个关联的应答信号变化时,通过预先设定的的优先级来仲裁。与事件触发帧类似,偶发帧也定义了一组无条件帧。规定偶发帧只有由主机节点发布。偶发帧的传输可能出现三种情况:当关联的无条件帧没有信号发生变化,这是主机连帧头也不需要发送。当关联的一个无条件帧信号发生变化则发送该帧。当有多个无条件帧发生信号变化时,则按照事先规定要的优先级依次发送。5.2.2.诊断帧诊断帧包括主机请求帧和从机应答帧,主要用于配置、识别和诊断。主机请求帧ID=0x3c,应答部分的发布节点为主机节点;从机应答帧ID=0x3d,应答部分的发布节点为从机节点。数据段规定为8个字节,一律采用标准效验和。5.2.3.保留帧保留帧的ID=0x3e与0x3f,为将来扩张需求用。5.3.进度表进度表是帧的调度表,规定了总线上帧的传输次序以及传输时间。进度表位于主机节点,主机任务根据应用程需要进行调度。进度表可以有多个,一般情况下,轮到某个进度表执行的时候,从该进度表的入口处开始执行,到进度表的最后一个帧时,如果没有新的进度表启动则返回到当前进度表的第一个帧开始执行;也有可能在执行到某个进度表时发生中断,跳到另一个进度表后再返回,如事件触发帧就是一个典型的例子。6.状态机的实现6.1.主机状态机6.2.从机状态机从机任务负责发布或者接听帧的应答状态,包括连两个状态机:同步间隔段与同步段检查器、帧处理器。6.3.从机任务状态机6.4.帧处理任务状态机有道云笔记2021-11-17 15:22:32 -

timer的输入捕获功能(2021-11-18 ) 内部定时器结构在 STM32定时器系列 - STM32常规定时器时基与时钟源 这篇博文中,我们讲述过,定时器的结构。其实我们只需要看这张图就可以了:看流程的走向,由 时钟源 提供时钟 到 时间基(一般时钟源都是选择内部的CLK)这里需要注意的就是看定时器时挂在那个总线下的,APB1 与 APB2 CLK不一样。然后流向 输入捕获 的只有 PSC(预分配器) 并没有 重装载寄存器,因此,采样的频率就是定时器经过预分配器之后的频率,与重装载无关。输入捕获【Input Capture】基本原理定时器针对外部输入信号或者内部触发信号实现"边沿捕获";产生捕捉事件,并可以触发中断或者DMA请求,同时记录捕捉时刻计数器的值,基于这个原理,配合计数器实时计数器功能可以对捕捉信号进行脉冲宽度的测量,进而实现对周期性波形测量其周期与占空比,或者用来做通信解码(红外通信解码)。具体到我们的定时器,输入捕获的功能主要是靠捕获比较单元来实现。输入捕获模式下:当捕获单元捕获到外来有效信号边沿事件【上升沿或者下降沿】,将此刻计数器的值锁存到CCR影子寄存器并自动将CCR影子寄存器的值拷贝进CCR预装寄存器,以供用户读取。关于CCR寄存器,它是由影子寄存器与预装寄存器组成,带预装使能控制位。在输入模式下,此时CCR对用户是只读的,不可对其修改、赋值。外部输入信号作为输入捕获信号,往往需要经过如下几个阶段:一般经过滤波,边沿检测,极性选择,捕获信号选择,捕获信号分频,最终进入捕获功能模块从而实现输入捕获。其中边沿检测、极性选择确定捕获单元对捕获信号的捕获极性,即捕获上升沿还是下降沿,甚至双边沿。捕获信号选择是指:对输入捕获信号的信号进行选择,即前面提到过的作为捕获信号的信号源有两大类;捕获信号分频是指对将被用作捕获信号的信号进行分频,比如2分频,3分频等,分频之后送到捕获功能模块去完成输入捕获。(这里如果输入信号频率大于采样频率就可以采用捕获信号分频的方法降低信号频率,达到可以采集的目标,计算结果后,在乘以分频系数)外部输入信号的滤波为了防止因为输入信号上的噪声或边沿抖动而导致误计数、误触发,我们可以针对外部输入信号进行合适的滤波。用户要做的就是针对输入信号具体情况【频率、噪声等】,通过寄存器配置适当的滤波参数,选择适当采样时钟和采样次数,其它事情交给定时器硬件去处理。这样也可以减少因为做滤波而导致的软件开销。假设我们让定时器对某输入通道的信号进行捕捉,捕捉极性为上升沿。设置滤波的采样时钟与定时器内部时钟频率一致,采样次数为4次。则每当捕捉到上升沿时,硬件连续根据采样频率来采样4次【包括发生捕捉触发沿的那一次】。如果4次采样结果均为高电平,则此次触发有效。并可以产生触发事件,该事件可以触发中断或DMA请求,同时捕捉单元将此刻计数器的值放入到捕捉比较寄存器CCR中。当然,如果捕捉到触发边沿后,没法做到连续4次采样均为高电平,则该触发无效,将会被丢弃。这样达到滤除噪声的目的。内部触发输入信号【ITRx】作为输入捕获信号与输入捕获相关的事件捕获时刻的计数器值锁存到对应捕获通道的CCRx寄存器。对应通道的捕获事件/中断会被置位;【CCxIF@TIMx_SR】如果允许了捕获中断或者DMA请求,可以触发中断或者DMA请求。取决于【CCxIE/CCxDE@TIMx_DIER】配置。如果运行连续捕获事件,前一次没有清零的话会置位【CCxOF@TIMx_SR】对于CCxIF标志可以软件清零或者读取CCR来清零。可以通过设置位【CCxG@TIMx_EGR】来软件触发输入捕获事件。与输入捕获相关的事件主要就这些,我们要做到心中有数。只要了解它们后,在我们的定时器的实际应用中才能灵活使用它们,实现我们需要的功能。如在发生输入捕获事件时,利用相关中断或DMA请求实现其它功能,比如做数据的更新、ADC的启动、其它定时器的启动等等。通过输入捕获测量脉冲周期在输入捕捉模式下,定时器可用于测量外部信号周期。根据定时器时钟、预分频器和定时器分辨率,可推导出最大测量周期。相应的定时器配置包括:通过对CCMRx 寄存器中的 CCxS 位选择有效输入。根据需要,通过对 CCMRx 寄存器中的 IC1F[3:0] 位执行操作以编程滤波器参数,并通过对IC1PSC[1:0] 位执行写操作以编程预分频器。通过对 CCxNP/CCxP 位执行写操作选择极性,即选择上升沿触发、下降沿触发或边沿触发。当输入通道检测到相应的信号发生跳变时,可使用输入捕捉模块进行捕捉。要获取外部信号周期,需连续进行两次捕捉,通过将两次捕捉到的值相减可计算得到周期。对于单沿捕捉,计数器采用向上计数模式,待测信号不长于计数器的计数周期时:假设两次连续捕捉值为 CCRx_tn 和 CCRx_tn+1● 如果 CCRx_tn < CCRx_tn+1:捕捉宽度= CCRx_tn+1 - CCRx_tn● 如果 CCRx_tn > CCRx_tn+1:捕捉宽度= (ARR_max - CCRx_tn) + CCRx_tn+1如果待测信号周期长于当前计数器周期的话,需要考虑溢出问题。实际应用中有时因为忽略了这点而导致测试不正确。有道云笔记2021-11-18 17:40:28

timer的输入捕获功能(2021-11-18 ) 内部定时器结构在 STM32定时器系列 - STM32常规定时器时基与时钟源 这篇博文中,我们讲述过,定时器的结构。其实我们只需要看这张图就可以了:看流程的走向,由 时钟源 提供时钟 到 时间基(一般时钟源都是选择内部的CLK)这里需要注意的就是看定时器时挂在那个总线下的,APB1 与 APB2 CLK不一样。然后流向 输入捕获 的只有 PSC(预分配器) 并没有 重装载寄存器,因此,采样的频率就是定时器经过预分配器之后的频率,与重装载无关。输入捕获【Input Capture】基本原理定时器针对外部输入信号或者内部触发信号实现"边沿捕获";产生捕捉事件,并可以触发中断或者DMA请求,同时记录捕捉时刻计数器的值,基于这个原理,配合计数器实时计数器功能可以对捕捉信号进行脉冲宽度的测量,进而实现对周期性波形测量其周期与占空比,或者用来做通信解码(红外通信解码)。具体到我们的定时器,输入捕获的功能主要是靠捕获比较单元来实现。输入捕获模式下:当捕获单元捕获到外来有效信号边沿事件【上升沿或者下降沿】,将此刻计数器的值锁存到CCR影子寄存器并自动将CCR影子寄存器的值拷贝进CCR预装寄存器,以供用户读取。关于CCR寄存器,它是由影子寄存器与预装寄存器组成,带预装使能控制位。在输入模式下,此时CCR对用户是只读的,不可对其修改、赋值。外部输入信号作为输入捕获信号,往往需要经过如下几个阶段:一般经过滤波,边沿检测,极性选择,捕获信号选择,捕获信号分频,最终进入捕获功能模块从而实现输入捕获。其中边沿检测、极性选择确定捕获单元对捕获信号的捕获极性,即捕获上升沿还是下降沿,甚至双边沿。捕获信号选择是指:对输入捕获信号的信号进行选择,即前面提到过的作为捕获信号的信号源有两大类;捕获信号分频是指对将被用作捕获信号的信号进行分频,比如2分频,3分频等,分频之后送到捕获功能模块去完成输入捕获。(这里如果输入信号频率大于采样频率就可以采用捕获信号分频的方法降低信号频率,达到可以采集的目标,计算结果后,在乘以分频系数)外部输入信号的滤波为了防止因为输入信号上的噪声或边沿抖动而导致误计数、误触发,我们可以针对外部输入信号进行合适的滤波。用户要做的就是针对输入信号具体情况【频率、噪声等】,通过寄存器配置适当的滤波参数,选择适当采样时钟和采样次数,其它事情交给定时器硬件去处理。这样也可以减少因为做滤波而导致的软件开销。假设我们让定时器对某输入通道的信号进行捕捉,捕捉极性为上升沿。设置滤波的采样时钟与定时器内部时钟频率一致,采样次数为4次。则每当捕捉到上升沿时,硬件连续根据采样频率来采样4次【包括发生捕捉触发沿的那一次】。如果4次采样结果均为高电平,则此次触发有效。并可以产生触发事件,该事件可以触发中断或DMA请求,同时捕捉单元将此刻计数器的值放入到捕捉比较寄存器CCR中。当然,如果捕捉到触发边沿后,没法做到连续4次采样均为高电平,则该触发无效,将会被丢弃。这样达到滤除噪声的目的。内部触发输入信号【ITRx】作为输入捕获信号与输入捕获相关的事件捕获时刻的计数器值锁存到对应捕获通道的CCRx寄存器。对应通道的捕获事件/中断会被置位;【CCxIF@TIMx_SR】如果允许了捕获中断或者DMA请求,可以触发中断或者DMA请求。取决于【CCxIE/CCxDE@TIMx_DIER】配置。如果运行连续捕获事件,前一次没有清零的话会置位【CCxOF@TIMx_SR】对于CCxIF标志可以软件清零或者读取CCR来清零。可以通过设置位【CCxG@TIMx_EGR】来软件触发输入捕获事件。与输入捕获相关的事件主要就这些,我们要做到心中有数。只要了解它们后,在我们的定时器的实际应用中才能灵活使用它们,实现我们需要的功能。如在发生输入捕获事件时,利用相关中断或DMA请求实现其它功能,比如做数据的更新、ADC的启动、其它定时器的启动等等。通过输入捕获测量脉冲周期在输入捕捉模式下,定时器可用于测量外部信号周期。根据定时器时钟、预分频器和定时器分辨率,可推导出最大测量周期。相应的定时器配置包括:通过对CCMRx 寄存器中的 CCxS 位选择有效输入。根据需要,通过对 CCMRx 寄存器中的 IC1F[3:0] 位执行操作以编程滤波器参数,并通过对IC1PSC[1:0] 位执行写操作以编程预分频器。通过对 CCxNP/CCxP 位执行写操作选择极性,即选择上升沿触发、下降沿触发或边沿触发。当输入通道检测到相应的信号发生跳变时,可使用输入捕捉模块进行捕捉。要获取外部信号周期,需连续进行两次捕捉,通过将两次捕捉到的值相减可计算得到周期。对于单沿捕捉,计数器采用向上计数模式,待测信号不长于计数器的计数周期时:假设两次连续捕捉值为 CCRx_tn 和 CCRx_tn+1● 如果 CCRx_tn < CCRx_tn+1:捕捉宽度= CCRx_tn+1 - CCRx_tn● 如果 CCRx_tn > CCRx_tn+1:捕捉宽度= (ARR_max - CCRx_tn) + CCRx_tn+1如果待测信号周期长于当前计数器周期的话,需要考虑溢出问题。实际应用中有时因为忽略了这点而导致测试不正确。有道云笔记2021-11-18 17:40:28 -

SWD协议通信的简单总结(2022-08-05) 对SWD协议做一个简单的总结SWD协议1.SWD协议框图SWD协议可以配置单片机内部几乎所有的寄存器。整个SWD过程是分级进行的,时钟信号由SWCLK 管脚输入,数据信号从SWDIO管脚输入输出。首先HOST对SW-DP进行操作,确定AP寄存器的参数,达到对Cortex Memory Map进行操作。Debug Access Port(DAP)由两部分组成:Debug Port(DP)Memory Access Port(MEM-AP)(AP)2.DAP寄存器1、DP寄存器IDCODE:识别码寄存器,用于识别SW-DP。ID:0x0BB11477(M0)ABORT:中止寄存器,强制AP事务中止。在通信中,若发生粘性错 误位置1(ack = 4)。将0b1写入ABORT中,会生成一个DAP中止使当前AP事务中止。CTRL_STAT_W/R:控制状态寄存器,用于控制和获取有关DP的状态信息。SELECT:AHB-AP选择寄存器,选择要访问的端口(AP)和AP中的bank地址和DP的bank地址。RDBUFF:读缓冲寄存器,在SW-DP上,RDBUFF显示了在上一次AP读取期间捕获的数据,允许重复返回值而不生成新的AP访问。2、AP寄存器CSW_W:控制/状态字寄存器,CSW配置和控制通过MEM-AP访问连接的内存系统。size:32bit-0b010;16bit-0b001TAR_W:传送地址寄存器,TAR保存要通过AP访问的内存地址。DRW_W/R:数据读/写寄存器,DRW将AP访问中传递的值直接映射到TAR中指定的地址的一个或多个内存访问。IDR:识别寄存器,IDR标识访问的端口3.读/写时序及命令1、SWD时序1)成功的写时序 (烧录器往DP或MEM-AP寄存器的写操作)2)成功的读时序 (指烧录器读取DP或MEM-AP寄存器的数据)3)DAP没准备好,响应WAIT给HOST,此次通讯结束4)DAP出错,响应FAULT给HOST,此次通讯结束2、SWD命令详情1)主机 HOST 发出的请求由 8bit 组成Bit0:Start,固定为 1。Bit1:APnDP,0表示访问 DP 寄存器,1 表示访问 MEM-AP 寄存器。Bit2:RnW,0表示写请求,1表示读请求。Bit[4:3]:地址值A[3:2],存放DP/AP寄存器的地址。Bit5:Parity,用于表示由{APnDP,RnW, A[2:3]}组成这四位数的奇偶总个数。Bit6:Stop,固定为0。Bit7:Park,固定为1。2)Target返回的ACK值由3bit组成ACK[0:2]==001,表示FAULTACK[0:2]==010,表示WAITACK[0:2]==100,表示OK response3)数据由32bit有效数据 + 1bit数据的奇偶校验位组成chip连接1.获取芯片IDSWD协议的操作步骤:1、SWD初始化步骤:a)初始化IO口,SWCLK和SWIO设置为输出模式,保持SWDIO=1,保证Host连续发送至少50个“1”,使得Target进行Line Reset。b)发送JTAG to SWD命令,0x79、0xE7两个byte(在ARM-Debug_Interface官方文档中可以查到),随后再发送一次line reset操作。c)至少发送两个Idle信号,保持SWDIO=0。d)读取Chip ID,从而完成SWD初始化操作。此时只能访问DP寄存器组,AP寄存器组还无法访问。2、解锁AP步骤如下:1)CTRL/STAT寄存器写入0x50000000 (第28位和第30位),开启debug port及其时钟2)SELECT寄存器写入的数据为0x000000F0,bank:0xF3)读取IDR寄存器(addr = 0xFC)的数据并验证4)SELECT寄存器写入的数据为0x00000000,bank:0x05)CSW寄存器写入0x00000002,data_size:32bit注意:1、CTRL/STAT寄存器:CSYSPWRUPREQ:System powerup requestCDBGPWRUPREQ:Debug powerup request2、SELECT寄存器:APSEL=0X00表示AHB访问;APBANKSEL:选择当前AP的bank地址。3、读取IDR寄存器的数值时,需要两次,第一次是dummy read,第二次读取到的才是正确的数据。(第二次也可以读RDBUFF寄存器)4、CSW寄存器:Size:访问MEM-AP的数据类型的大小其中:寄存器的数据是32bit–0b010,编程写入Flash的数据是16bit–0b001。2.读/写操作如果想要写入/读出MCU内部Flash的数值,需要用到两个AP寄存器:TAR(The Transfer Address Register)和DRW(The Data Read/Write Register)。1、写操作1)在TAR_W寄存器中写入要访问的内存地址数值 (addr = 0x08000000)2)在DRW_W寄存器中写入要往内存中写入的数据 (data = 0x12345678)2、读操作1)在TAR_W寄存器中写入要访问的内存地址数值 (addr = 0x08000000)2)从DRW_R寄存器中读取要访问的内存中存放的数据3)从RDBUFF寄存器(DP)中读取数据/从DRW_R寄存器(AP)中读取数据注意:由于读取AP寄存器的特殊性,当读取AP寄存器时,返回的数据是上一次传输的值。也就是说,有两种方式可以得到正确的 AP 寄存器的值。发送两次读DRW寄存器的操作发送一次读DRW寄存器的操作(读取上一周期的数据),再发送一次读RDBUFF寄存器的操作(读取自己需要的数据)总的来说,读写DP寄存器没有迟滞,不需要读写两次。读取AP寄存器,有迟滞,第一次读AP,是上一周期的值,第二次读AP才是想要的值。写AP寄存器,没有迟滞。如TAR,DRW只需要写一次即可写进去。有道云笔记2022-08-05 15:08:26

SWD协议通信的简单总结(2022-08-05) 对SWD协议做一个简单的总结SWD协议1.SWD协议框图SWD协议可以配置单片机内部几乎所有的寄存器。整个SWD过程是分级进行的,时钟信号由SWCLK 管脚输入,数据信号从SWDIO管脚输入输出。首先HOST对SW-DP进行操作,确定AP寄存器的参数,达到对Cortex Memory Map进行操作。Debug Access Port(DAP)由两部分组成:Debug Port(DP)Memory Access Port(MEM-AP)(AP)2.DAP寄存器1、DP寄存器IDCODE:识别码寄存器,用于识别SW-DP。ID:0x0BB11477(M0)ABORT:中止寄存器,强制AP事务中止。在通信中,若发生粘性错 误位置1(ack = 4)。将0b1写入ABORT中,会生成一个DAP中止使当前AP事务中止。CTRL_STAT_W/R:控制状态寄存器,用于控制和获取有关DP的状态信息。SELECT:AHB-AP选择寄存器,选择要访问的端口(AP)和AP中的bank地址和DP的bank地址。RDBUFF:读缓冲寄存器,在SW-DP上,RDBUFF显示了在上一次AP读取期间捕获的数据,允许重复返回值而不生成新的AP访问。2、AP寄存器CSW_W:控制/状态字寄存器,CSW配置和控制通过MEM-AP访问连接的内存系统。size:32bit-0b010;16bit-0b001TAR_W:传送地址寄存器,TAR保存要通过AP访问的内存地址。DRW_W/R:数据读/写寄存器,DRW将AP访问中传递的值直接映射到TAR中指定的地址的一个或多个内存访问。IDR:识别寄存器,IDR标识访问的端口3.读/写时序及命令1、SWD时序1)成功的写时序 (烧录器往DP或MEM-AP寄存器的写操作)2)成功的读时序 (指烧录器读取DP或MEM-AP寄存器的数据)3)DAP没准备好,响应WAIT给HOST,此次通讯结束4)DAP出错,响应FAULT给HOST,此次通讯结束2、SWD命令详情1)主机 HOST 发出的请求由 8bit 组成Bit0:Start,固定为 1。Bit1:APnDP,0表示访问 DP 寄存器,1 表示访问 MEM-AP 寄存器。Bit2:RnW,0表示写请求,1表示读请求。Bit[4:3]:地址值A[3:2],存放DP/AP寄存器的地址。Bit5:Parity,用于表示由{APnDP,RnW, A[2:3]}组成这四位数的奇偶总个数。Bit6:Stop,固定为0。Bit7:Park,固定为1。2)Target返回的ACK值由3bit组成ACK[0:2]==001,表示FAULTACK[0:2]==010,表示WAITACK[0:2]==100,表示OK response3)数据由32bit有效数据 + 1bit数据的奇偶校验位组成chip连接1.获取芯片IDSWD协议的操作步骤:1、SWD初始化步骤:a)初始化IO口,SWCLK和SWIO设置为输出模式,保持SWDIO=1,保证Host连续发送至少50个“1”,使得Target进行Line Reset。b)发送JTAG to SWD命令,0x79、0xE7两个byte(在ARM-Debug_Interface官方文档中可以查到),随后再发送一次line reset操作。c)至少发送两个Idle信号,保持SWDIO=0。d)读取Chip ID,从而完成SWD初始化操作。此时只能访问DP寄存器组,AP寄存器组还无法访问。2、解锁AP步骤如下:1)CTRL/STAT寄存器写入0x50000000 (第28位和第30位),开启debug port及其时钟2)SELECT寄存器写入的数据为0x000000F0,bank:0xF3)读取IDR寄存器(addr = 0xFC)的数据并验证4)SELECT寄存器写入的数据为0x00000000,bank:0x05)CSW寄存器写入0x00000002,data_size:32bit注意:1、CTRL/STAT寄存器:CSYSPWRUPREQ:System powerup requestCDBGPWRUPREQ:Debug powerup request2、SELECT寄存器:APSEL=0X00表示AHB访问;APBANKSEL:选择当前AP的bank地址。3、读取IDR寄存器的数值时,需要两次,第一次是dummy read,第二次读取到的才是正确的数据。(第二次也可以读RDBUFF寄存器)4、CSW寄存器:Size:访问MEM-AP的数据类型的大小其中:寄存器的数据是32bit–0b010,编程写入Flash的数据是16bit–0b001。2.读/写操作如果想要写入/读出MCU内部Flash的数值,需要用到两个AP寄存器:TAR(The Transfer Address Register)和DRW(The Data Read/Write Register)。1、写操作1)在TAR_W寄存器中写入要访问的内存地址数值 (addr = 0x08000000)2)在DRW_W寄存器中写入要往内存中写入的数据 (data = 0x12345678)2、读操作1)在TAR_W寄存器中写入要访问的内存地址数值 (addr = 0x08000000)2)从DRW_R寄存器中读取要访问的内存中存放的数据3)从RDBUFF寄存器(DP)中读取数据/从DRW_R寄存器(AP)中读取数据注意:由于读取AP寄存器的特殊性,当读取AP寄存器时,返回的数据是上一次传输的值。也就是说,有两种方式可以得到正确的 AP 寄存器的值。发送两次读DRW寄存器的操作发送一次读DRW寄存器的操作(读取上一周期的数据),再发送一次读RDBUFF寄存器的操作(读取自己需要的数据)总的来说,读写DP寄存器没有迟滞,不需要读写两次。读取AP寄存器,有迟滞,第一次读AP,是上一周期的值,第二次读AP才是想要的值。写AP寄存器,没有迟滞。如TAR,DRW只需要写一次即可写进去。有道云笔记2022-08-05 15:08:26 -

verilog中clock不使用negedge的三个原因 (2008-06-10 12:31:58) verilog中clock不使用negedge的三个原因Verilog中典型的counter逻辑是这样的:always@(posedge clk or negedge reset) beginif(reset == 1'b0) reg_inst1 <= 8'd0; else if(clk == 1'b1) reg_inst1 <= reg_inst1 + 1'd1; else reg_inst1 <= reg_inst1;endclk为什么要用posedge,而不用negedge呢?请教丹内先生,答案如下:一般情况下,系统中统一用posedge,避免用negedge,降低设计的复杂度,可以减少出错。 在ModelSim 仿真中,时钟是很严格的,但是在真实的晶振所产生的clock却是不严格的,比如高电平和低电平的时间跨度不一样,甚至非周期性的微小波动。如果只使用 posedge,则整个系统的节拍都按照clock上升延对齐,如果用到了negedge,则系统的节拍没有统一到一个点上。上升延到上升延肯定是一个时 钟周期,但是上升延到下降延却很可能不是半个周期。这都会出现问题。 FPGA特有的东西:Global CLK。FPGA内部有专门的CLK“线”,和一般的逻辑门的走法不一样,目的是为了保证整个FPGA片内的时钟一致,这个东西就叫Global CLK。(这个和negedge有什么关系?没搞懂)

verilog中clock不使用negedge的三个原因 (2008-06-10 12:31:58) verilog中clock不使用negedge的三个原因Verilog中典型的counter逻辑是这样的:always@(posedge clk or negedge reset) beginif(reset == 1'b0) reg_inst1 <= 8'd0; else if(clk == 1'b1) reg_inst1 <= reg_inst1 + 1'd1; else reg_inst1 <= reg_inst1;endclk为什么要用posedge,而不用negedge呢?请教丹内先生,答案如下:一般情况下,系统中统一用posedge,避免用negedge,降低设计的复杂度,可以减少出错。 在ModelSim 仿真中,时钟是很严格的,但是在真实的晶振所产生的clock却是不严格的,比如高电平和低电平的时间跨度不一样,甚至非周期性的微小波动。如果只使用 posedge,则整个系统的节拍都按照clock上升延对齐,如果用到了negedge,则系统的节拍没有统一到一个点上。上升延到上升延肯定是一个时 钟周期,但是上升延到下降延却很可能不是半个周期。这都会出现问题。 FPGA特有的东西:Global CLK。FPGA内部有专门的CLK“线”,和一般的逻辑门的走法不一样,目的是为了保证整个FPGA片内的时钟一致,这个东西就叫Global CLK。(这个和negedge有什么关系?没搞懂) -

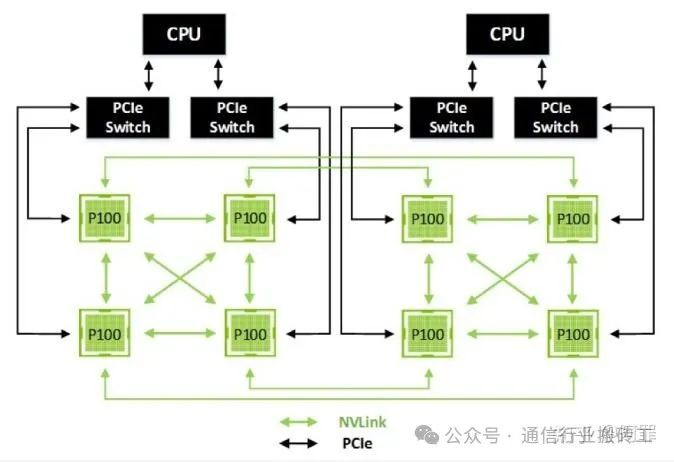

NVLink1.0~5.0: 高速互联的架构演进之路 01、引言:数据时代的“高速公路”在人工智能(AI)和高性能计算(HPC)的浪潮中,计算能力的提升不仅依赖于处理器性能,还需要高效的数据传输通道。传统 PCIe 互联虽广泛应用,但其带宽和延迟已难以满足现代计算需求。NVIDIA 的 NVLink 应运而生,作为一种高速、低延迟的点对点互联技术,它为多 GPU 和 CPU-GPU 系统提供了“数据高速公路”,显著提升了计算效率。本文将从技术视角深入剖析 NVLink 的架构、演进历程、应用场景及生态布局,为科技人士、通信工程师和学术研究者提供全面洞察。02、NVLink架构:技术核心与关键特性NVLink 是 NVIDIA 专为高性能计算设计的互联技术,旨在实现 GPU 间或 GPU 与 CPU 间的高速数据交换。其架构基于点对点通信,采用多通道设计,每个通道(称为“链接”)包含多个差分对,提供高带宽和低延迟的数据传输。核心特性高带宽:NVLink 提供远超 PCIe 的带宽。例如,最新 NVLink 5.0 单链接双向带宽达 200 GB/s,总带宽可达 1.8 TB/s,而 PCIe 5.0 x16 仅约 126 GB/s。低延迟:通过专用通道和优化协议,NVLink 显著降低数据传输延迟,适合实时计算任务。缓存一致性:NVLink 支持 GPU 间或 GPU-CPU 间的缓存一致性,允许共享统一内存空间,减少数据拷贝开销。可扩展性:结合 NVSwitch,NVLink 支持全连接拓扑,使多 GPU 系统实现高效通信。NVLink 的工作原理类似高速公路网络:每个 GPU 或 CPU 是“城市”,链接是“车道”,NVSwitch 则像“交通枢纽”,确保数据流畅无阻。这种设计特别适合需要大规模并行计算的场景,如 AI 模型训练和科学模拟。03、技术演进:从NVLink 1.0到5.0 的跨越NVLink 自 2016 年首次亮相以来,经历了五代技术迭代,每一代都针对计算需求的增长进行了优化。版本年份GPU 架构每链接带宽(双向,GB/s)链接数总带宽(GB/s)备注1.02016Pascal404160首代,Tesla P1002.02017Volta506300支持 NVSwitch,DGX-13.02020Ampere5012600A100 GPU,广泛用于云4.02022Hopper10018900H100 GPU,PAM4 编码5.02024Blackwell200181800GB200 NVL72,AI 优化以下是对其演进历程的详细分析,涵盖技术原理、软硬件架构及技术演进亮点。1、NVLink 1.0(2016):开创高速互联先河GPU架构:Pascal(Tesla P100)带宽:每链接 40 GB/秒(双向,20 GB/秒单向),P100 支持 4 个链接,总带宽 160 GB/秒。技术原理:采用 NRZ(非归零)信号编码,每个时钟周期传输 1 位数据。NVLink 使用差分对传输,包含 8 条子通道,每条子通道运行在 20 Gbps。协议栈基于定制的点对点通信,优化了数据包格式,减少了传输开销。软硬件软件架构:NVLink 1.0 直接集成在 P100 GPU 芯片上,每个链接占用专用硅片区域。软件方面,CUDA 7.0 引入了cudaMemcpyPeer API技术,支持GPU间直接内存拷贝,简化了多GPU编程。技术演进亮点:首次亮相于Pascal架构的Tesla P100,提供160GB/s总带宽,较PCIexpress 3.0x16(约32GB/s)提升数倍,奠定了多GPU互联基础。应用场景:主要用于早期深度学习任务,如图像识别模型(如 ResNet)的训练。DGX-1 系统首次采用 NVLink 1.0,连接 8 个 P100 GPU,奠定了多 GPU 系统的基础。挑战与突破:NVLink 1.0 的主要挑战是链接数量有限,仅支持 4 个链接,限制了多 GPU 系统的扩展性。NVIDIA 通过优化协议和硬件设计,确保了低延迟和高可靠性,为后续版本奠定了技术基础。2、NVLink 2.0(2017):引入 NVSwitch,扩展规模GPU架构:Volta(Tesla V100)带宽:每链接 50 GB/秒(双向,25 GB/秒单向),V100 支持 6 个链接,总带宽 300 GB/秒。技术原理:继续使用 NRZ 编码,但通过提高时钟频率和优化信号完整性,将单链接带宽提升 25%。引入 NVSwitch,一个高性能交换矩阵,支持全连接拓扑,允许多达 16 个 GPU 直接通信。NVSwitch 包含 18 个 NVLink 端口,每个端口提供 50 GB/秒带宽,总吞吐量达 900 GB/秒。软硬件架构:NVSwitch 作为独立芯片,集成在 DGX-2 系统,连接 16 个 V100 GPU。软件方面,CUDA 9.0 和 NCCL 2.0 优化了集体通信操作(如 all-reduce),提升了分布式训练效率。NVLink 2.0 支持缓存一致性,允许多 GPU 共享统一内存空间。技术演进亮点:引入 NVSwitch,支持全连接拓扑,带宽增至 300 GB/s,广泛用于 DGX-1 系统。应用场景:广泛用于 AI 研究和企业级应用,如自然语言处理(BERT 模型)和推荐系统训练。Summit 超级计算机(橡树岭国家实验室)采用 NVLink 2.0,连接 IBM Power9 CPU 和 V100 GPU,位列全球超算前列。挑战与突破:NVLink 2.0 解决了扩展性问题,但 NVSwitch 的引入增加了系统复杂性和成本。NVIDIA 通过优化交换矩阵设计和协议栈,确保了高吞吐量和低延迟。3、NVLink 3.0(2020):链接数量翻倍GPU架构:Ampere(A100)带宽:每链接 50 GB/秒(双向),A100 支持 12 个链接,总带宽 600 GB/秒。技术原理:维持 NRZ 编码,但通过增加链接数量(从 6 到 12),将总带宽翻倍。引入多实例 GPU(MIG)技术,允许将 A100 GPU 虚拟化为多个独立实例,每个实例可分配 NVLink 链接,提升资源利用率。协议栈进一步优化,支持更高效的缓存一致性。软硬件架构:A100 GPU 的 NVLink 端口集成在芯片边缘,采用高密度封装技术。DGX A100 系统使用 8 个 A100 GPU,通过 NVSwitch 连接,提供 4.8 TB/秒的内部带宽。CUDA 11.0 和 NCCL 2.7 增强了对 NVLink 3.0 的支持,优化了分布式训练和推理。技术演进亮点:链接数翻倍至 12,带宽达 600 GB/s,搭配 A100 GPU,满足大模型训练需求。应用场景:云服务(如 AWS P4d 实例)、AI 训练和推理,以及 HPC 任务(如分子动力学模拟)。A100 的 MIG 功能特别适合云端多租户环境。挑战与突破:链接数量的增加提高了芯片设计复杂性,NVIDIA 通过先进的硅片布局和信号完整性技术解决了这一问题。MIG 技术的引入进一步提升了灵活性。4、NVLink 4.0(2022):PAM4 信号革命GPU架构:Hopper(H100)带宽:每链接 100 GB/秒(双向,50 GB/秒单向),H100 支持 18 个链接,总带宽 900 GB/秒。技术原理:首次采用 PAM4(4 级脉冲幅度调制)信号编码,每个时钟周期传输 2 位数据,较 NRZ 翻倍数据率。PAM4 要求更高的信噪比,NVIDIA 通过先进的纠错码(ECC)和信号调制技术确保可靠性。协议栈优化了流量管理,支持动态带宽分配。软硬件架构:H100 GPU 使用 TSMC 4nm 工艺,NVLink 端口数量增至 18,集成在芯片边缘的高速 I/O 区域。DGX H100 系统通过 NVSwitch 连接 8 个 H100 GPU,提供 7.2 TB/秒的内部带宽。CUDA 12.0 和 NCCL 2.10 引入了新的通信原语,优化了超大规模模型训练。技术演进亮点:采用 PAM4 编码,链接数增至 18,总带宽 900 GB/s,H100 GPU 成为 HPC 标杆。应用场景:训练超大规模 AI 模型(如 GPT-4)和高精度科学模拟(如量子化学计算)。H100 的 NVLink 4.0 特别适合需要极高吞吐量的任务。挑战与突破:PAM4 的复杂性增加了设计难度,NVIDIA 通过优化信号处理和芯片布局,确保了高性能和可靠性。5、NVLink 5.0(2024):面向 exascale 计算GPU架构:Blackwell(B200)带宽:每链接 200 GB/秒(双向,100 GB/秒单向),B200 支持 18 个链接,总带宽 1.8 TB/秒。技术原理:进一步优化 PAM4 编码,通过提高时钟频率和信号调制效率,将单链接带宽翻倍。引入 NVLink-C2C(Chip-to-Chip)技术,支持与 Grace CPU 的高速连接,提供 900 GB/秒的 CPU-GPU 带宽。协议栈支持动态流量优先级,确保多种工作负载的平衡。软硬件架构:B200 GPU 使用 3nm 工艺,NVLink 端口采用高密度封装,支持更高的信号密度。GB200 NVL72 系统连接 72 个 Blackwell GPU,通过 NVSwitch 提供 130 TB/秒的内部带宽。CUDA 13.0 和 NCCL 2.12 优化了 exascale 级通信模式。技术演进亮点:带宽翻倍至 1.8 TB/s,搭配 Blackwell 架构的 GB200 NVL72,支持超大规模 AI 集群。应用场景:exascale 级别的 AI 和 HPC 任务,如气候建模、基因组分析和超大规模语言模型训练。NVLink-C2C 特别适合 CPU-GPU 协同计算。挑战与突破:高带宽和高链接数量增加了功耗和散热挑战,NVIDIA 通过先进的电源管理和冷却技术解决了这些问题。04、NVLink技术原理分析信号技术NVLink 的信号技术从 NRZ 进化到 PAM4。NRZ 每个时钟周期传输 1 位数据,而 PAM4 传输 2 位,通过四种电平表示 00、01、10、11。这使得在相同物理带宽下,数据传输率翻倍。PAM4 虽然对信噪比要求更高,但通过先进的纠错码(ECC)和信号调制技术,NVLink 4.0 及以后的版本成功实现了高可靠性的高速传输。协议栈NVLink 使用定制的协议栈,优化了数据包格式和传输机制。与 PCIe 相比,NVLink 的协议更精简,减少了开销,降低了延迟。协议支持多种流量类型,包括内存访问、I/O 操作和消息传递,确保了灵活性和高效性。NVLink 5.0 引入了动态流量优先级,允许根据工作负载需求调整带宽分配。缓存一致性NVLink 支持硬件级的缓存一致性,允许多个 GPU 共享统一的内存地址空间,而无需软件干预。这通过目录式缓存一致性协议实现,类似于多核 CPU 的设计。每个 GPU 维护自己的缓存,并通过 NVLink 广播或点对点通信来维护一致性。这种机制极大地简化了编程模型,提高了开发效率。软硬件架构硬件集成NVLink 接口直接集成在 GPU 芯片上,每个 GPU 拥有多个 NVLink 端口。端口数量和带宽随 GPU 型号而异。NVSwitch 作为交换矩阵,连接多个 GPU,形成全连接或部分连接的拓扑结构,确保任意两个 GPU 间都有直接或间接的高速路径。NVLink-C2C 技术将 CPU 和 GPU 连接,提供高带宽协同计算能力。软件支持NVIDIA 提供了丰富的软件栈来利用 NVLink:CUDA:提供cudaMemcpyPeer等API,支持GPU间直接内存拷贝。NCCL:优化了集体通信操作,如 all-reduce、broadcast,广泛用于分布式训练。Unified Memory:允许 CPU 和 GPU 共享内存,NVLink 提供高带宽支持,减少数据移动开销。演进亮点NVLink 1.0(2016):首次亮相于 Pascal 架构的 Tesla P100,提供 160 GB/s 总带宽,较 PCIe 3.0 x16(约 32 GB/s)提升数倍,奠定了多 GPU 互联基础。NVLink 2.0(2017):引入 NVSwitch,支持全连接拓扑,带宽增至 300 GB/s,广泛用于 DGX-1 系统。NVLink 3.0(2020):链接数翻倍至 12,带宽达 600 GB/s,搭配 A100 GPU,满足大模型训练需求。NVLink 4.0(2022):采用 PAM4 编码,链接数增至 18,总带宽 900 GB/s,H100 GPU 成为 HPC 标杆。NVLink 5.0(2024):带宽翻倍至 1.8 TB/s,搭配 Blackwell 架构的 GB200 NVL72,支持超大规模 AI 集群。NVLink 的演进反映了 NVIDIA 对计算规模和复杂性增长的精准应对。从最初的 GPU-GPU 互联,到如今支持 CPU-GPU 协同(如 Grace CPU),NVLink 已从单一技术成长为数据中心计算的核心支柱。05、应用场景:赋能AI与HPCNVLink 的高带宽和低延迟使其在以下领域大放异彩:人工智能与深度学习AI 模型(如大语言模型)需要处理海量参数和数据,单 GPU 内存和计算能力往往不足。NVLink 允许多 GPU 共享统一内存池,加速模型训练。例如,训练 GPT-3 规模的模型需数十 GB 参数,NVLink 确保 GPU 间快速交换梯度和权重,缩短训练时间。NVIDIA DGX A100(8 个 A100 GPU,NVLink 3.0)可将训练时间从数月缩短至数周。高性能计算(HPC)HPC 任务,如气候建模、分子动力学模拟,需处理大规模矩阵运算。NVLink 的高带宽减少数据传输瓶颈,提升计算效率。例如,美国橡树岭国家实验室的 Summit 超级计算机使用 IBM Power9 CPU 和 NVIDIA V100 GPU,通过 NVLink 2.0 实现高效互联,位列全球超算前列。数据科学与分析在数据密集型任务中,NVLink 加速多 GPU 协作处理。例如,金融风控模型需分析海量交易数据,NVLink 确保快速数据分发,缩短分析时间。云服务云服务商如 AWS(P4d 实例,A100 GPU)、Azure 和 Google Cloud 提供 NVLink 连接的 GPU 实例,允许用户按需租用高性能计算资源,无需自建硬件。例如,AWS P4d 实例使用 NVLink 3.0,支持多 GPU 训练和推理。06、生态布局:硬件、软件与合作伙伴NVLink 的成功不仅在于技术本身,还得益于 NVIDIA 构建的强大生态系统。硬件生态GPU与CPU:NVLink 支持 NVIDIA 全系列 GPU,从 Pascal 到 Blackwell。Grace CPU 通过 NVLink-C2C 与 GPU 实现高带宽连接,Grace Hopper 超级芯片更是将 CPU 和 GPU 集成于同一封装,提供超高性能。NVSwitch:NVSwitch 扩展了 NVLink 的连接能力,支持全连接拓扑。例如,DGX-2 使用 12 个 NVSwitch 连接 16 个 V100 GPU,GB200 NVL72 则连接 72 个 Blackwell GPU。DGX与HGX系统:DGX 系统(如 DGX A100、H100)是 NVLink 的旗舰平台,预配置多 GPU 和 NVSwitch,适合企业 AI 开发。HGX 平台则为服务器厂商提供灵活的 NVLink 集成方案。软件生态CUDA与 NCCL:CUDA 提供 NVLink 专用 API,简化多 GPU 数据传输。NCCL(NVIDIA 集体通信库)优化了多 GPU 通信模式,广泛用于 AI 框架。AI框架:TensorFlow、PyTorch 等主流框架支持 NVLink,开发者可无缝利用其高带宽特性。NVIDIA AI Enterprise:提供预优化模型和微服务(如 NIM),与 NVLink 硬件协同,提升 AI 部署效率。合作伙伴生态服务器厂商:Dell、HPE、Lenovo 等厂商推出 NVLink 服务器,满足企业需求。云服务商:AWS、Azure、Google Cloud 提供 NVLink 实例,降低用户进入门槛。超算中心:Summit、Perlmutter 等顶级超算采用 NVLink,验证其在极端计算中的可靠性。未来方向NVLink 的生态布局正向更广泛领域扩展。Grace CPU 和 Blackwell 架构的推出表明 NVIDIA 致力于构建 CPU-GPU 统一计算平台。未来,NVLink 或将融入 6G 网络、边缘计算等新兴领域,进一步推动计算架构创新。然而,开放标准如 UALink(支持 1,024 GPU,200 GT/s 带宽)可能对 NVLink 的专有性构成挑战,NVIDIA 需平衡技术领先与生态开放性。07、写在最后:NVLink的计算革命NVLink 从 2016 年的初代到 2024 年的第五代,已成为 AI 和 HPC 的核心技术。其高带宽、低延迟和缓存一致性特性,赋能了从云端到边缘的计算创新。无论是训练万亿参数的 AI 模型,还是运行复杂的科学模拟,NVLink 都提供了不可或缺的“数据动脉”。通过硬件、软件和合作伙伴的协同,NVIDIA 构建了强大的 NVLink 生态,为计算行业树立了标杆。未来,随着计算需求的持续增长,NVLink 无疑将继续引领技术前沿,驱动下一代计算革命。本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。原始发表:2025-04-29,如有侵权请联系 hegangben@163.com 删除

NVLink1.0~5.0: 高速互联的架构演进之路 01、引言:数据时代的“高速公路”在人工智能(AI)和高性能计算(HPC)的浪潮中,计算能力的提升不仅依赖于处理器性能,还需要高效的数据传输通道。传统 PCIe 互联虽广泛应用,但其带宽和延迟已难以满足现代计算需求。NVIDIA 的 NVLink 应运而生,作为一种高速、低延迟的点对点互联技术,它为多 GPU 和 CPU-GPU 系统提供了“数据高速公路”,显著提升了计算效率。本文将从技术视角深入剖析 NVLink 的架构、演进历程、应用场景及生态布局,为科技人士、通信工程师和学术研究者提供全面洞察。02、NVLink架构:技术核心与关键特性NVLink 是 NVIDIA 专为高性能计算设计的互联技术,旨在实现 GPU 间或 GPU 与 CPU 间的高速数据交换。其架构基于点对点通信,采用多通道设计,每个通道(称为“链接”)包含多个差分对,提供高带宽和低延迟的数据传输。核心特性高带宽:NVLink 提供远超 PCIe 的带宽。例如,最新 NVLink 5.0 单链接双向带宽达 200 GB/s,总带宽可达 1.8 TB/s,而 PCIe 5.0 x16 仅约 126 GB/s。低延迟:通过专用通道和优化协议,NVLink 显著降低数据传输延迟,适合实时计算任务。缓存一致性:NVLink 支持 GPU 间或 GPU-CPU 间的缓存一致性,允许共享统一内存空间,减少数据拷贝开销。可扩展性:结合 NVSwitch,NVLink 支持全连接拓扑,使多 GPU 系统实现高效通信。NVLink 的工作原理类似高速公路网络:每个 GPU 或 CPU 是“城市”,链接是“车道”,NVSwitch 则像“交通枢纽”,确保数据流畅无阻。这种设计特别适合需要大规模并行计算的场景,如 AI 模型训练和科学模拟。03、技术演进:从NVLink 1.0到5.0 的跨越NVLink 自 2016 年首次亮相以来,经历了五代技术迭代,每一代都针对计算需求的增长进行了优化。版本年份GPU 架构每链接带宽(双向,GB/s)链接数总带宽(GB/s)备注1.02016Pascal404160首代,Tesla P1002.02017Volta506300支持 NVSwitch,DGX-13.02020Ampere5012600A100 GPU,广泛用于云4.02022Hopper10018900H100 GPU,PAM4 编码5.02024Blackwell200181800GB200 NVL72,AI 优化以下是对其演进历程的详细分析,涵盖技术原理、软硬件架构及技术演进亮点。1、NVLink 1.0(2016):开创高速互联先河GPU架构:Pascal(Tesla P100)带宽:每链接 40 GB/秒(双向,20 GB/秒单向),P100 支持 4 个链接,总带宽 160 GB/秒。技术原理:采用 NRZ(非归零)信号编码,每个时钟周期传输 1 位数据。NVLink 使用差分对传输,包含 8 条子通道,每条子通道运行在 20 Gbps。协议栈基于定制的点对点通信,优化了数据包格式,减少了传输开销。软硬件软件架构:NVLink 1.0 直接集成在 P100 GPU 芯片上,每个链接占用专用硅片区域。软件方面,CUDA 7.0 引入了cudaMemcpyPeer API技术,支持GPU间直接内存拷贝,简化了多GPU编程。技术演进亮点:首次亮相于Pascal架构的Tesla P100,提供160GB/s总带宽,较PCIexpress 3.0x16(约32GB/s)提升数倍,奠定了多GPU互联基础。应用场景:主要用于早期深度学习任务,如图像识别模型(如 ResNet)的训练。DGX-1 系统首次采用 NVLink 1.0,连接 8 个 P100 GPU,奠定了多 GPU 系统的基础。挑战与突破:NVLink 1.0 的主要挑战是链接数量有限,仅支持 4 个链接,限制了多 GPU 系统的扩展性。NVIDIA 通过优化协议和硬件设计,确保了低延迟和高可靠性,为后续版本奠定了技术基础。2、NVLink 2.0(2017):引入 NVSwitch,扩展规模GPU架构:Volta(Tesla V100)带宽:每链接 50 GB/秒(双向,25 GB/秒单向),V100 支持 6 个链接,总带宽 300 GB/秒。技术原理:继续使用 NRZ 编码,但通过提高时钟频率和优化信号完整性,将单链接带宽提升 25%。引入 NVSwitch,一个高性能交换矩阵,支持全连接拓扑,允许多达 16 个 GPU 直接通信。NVSwitch 包含 18 个 NVLink 端口,每个端口提供 50 GB/秒带宽,总吞吐量达 900 GB/秒。软硬件架构:NVSwitch 作为独立芯片,集成在 DGX-2 系统,连接 16 个 V100 GPU。软件方面,CUDA 9.0 和 NCCL 2.0 优化了集体通信操作(如 all-reduce),提升了分布式训练效率。NVLink 2.0 支持缓存一致性,允许多 GPU 共享统一内存空间。技术演进亮点:引入 NVSwitch,支持全连接拓扑,带宽增至 300 GB/s,广泛用于 DGX-1 系统。应用场景:广泛用于 AI 研究和企业级应用,如自然语言处理(BERT 模型)和推荐系统训练。Summit 超级计算机(橡树岭国家实验室)采用 NVLink 2.0,连接 IBM Power9 CPU 和 V100 GPU,位列全球超算前列。挑战与突破:NVLink 2.0 解决了扩展性问题,但 NVSwitch 的引入增加了系统复杂性和成本。NVIDIA 通过优化交换矩阵设计和协议栈,确保了高吞吐量和低延迟。3、NVLink 3.0(2020):链接数量翻倍GPU架构:Ampere(A100)带宽:每链接 50 GB/秒(双向),A100 支持 12 个链接,总带宽 600 GB/秒。技术原理:维持 NRZ 编码,但通过增加链接数量(从 6 到 12),将总带宽翻倍。引入多实例 GPU(MIG)技术,允许将 A100 GPU 虚拟化为多个独立实例,每个实例可分配 NVLink 链接,提升资源利用率。协议栈进一步优化,支持更高效的缓存一致性。软硬件架构:A100 GPU 的 NVLink 端口集成在芯片边缘,采用高密度封装技术。DGX A100 系统使用 8 个 A100 GPU,通过 NVSwitch 连接,提供 4.8 TB/秒的内部带宽。CUDA 11.0 和 NCCL 2.7 增强了对 NVLink 3.0 的支持,优化了分布式训练和推理。技术演进亮点:链接数翻倍至 12,带宽达 600 GB/s,搭配 A100 GPU,满足大模型训练需求。应用场景:云服务(如 AWS P4d 实例)、AI 训练和推理,以及 HPC 任务(如分子动力学模拟)。A100 的 MIG 功能特别适合云端多租户环境。挑战与突破:链接数量的增加提高了芯片设计复杂性,NVIDIA 通过先进的硅片布局和信号完整性技术解决了这一问题。MIG 技术的引入进一步提升了灵活性。4、NVLink 4.0(2022):PAM4 信号革命GPU架构:Hopper(H100)带宽:每链接 100 GB/秒(双向,50 GB/秒单向),H100 支持 18 个链接,总带宽 900 GB/秒。技术原理:首次采用 PAM4(4 级脉冲幅度调制)信号编码,每个时钟周期传输 2 位数据,较 NRZ 翻倍数据率。PAM4 要求更高的信噪比,NVIDIA 通过先进的纠错码(ECC)和信号调制技术确保可靠性。协议栈优化了流量管理,支持动态带宽分配。软硬件架构:H100 GPU 使用 TSMC 4nm 工艺,NVLink 端口数量增至 18,集成在芯片边缘的高速 I/O 区域。DGX H100 系统通过 NVSwitch 连接 8 个 H100 GPU,提供 7.2 TB/秒的内部带宽。CUDA 12.0 和 NCCL 2.10 引入了新的通信原语,优化了超大规模模型训练。技术演进亮点:采用 PAM4 编码,链接数增至 18,总带宽 900 GB/s,H100 GPU 成为 HPC 标杆。应用场景:训练超大规模 AI 模型(如 GPT-4)和高精度科学模拟(如量子化学计算)。H100 的 NVLink 4.0 特别适合需要极高吞吐量的任务。挑战与突破:PAM4 的复杂性增加了设计难度,NVIDIA 通过优化信号处理和芯片布局,确保了高性能和可靠性。5、NVLink 5.0(2024):面向 exascale 计算GPU架构:Blackwell(B200)带宽:每链接 200 GB/秒(双向,100 GB/秒单向),B200 支持 18 个链接,总带宽 1.8 TB/秒。技术原理:进一步优化 PAM4 编码,通过提高时钟频率和信号调制效率,将单链接带宽翻倍。引入 NVLink-C2C(Chip-to-Chip)技术,支持与 Grace CPU 的高速连接,提供 900 GB/秒的 CPU-GPU 带宽。协议栈支持动态流量优先级,确保多种工作负载的平衡。软硬件架构:B200 GPU 使用 3nm 工艺,NVLink 端口采用高密度封装,支持更高的信号密度。GB200 NVL72 系统连接 72 个 Blackwell GPU,通过 NVSwitch 提供 130 TB/秒的内部带宽。CUDA 13.0 和 NCCL 2.12 优化了 exascale 级通信模式。技术演进亮点:带宽翻倍至 1.8 TB/s,搭配 Blackwell 架构的 GB200 NVL72,支持超大规模 AI 集群。应用场景:exascale 级别的 AI 和 HPC 任务,如气候建模、基因组分析和超大规模语言模型训练。NVLink-C2C 特别适合 CPU-GPU 协同计算。挑战与突破:高带宽和高链接数量增加了功耗和散热挑战,NVIDIA 通过先进的电源管理和冷却技术解决了这些问题。04、NVLink技术原理分析信号技术NVLink 的信号技术从 NRZ 进化到 PAM4。NRZ 每个时钟周期传输 1 位数据,而 PAM4 传输 2 位,通过四种电平表示 00、01、10、11。这使得在相同物理带宽下,数据传输率翻倍。PAM4 虽然对信噪比要求更高,但通过先进的纠错码(ECC)和信号调制技术,NVLink 4.0 及以后的版本成功实现了高可靠性的高速传输。协议栈NVLink 使用定制的协议栈,优化了数据包格式和传输机制。与 PCIe 相比,NVLink 的协议更精简,减少了开销,降低了延迟。协议支持多种流量类型,包括内存访问、I/O 操作和消息传递,确保了灵活性和高效性。NVLink 5.0 引入了动态流量优先级,允许根据工作负载需求调整带宽分配。缓存一致性NVLink 支持硬件级的缓存一致性,允许多个 GPU 共享统一的内存地址空间,而无需软件干预。这通过目录式缓存一致性协议实现,类似于多核 CPU 的设计。每个 GPU 维护自己的缓存,并通过 NVLink 广播或点对点通信来维护一致性。这种机制极大地简化了编程模型,提高了开发效率。软硬件架构硬件集成NVLink 接口直接集成在 GPU 芯片上,每个 GPU 拥有多个 NVLink 端口。端口数量和带宽随 GPU 型号而异。NVSwitch 作为交换矩阵,连接多个 GPU,形成全连接或部分连接的拓扑结构,确保任意两个 GPU 间都有直接或间接的高速路径。NVLink-C2C 技术将 CPU 和 GPU 连接,提供高带宽协同计算能力。软件支持NVIDIA 提供了丰富的软件栈来利用 NVLink:CUDA:提供cudaMemcpyPeer等API,支持GPU间直接内存拷贝。NCCL:优化了集体通信操作,如 all-reduce、broadcast,广泛用于分布式训练。Unified Memory:允许 CPU 和 GPU 共享内存,NVLink 提供高带宽支持,减少数据移动开销。演进亮点NVLink 1.0(2016):首次亮相于 Pascal 架构的 Tesla P100,提供 160 GB/s 总带宽,较 PCIe 3.0 x16(约 32 GB/s)提升数倍,奠定了多 GPU 互联基础。NVLink 2.0(2017):引入 NVSwitch,支持全连接拓扑,带宽增至 300 GB/s,广泛用于 DGX-1 系统。NVLink 3.0(2020):链接数翻倍至 12,带宽达 600 GB/s,搭配 A100 GPU,满足大模型训练需求。NVLink 4.0(2022):采用 PAM4 编码,链接数增至 18,总带宽 900 GB/s,H100 GPU 成为 HPC 标杆。NVLink 5.0(2024):带宽翻倍至 1.8 TB/s,搭配 Blackwell 架构的 GB200 NVL72,支持超大规模 AI 集群。NVLink 的演进反映了 NVIDIA 对计算规模和复杂性增长的精准应对。从最初的 GPU-GPU 互联,到如今支持 CPU-GPU 协同(如 Grace CPU),NVLink 已从单一技术成长为数据中心计算的核心支柱。05、应用场景:赋能AI与HPCNVLink 的高带宽和低延迟使其在以下领域大放异彩:人工智能与深度学习AI 模型(如大语言模型)需要处理海量参数和数据,单 GPU 内存和计算能力往往不足。NVLink 允许多 GPU 共享统一内存池,加速模型训练。例如,训练 GPT-3 规模的模型需数十 GB 参数,NVLink 确保 GPU 间快速交换梯度和权重,缩短训练时间。NVIDIA DGX A100(8 个 A100 GPU,NVLink 3.0)可将训练时间从数月缩短至数周。高性能计算(HPC)HPC 任务,如气候建模、分子动力学模拟,需处理大规模矩阵运算。NVLink 的高带宽减少数据传输瓶颈,提升计算效率。例如,美国橡树岭国家实验室的 Summit 超级计算机使用 IBM Power9 CPU 和 NVIDIA V100 GPU,通过 NVLink 2.0 实现高效互联,位列全球超算前列。数据科学与分析在数据密集型任务中,NVLink 加速多 GPU 协作处理。例如,金融风控模型需分析海量交易数据,NVLink 确保快速数据分发,缩短分析时间。云服务云服务商如 AWS(P4d 实例,A100 GPU)、Azure 和 Google Cloud 提供 NVLink 连接的 GPU 实例,允许用户按需租用高性能计算资源,无需自建硬件。例如,AWS P4d 实例使用 NVLink 3.0,支持多 GPU 训练和推理。06、生态布局:硬件、软件与合作伙伴NVLink 的成功不仅在于技术本身,还得益于 NVIDIA 构建的强大生态系统。硬件生态GPU与CPU:NVLink 支持 NVIDIA 全系列 GPU,从 Pascal 到 Blackwell。Grace CPU 通过 NVLink-C2C 与 GPU 实现高带宽连接,Grace Hopper 超级芯片更是将 CPU 和 GPU 集成于同一封装,提供超高性能。NVSwitch:NVSwitch 扩展了 NVLink 的连接能力,支持全连接拓扑。例如,DGX-2 使用 12 个 NVSwitch 连接 16 个 V100 GPU,GB200 NVL72 则连接 72 个 Blackwell GPU。DGX与HGX系统:DGX 系统(如 DGX A100、H100)是 NVLink 的旗舰平台,预配置多 GPU 和 NVSwitch,适合企业 AI 开发。HGX 平台则为服务器厂商提供灵活的 NVLink 集成方案。软件生态CUDA与 NCCL:CUDA 提供 NVLink 专用 API,简化多 GPU 数据传输。NCCL(NVIDIA 集体通信库)优化了多 GPU 通信模式,广泛用于 AI 框架。AI框架:TensorFlow、PyTorch 等主流框架支持 NVLink,开发者可无缝利用其高带宽特性。NVIDIA AI Enterprise:提供预优化模型和微服务(如 NIM),与 NVLink 硬件协同,提升 AI 部署效率。合作伙伴生态服务器厂商:Dell、HPE、Lenovo 等厂商推出 NVLink 服务器,满足企业需求。云服务商:AWS、Azure、Google Cloud 提供 NVLink 实例,降低用户进入门槛。超算中心:Summit、Perlmutter 等顶级超算采用 NVLink,验证其在极端计算中的可靠性。未来方向NVLink 的生态布局正向更广泛领域扩展。Grace CPU 和 Blackwell 架构的推出表明 NVIDIA 致力于构建 CPU-GPU 统一计算平台。未来,NVLink 或将融入 6G 网络、边缘计算等新兴领域,进一步推动计算架构创新。然而,开放标准如 UALink(支持 1,024 GPU,200 GT/s 带宽)可能对 NVLink 的专有性构成挑战,NVIDIA 需平衡技术领先与生态开放性。07、写在最后:NVLink的计算革命NVLink 从 2016 年的初代到 2024 年的第五代,已成为 AI 和 HPC 的核心技术。其高带宽、低延迟和缓存一致性特性,赋能了从云端到边缘的计算创新。无论是训练万亿参数的 AI 模型,还是运行复杂的科学模拟,NVLink 都提供了不可或缺的“数据动脉”。通过硬件、软件和合作伙伴的协同,NVIDIA 构建了强大的 NVLink 生态,为计算行业树立了标杆。未来,随着计算需求的持续增长,NVLink 无疑将继续引领技术前沿,驱动下一代计算革命。本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。原始发表:2025-04-29,如有侵权请联系 hegangben@163.com 删除