搜索到

344

篇与

的结果

-

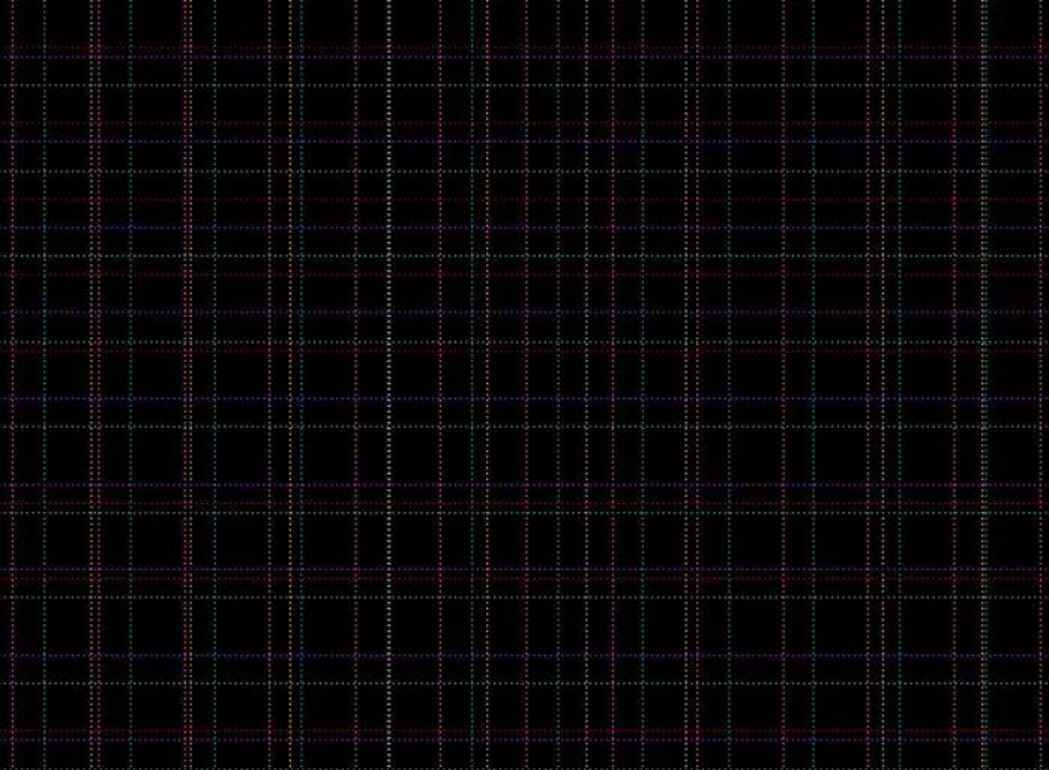

数字后端基本概念介绍——Track The basic concept of the digital backend that I want to introduce to you today is Track. Track refers to the trace track, which, like row, can constrain the direction of the trace device. The signal line usually has to be on the track. The height of an std cell is usually expressed by metal2 track pitch. The commonly used std cell libraries are 7T / 9T / 12T, which are distinguished by track. 9T means that nine lines can be walked within the height range of an std cell, so generally speaking, the size of a 7T cell is the smallest, and the size of a 9T cell is slightly larger. big.The colorful lines in the figure below are the track traces defined on each layer.Usually we define the attributes of track in the technology lef of design, as shown in the figure below:LAYER M1TYPE ROUTING ;DIRECTION VERTICAL ;PITCH 0.090 0.064;OFFSET 0.000 0.000;MAXWIDTH 2 ;WIDTH 0.032 ;In the definition of M1 layer above, TYPE ROUTING means that this is a routing layer. We have other types including Implant, Masterslice, etc.The direction represents the direction of the metal prefer routing of this layer. It is worth noting here that each layer of track will be divided into pref track and non-pref track. The pref track is the mainstream routing direction on this layer, and the remaining non-pref track is the non-mainstream direction. Therefore, the mainstream routing direction in the above example is vertical (vertical), and the non-mainstream is horizontal (honrizontal). usually. The wire that takes the non-pref track will be wider, which will take up more winding resources. Therefore, it is generally not recommended to use non-pref track. Especially in the design of advanced processes, winding resources are extremely tight, and non-pref track is generally rarely used.PITCH IS the SPACING BETWEEN EACH track. In the above example, the vertical spacing is 0.09 and the horizontal spacing is 0.064.OFFSET is the distance from the starting point of the first trackWIDTH represents the default width of the wire on this layer, and MAXWIDTH represents the maximum width that cannot be exceeded.

数字后端基本概念介绍——Track The basic concept of the digital backend that I want to introduce to you today is Track. Track refers to the trace track, which, like row, can constrain the direction of the trace device. The signal line usually has to be on the track. The height of an std cell is usually expressed by metal2 track pitch. The commonly used std cell libraries are 7T / 9T / 12T, which are distinguished by track. 9T means that nine lines can be walked within the height range of an std cell, so generally speaking, the size of a 7T cell is the smallest, and the size of a 9T cell is slightly larger. big.The colorful lines in the figure below are the track traces defined on each layer.Usually we define the attributes of track in the technology lef of design, as shown in the figure below:LAYER M1TYPE ROUTING ;DIRECTION VERTICAL ;PITCH 0.090 0.064;OFFSET 0.000 0.000;MAXWIDTH 2 ;WIDTH 0.032 ;In the definition of M1 layer above, TYPE ROUTING means that this is a routing layer. We have other types including Implant, Masterslice, etc.The direction represents the direction of the metal prefer routing of this layer. It is worth noting here that each layer of track will be divided into pref track and non-pref track. The pref track is the mainstream routing direction on this layer, and the remaining non-pref track is the non-mainstream direction. Therefore, the mainstream routing direction in the above example is vertical (vertical), and the non-mainstream is horizontal (honrizontal). usually. The wire that takes the non-pref track will be wider, which will take up more winding resources. Therefore, it is generally not recommended to use non-pref track. Especially in the design of advanced processes, winding resources are extremely tight, and non-pref track is generally rarely used.PITCH IS the SPACING BETWEEN EACH track. In the above example, the vertical spacing is 0.09 and the horizontal spacing is 0.064.OFFSET is the distance from the starting point of the first trackWIDTH represents the default width of the wire on this layer, and MAXWIDTH represents the maximum width that cannot be exceeded. -

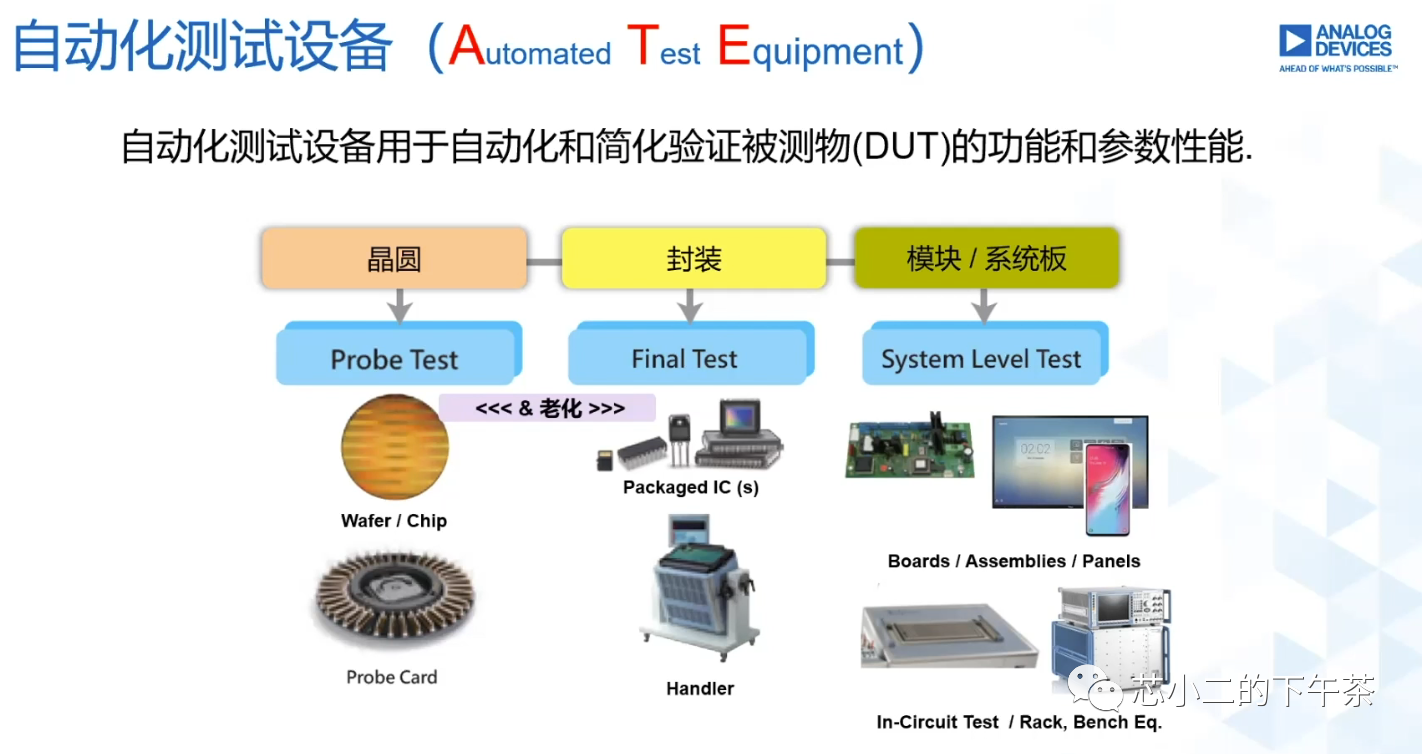

谈谈CP和FT测试 关于CP和FT的测试,我本来以为这个话题已经是业界常识,不需要专门再谈了.不过前几天和一个设计公司的主管交流了一下,发现其实很多非测试专业的从业人员对这两个概念其实了解并不像我以为的那样深刻.所以,我还是有必要在这里再谈一下按照国际惯例,首先需要再解释一下什么是CP和FT测试.CP是(ChipProbe)的缩写,指的是芯片在wafer的阶段,就通过探针卡扎到芯片管脚上对芯片进行性能及功能测试,有时候这道工序也被称作WS(WaferSort);而FT是Final Test的缩写,指的是芯片在封装完成以后进行的最终测试,只有通过测试的芯片才会被出货由于测试治具上的差异,CP和FT的不同点并不仅仅限于所处的工序阶段不同,两者在效率和功能覆盖上都有着明显的差异,这些信息是每一个IC从业人员需要基本了解的在绝大多数情况下,特别是在国内,我们目前在CP测试上选用的探针都还是悬臂针(也有叫环氧针的,因为针是用环氧树脂固定的缘故).这种类型的针比较长,而且是悬空的,信号完整性控制上非常困难,所以一般数据的最高传输率只有100~400Mbps,高速信号的测试是几乎不可能的;另外,探针和pad的直接接触在电气性能上也有局限,容易产生漏电和接触电阻,这对于高精度的信号测量也会带来巨大的影响.所以,通常CP测试仅仅用于基本的连接测试和低速的数字电路测试当然,理论上在CP阶段也可以进行高速信号和高精度信号的测试,但这往往需要采用专业的高速探针方案,如垂直针/MEMS探针等技术,这会大大增加硬件的成本.多数情况下,这在经济角度上来说是不合算的那这样一来,我们还需不需要CP测试?或者在CP测试阶段如何对具体测试项目进行取舍呢?要回答这个问题,我们就必须对CP的目的有深刻的理解.那CP的目的究竟是什么呢?首先,CP最大的目的就是确保在芯片封装前,尽可能地把坏的芯片筛选出来以节约封装费用.所以基于这个认识,在CP测试阶段,尽可能只选择那些对良率影响较大的测试项目,一些测试难度大,成本高但fail率不高的测试项目,完全可以放到FT阶段再测试.这些项目在CP阶段测试意义不大,只会增加测试的成本.要知道,增加一个复杂的高速或高精度模拟测试,不仅仅会增加治具的成本,还会增加测试机台的费率和增加测试时间.这些测试项目在FT阶段都是要测试的,所以没有必要放在CP阶段重复进行了其次,一些芯片的部分模组地管脚在封装的时候是不会引出来了,也就是说在FT阶段这些模组很难甚至无法测量.在这样的情况下,测试就必须在CP阶段进行.这也是必须进行CP测试的一个重要原因还有一种特殊情况,芯片的封装是SIP之类的特殊形式.一方面这种封装形式在FT阶段可测性较低,而且多芯片合封的情况下,整体良率受每颗die的良率影响较大,所以一般需要在封装前确保每颗die都是好品(KGD: Known Good Die).这种情况下,往往无论多困难,都需要在CP阶段把所有测试项目都测一遍了所以,基于以上的认识,我们就比较容易在具体项目中判断CP测试项目的取舍了.简单而言:1)因为封装本身可能影响芯片的良率和特性,所以芯片所有可测测试项目都是必须在FT阶段测试一遍的.而CP阶段则是可选2)CP阶段原则上只测一些基本的DC,低速数字电路的功能,以及其它一些容易测试或者必须测试的项目.凡是在FT阶段可以测试,在CP阶段难于测试的项目,能不测就尽量不测.一些类似ADC的测试,在CP阶段可以只给几个DC电平,确认ADC能够基本工作.在FT阶段再确认具体的SNR/THD等指标3)由于CP阶段的测试精度往往不够准确,可以适当放宽测试判断标准,只做初步筛选.精细严格的测试放到FT阶段4)如果封装成本不大,且芯片本身良率已经比较高.可以考虑不做CP测试,或者CP阶段只做抽样测试,监督工艺5)新的产品导入量产,应该先完成FT测试程序的开发核导入.在产品量产初期,FT远远比CP重要.等产品逐渐上量以后,可以再根据FT的实际情况,制定和开发CP测试以上只是根据我个人的经验总结的一些最基本的CP/FT测试常识.事实上,在具体的项目中,会有很多复杂的问题出现,这些问题的对应和解决不是我短短一篇文章所能全部覆盖到的.本文的作用只是给广大非测试专业的从业人员提供一些最基本的概念信息.在实际的案例中,往往需要具体问题具体分析.总而言之,对于任何一家设计公司而言,优秀的测试工程师或团队是确保产品良率和成本控制币不可少的因素

谈谈CP和FT测试 关于CP和FT的测试,我本来以为这个话题已经是业界常识,不需要专门再谈了.不过前几天和一个设计公司的主管交流了一下,发现其实很多非测试专业的从业人员对这两个概念其实了解并不像我以为的那样深刻.所以,我还是有必要在这里再谈一下按照国际惯例,首先需要再解释一下什么是CP和FT测试.CP是(ChipProbe)的缩写,指的是芯片在wafer的阶段,就通过探针卡扎到芯片管脚上对芯片进行性能及功能测试,有时候这道工序也被称作WS(WaferSort);而FT是Final Test的缩写,指的是芯片在封装完成以后进行的最终测试,只有通过测试的芯片才会被出货由于测试治具上的差异,CP和FT的不同点并不仅仅限于所处的工序阶段不同,两者在效率和功能覆盖上都有着明显的差异,这些信息是每一个IC从业人员需要基本了解的在绝大多数情况下,特别是在国内,我们目前在CP测试上选用的探针都还是悬臂针(也有叫环氧针的,因为针是用环氧树脂固定的缘故).这种类型的针比较长,而且是悬空的,信号完整性控制上非常困难,所以一般数据的最高传输率只有100~400Mbps,高速信号的测试是几乎不可能的;另外,探针和pad的直接接触在电气性能上也有局限,容易产生漏电和接触电阻,这对于高精度的信号测量也会带来巨大的影响.所以,通常CP测试仅仅用于基本的连接测试和低速的数字电路测试当然,理论上在CP阶段也可以进行高速信号和高精度信号的测试,但这往往需要采用专业的高速探针方案,如垂直针/MEMS探针等技术,这会大大增加硬件的成本.多数情况下,这在经济角度上来说是不合算的那这样一来,我们还需不需要CP测试?或者在CP测试阶段如何对具体测试项目进行取舍呢?要回答这个问题,我们就必须对CP的目的有深刻的理解.那CP的目的究竟是什么呢?首先,CP最大的目的就是确保在芯片封装前,尽可能地把坏的芯片筛选出来以节约封装费用.所以基于这个认识,在CP测试阶段,尽可能只选择那些对良率影响较大的测试项目,一些测试难度大,成本高但fail率不高的测试项目,完全可以放到FT阶段再测试.这些项目在CP阶段测试意义不大,只会增加测试的成本.要知道,增加一个复杂的高速或高精度模拟测试,不仅仅会增加治具的成本,还会增加测试机台的费率和增加测试时间.这些测试项目在FT阶段都是要测试的,所以没有必要放在CP阶段重复进行了其次,一些芯片的部分模组地管脚在封装的时候是不会引出来了,也就是说在FT阶段这些模组很难甚至无法测量.在这样的情况下,测试就必须在CP阶段进行.这也是必须进行CP测试的一个重要原因还有一种特殊情况,芯片的封装是SIP之类的特殊形式.一方面这种封装形式在FT阶段可测性较低,而且多芯片合封的情况下,整体良率受每颗die的良率影响较大,所以一般需要在封装前确保每颗die都是好品(KGD: Known Good Die).这种情况下,往往无论多困难,都需要在CP阶段把所有测试项目都测一遍了所以,基于以上的认识,我们就比较容易在具体项目中判断CP测试项目的取舍了.简单而言:1)因为封装本身可能影响芯片的良率和特性,所以芯片所有可测测试项目都是必须在FT阶段测试一遍的.而CP阶段则是可选2)CP阶段原则上只测一些基本的DC,低速数字电路的功能,以及其它一些容易测试或者必须测试的项目.凡是在FT阶段可以测试,在CP阶段难于测试的项目,能不测就尽量不测.一些类似ADC的测试,在CP阶段可以只给几个DC电平,确认ADC能够基本工作.在FT阶段再确认具体的SNR/THD等指标3)由于CP阶段的测试精度往往不够准确,可以适当放宽测试判断标准,只做初步筛选.精细严格的测试放到FT阶段4)如果封装成本不大,且芯片本身良率已经比较高.可以考虑不做CP测试,或者CP阶段只做抽样测试,监督工艺5)新的产品导入量产,应该先完成FT测试程序的开发核导入.在产品量产初期,FT远远比CP重要.等产品逐渐上量以后,可以再根据FT的实际情况,制定和开发CP测试以上只是根据我个人的经验总结的一些最基本的CP/FT测试常识.事实上,在具体的项目中,会有很多复杂的问题出现,这些问题的对应和解决不是我短短一篇文章所能全部覆盖到的.本文的作用只是给广大非测试专业的从业人员提供一些最基本的概念信息.在实际的案例中,往往需要具体问题具体分析.总而言之,对于任何一家设计公司而言,优秀的测试工程师或团队是确保产品良率和成本控制币不可少的因素 -

-

关于SO、SOP、SOIC封装(宽体、中体、窄体)的详解 SOP( Small Outline Package )小外形封装,指鸥翼形 (L 形 )引线从封装的两个侧面引出的一 种表面贴装型封装。 1968 ~ 1969 年飞利浦公司就开发出小外形封装( SOP)。以后逐渐派生出 SOJ( J 型引脚小 外形封装) 、TSOP(薄小外形封装) 、VSOP (甚小外形封装) 、SSOP(缩小型 SOP)、TSSOP(薄 的缩小型 SOP)及 SOT(小外形晶体管) 、 SOIC (小外形集成电路)等。在引脚数量不超过 40 的领域, SOP 是普及最广的表面贴装封装,典型引脚中心距 1.27mm(50mil) ,其它有 0.65mm 、 0.5mm ;引脚数多为 8~ 32;装配高度不到 1.27mm 的 SOP 也称为 TSOP 。表 1、常用缩写代码含义二、宽体、中体、窄体以及 SO、SOP、SOIC之争。在事实上,针对 SOIC 封装的尺寸标准,不同的厂家分别或同时遵循了两种不同的标准 JEDEC (美国联合电子设备工程委员会)和 EIAJ (日本电子机械工业协会),结果就导致了“宽体、中体和窄体”三个分支概念的出现,把很多人搞得晕头转向,也激起很多砖家在“宽体、中体、窄体以及 SO、SOP、SOIC ”几个概念之间争得死去活来。 还有许多来自不同半导体制造商的封装不属于上述标准。 另外, JEDEC 和 EIAJ 这两种标准 的名称也并非总是被用于制造商的产品目录和数据表中,除此以外,不同制造商之间的描述系 统也不统一。 其实,静下心来,仔细看一下两个封装标准,再对比几种常见的元件尺寸,不难发现,规律其实并不复杂:1、 单从字面上理解,其实 SO=SOP=SOIC 。2、 混乱现象主要出现在管脚间距 1.27mm 的封装上,多为 74 系列的数字逻辑芯片。3、 两个标准对代码缩写各有自己的习惯:EIAJ 习惯上使用 SOP( 5.3mm 体宽);JEDEC 习惯上使用 SOIC ( 3.9mm 与 7.5mm 两种体宽);也有些公司并不遵守这个习惯,如 UTC ,使用 SOP( 3.9mm 与 7.5mm 两种体宽);另有很多制造商使用 SO、 DSO、 SOL 等。4、 两个标准规定的尺寸不同,互不兼容,其差异主要体现在宽度 WB 和 WL 上,下表给出了常用 SOP 封装在两个标准下的 WB 与 WL 值:表 2、 SOP 封装在 JEDEC 和 EIAJ 标准下的尺寸差异其中 WB 与 WL 的含义如下:名词解释它们之间主要有两点区别:相邻引脚中心间距;相对引脚中心间距。8-pin plastic SOP

关于SO、SOP、SOIC封装(宽体、中体、窄体)的详解 SOP( Small Outline Package )小外形封装,指鸥翼形 (L 形 )引线从封装的两个侧面引出的一 种表面贴装型封装。 1968 ~ 1969 年飞利浦公司就开发出小外形封装( SOP)。以后逐渐派生出 SOJ( J 型引脚小 外形封装) 、TSOP(薄小外形封装) 、VSOP (甚小外形封装) 、SSOP(缩小型 SOP)、TSSOP(薄 的缩小型 SOP)及 SOT(小外形晶体管) 、 SOIC (小外形集成电路)等。在引脚数量不超过 40 的领域, SOP 是普及最广的表面贴装封装,典型引脚中心距 1.27mm(50mil) ,其它有 0.65mm 、 0.5mm ;引脚数多为 8~ 32;装配高度不到 1.27mm 的 SOP 也称为 TSOP 。表 1、常用缩写代码含义二、宽体、中体、窄体以及 SO、SOP、SOIC之争。在事实上,针对 SOIC 封装的尺寸标准,不同的厂家分别或同时遵循了两种不同的标准 JEDEC (美国联合电子设备工程委员会)和 EIAJ (日本电子机械工业协会),结果就导致了“宽体、中体和窄体”三个分支概念的出现,把很多人搞得晕头转向,也激起很多砖家在“宽体、中体、窄体以及 SO、SOP、SOIC ”几个概念之间争得死去活来。 还有许多来自不同半导体制造商的封装不属于上述标准。 另外, JEDEC 和 EIAJ 这两种标准 的名称也并非总是被用于制造商的产品目录和数据表中,除此以外,不同制造商之间的描述系 统也不统一。 其实,静下心来,仔细看一下两个封装标准,再对比几种常见的元件尺寸,不难发现,规律其实并不复杂:1、 单从字面上理解,其实 SO=SOP=SOIC 。2、 混乱现象主要出现在管脚间距 1.27mm 的封装上,多为 74 系列的数字逻辑芯片。3、 两个标准对代码缩写各有自己的习惯:EIAJ 习惯上使用 SOP( 5.3mm 体宽);JEDEC 习惯上使用 SOIC ( 3.9mm 与 7.5mm 两种体宽);也有些公司并不遵守这个习惯,如 UTC ,使用 SOP( 3.9mm 与 7.5mm 两种体宽);另有很多制造商使用 SO、 DSO、 SOL 等。4、 两个标准规定的尺寸不同,互不兼容,其差异主要体现在宽度 WB 和 WL 上,下表给出了常用 SOP 封装在两个标准下的 WB 与 WL 值:表 2、 SOP 封装在 JEDEC 和 EIAJ 标准下的尺寸差异其中 WB 与 WL 的含义如下:名词解释它们之间主要有两点区别:相邻引脚中心间距;相对引脚中心间距。8-pin plastic SOP -

typecho 网页系统jeo 主题新增分页及其下载 效果1.在主题的public文件夹下新建文件pagination.php,文件内容如下:<?php if ($this->options->JPageStatus === 'default') : ?> <?php $this->pageNav( '<svg class="icon icon-prev" viewBox="0 0 1024 1024" xmlns="http://www.w3.org/2000/svg" width="12" height="12"><path d="M822.272 146.944l-396.8 396.8c-19.456 19.456-51.2 19.456-70.656 0-18.944-19.456-18.944-51.2 0-70.656l396.8-396.8c19.456-19.456 51.2-19.456 70.656 0 18.944 19.456 18.944 45.056 0 70.656z"/><path d="M745.472 940.544l-396.8-396.8c-19.456-19.456-19.456-51.2 0-70.656 19.456-19.456 51.2-19.456 70.656 0l403.456 390.144c19.456 25.6 19.456 51.2 0 76.8-26.112 19.968-51.712 19.968-77.312.512zm-564.224-63.488c0-3.584 0-7.68.512-11.264h-.512v-714.24h.512c-.512-3.584-.512-7.168-.512-11.264 0-43.008 21.504-78.336 48.128-78.336s48.128 34.816 48.128 78.336c0 3.584 0 7.68-.512 11.264h.512v714.24h-.512c.512 3.584.512 7.168.512 11.264 0 43.008-21.504 78.336-48.128 78.336s-48.128-35.328-48.128-78.336z"/></svg>', '<svg class="icon icon-next" viewBox="0 0 1024 1024" xmlns="http://www.w3.org/2000/svg" width="12" height="12"><path d="M822.272 146.944l-396.8 396.8c-19.456 19.456-51.2 19.456-70.656 0-18.944-19.456-18.944-51.2 0-70.656l396.8-396.8c19.456-19.456 51.2-19.456 70.656 0 18.944 19.456 18.944 45.056 0 70.656z"/><path d="M745.472 940.544l-396.8-396.8c-19.456-19.456-19.456-51.2 0-70.656 19.456-19.456 51.2-19.456 70.656 0l403.456 390.144c19.456 25.6 19.456 51.2 0 76.8-26.112 19.968-51.712 19.968-77.312.512zm-564.224-63.488c0-3.584 0-7.68.512-11.264h-.512v-714.24h.512c-.512-3.584-.512-7.168-.512-11.264 0-43.008 21.504-78.336 48.128-78.336s48.128 34.816 48.128 78.336c0 3.584 0 7.68-.512 11.264h.512v714.24h-.512c.512 3.584.512 7.168.512 11.264 0 43.008-21.504 78.336-48.128 78.336s-48.128-35.328-48.128-78.336z"/></svg>', 1, '...', array( 'wrapTag' => 'ul', 'wrapClass' => 'joe_pagination', 'itemTag' => 'li', 'textTag' => 'a', 'currentClass' => 'active', 'prevClass' => 'prev', 'nextClass' => 'next' ) ); ?> <?php else : ?> <div class="joe_load">查看更多</div> <?php endif ?>修改主题目录下的index.php,添加如下代码,注意:此代码需添加在joe.index.min.js文件引入之前。<script> document.addEventListener('DOMContentLoaded', () => { window.Joe.PAGE_INDEX = '<?php echo $this->_currentPage; ?>' || 1; }); </script>在index.php中找到<div class="joe_load">查看更多</div>替换为<?php $this->need('public/pagination.php'); ?> 在主题目录下的functions.php文件中增加下面的代码,用于后台设置,这里默认的使用按钮切换形式,如果需求默认为点击加载形式可以将下面第四行的default改为ajax。$JPageStatus = new Typecho_Widget_Helper_Form_Element_Select( 'JPageStatus', array('default' => '按钮切换形式(默认)', 'ajax' => '点击加载形式'), 'default', '选择首页的分页形式', '介绍:选择一款您所喜欢的分页形式' ); $JPageStatus->setAttribute('class', 'joe_content joe_other'); $form->addInput($JPageStatus->multiMode());最后就是修改JS文件,找到主题目录下/assets/js/joe.index.min.js,将page:1替换为page:window.Joe.PAGE_INDEX还需要先恢复默认主题,或者其他主题然后再切换到jeo主题,主要是需要清除主题的缓存,不然不会看到效果

typecho 网页系统jeo 主题新增分页及其下载 效果1.在主题的public文件夹下新建文件pagination.php,文件内容如下:<?php if ($this->options->JPageStatus === 'default') : ?> <?php $this->pageNav( '<svg class="icon icon-prev" viewBox="0 0 1024 1024" xmlns="http://www.w3.org/2000/svg" width="12" height="12"><path d="M822.272 146.944l-396.8 396.8c-19.456 19.456-51.2 19.456-70.656 0-18.944-19.456-18.944-51.2 0-70.656l396.8-396.8c19.456-19.456 51.2-19.456 70.656 0 18.944 19.456 18.944 45.056 0 70.656z"/><path d="M745.472 940.544l-396.8-396.8c-19.456-19.456-19.456-51.2 0-70.656 19.456-19.456 51.2-19.456 70.656 0l403.456 390.144c19.456 25.6 19.456 51.2 0 76.8-26.112 19.968-51.712 19.968-77.312.512zm-564.224-63.488c0-3.584 0-7.68.512-11.264h-.512v-714.24h.512c-.512-3.584-.512-7.168-.512-11.264 0-43.008 21.504-78.336 48.128-78.336s48.128 34.816 48.128 78.336c0 3.584 0 7.68-.512 11.264h.512v714.24h-.512c.512 3.584.512 7.168.512 11.264 0 43.008-21.504 78.336-48.128 78.336s-48.128-35.328-48.128-78.336z"/></svg>', '<svg class="icon icon-next" viewBox="0 0 1024 1024" xmlns="http://www.w3.org/2000/svg" width="12" height="12"><path d="M822.272 146.944l-396.8 396.8c-19.456 19.456-51.2 19.456-70.656 0-18.944-19.456-18.944-51.2 0-70.656l396.8-396.8c19.456-19.456 51.2-19.456 70.656 0 18.944 19.456 18.944 45.056 0 70.656z"/><path d="M745.472 940.544l-396.8-396.8c-19.456-19.456-19.456-51.2 0-70.656 19.456-19.456 51.2-19.456 70.656 0l403.456 390.144c19.456 25.6 19.456 51.2 0 76.8-26.112 19.968-51.712 19.968-77.312.512zm-564.224-63.488c0-3.584 0-7.68.512-11.264h-.512v-714.24h.512c-.512-3.584-.512-7.168-.512-11.264 0-43.008 21.504-78.336 48.128-78.336s48.128 34.816 48.128 78.336c0 3.584 0 7.68-.512 11.264h.512v714.24h-.512c.512 3.584.512 7.168.512 11.264 0 43.008-21.504 78.336-48.128 78.336s-48.128-35.328-48.128-78.336z"/></svg>', 1, '...', array( 'wrapTag' => 'ul', 'wrapClass' => 'joe_pagination', 'itemTag' => 'li', 'textTag' => 'a', 'currentClass' => 'active', 'prevClass' => 'prev', 'nextClass' => 'next' ) ); ?> <?php else : ?> <div class="joe_load">查看更多</div> <?php endif ?>修改主题目录下的index.php,添加如下代码,注意:此代码需添加在joe.index.min.js文件引入之前。<script> document.addEventListener('DOMContentLoaded', () => { window.Joe.PAGE_INDEX = '<?php echo $this->_currentPage; ?>' || 1; }); </script>在index.php中找到<div class="joe_load">查看更多</div>替换为<?php $this->need('public/pagination.php'); ?> 在主题目录下的functions.php文件中增加下面的代码,用于后台设置,这里默认的使用按钮切换形式,如果需求默认为点击加载形式可以将下面第四行的default改为ajax。$JPageStatus = new Typecho_Widget_Helper_Form_Element_Select( 'JPageStatus', array('default' => '按钮切换形式(默认)', 'ajax' => '点击加载形式'), 'default', '选择首页的分页形式', '介绍:选择一款您所喜欢的分页形式' ); $JPageStatus->setAttribute('class', 'joe_content joe_other'); $form->addInput($JPageStatus->multiMode());最后就是修改JS文件,找到主题目录下/assets/js/joe.index.min.js,将page:1替换为page:window.Joe.PAGE_INDEX还需要先恢复默认主题,或者其他主题然后再切换到jeo主题,主要是需要清除主题的缓存,不然不会看到效果