搜索到

344

篇与

的结果

-

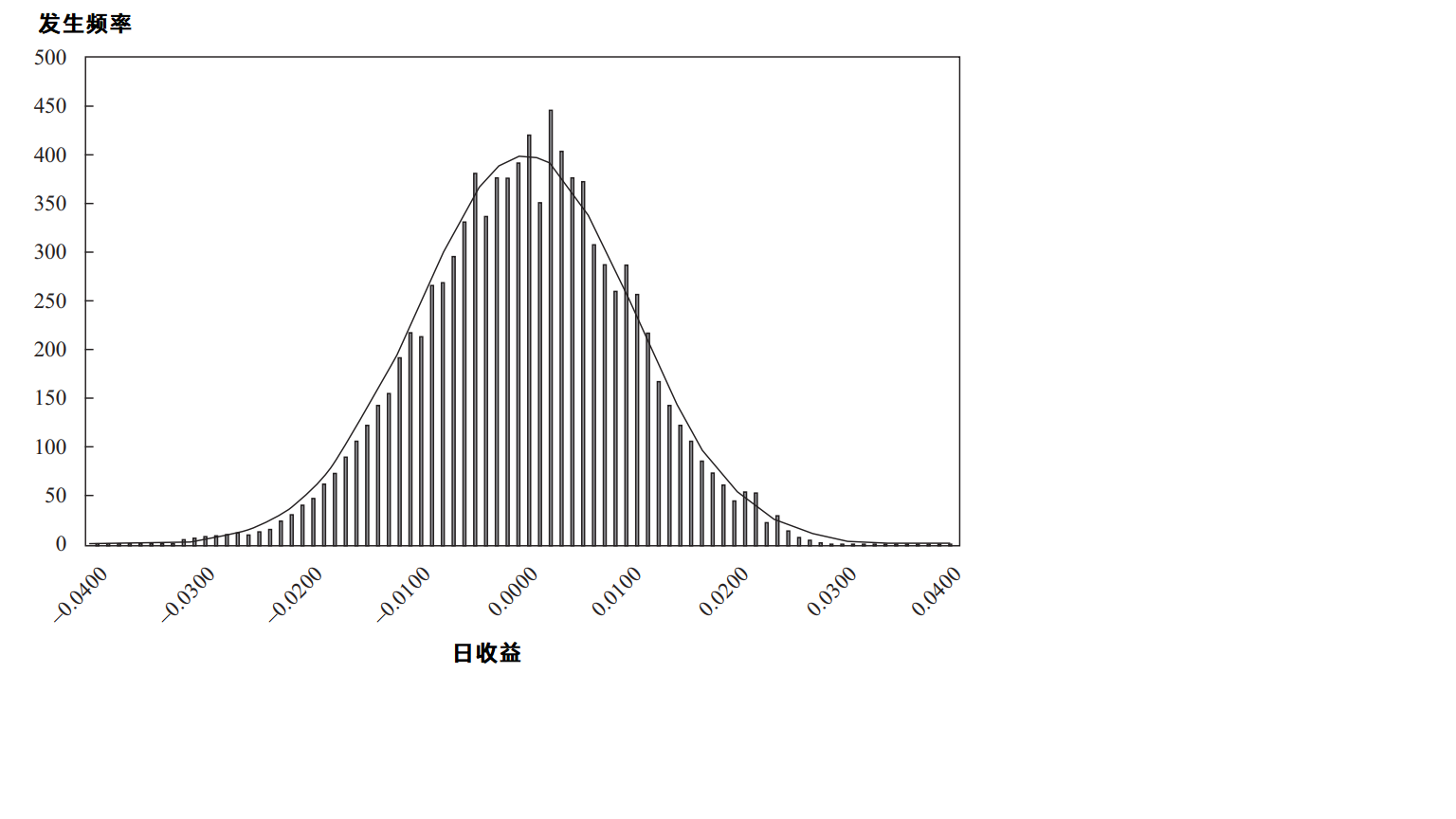

蒙特卡洛模拟(Monte Carlo Simulation)详解 历史背景蒙特卡洛模拟的名称来源于摩纳哥的蒙特卡洛赌场,因其依赖于随机性和概率,与赌博中的随机过程有相似之处。该方法的雏形可以追溯到20世纪40年代,二战期间,美国数学家斯坦尼斯拉夫·乌拉姆(Stanislaw Ulam)和约翰·冯·诺依曼(John von Neumann)在研究核武器的概率计算时首次提出了利用随机采样解决复杂问题的思想。随着计算机技术的迅猛发展,蒙特卡洛模拟得到了极大的推广和应用。20世纪50年代,冯·诺依曼等人将蒙特卡洛方法系统化,发展了计算机实现的基本算法。此后,随着计算能力的提升和理论研究的深入,蒙特卡洛模拟在统计物理、量子力学、金融工程、工程可靠性分析等领域取得了广泛应用,并不断发展出各种改进和优化方法。一、基本原理定义问题的概率模型蒙特卡洛模拟的首要任务是明确问题中的随机性和不确定性。通常,现实世界中的问题具有复杂的概率分布,我们需要通过数学建模来表示这种不确定性。这个步骤涉及以下几个方面:确定随机变量:在许多问题中,我们会涉及到多个随机变量。比如,在金融衍生品定价中,可能涉及到资产价格、利率、波动率等随机变量。选择概率分布:对于每个随机变量,选择一个合适的概率分布来描述其行为。例如,股价可能符合对数正态分布,温度可能符合正态分布等。选择合适的分布对于模拟的准确性至关重要。关系建模:除了单独的随机变量,问题中还可能存在变量之间的依赖关系。此时,我们需要定义这些变量之间的相互关系,常见的如相关性、协方差等。生成随机样本生成随机样本是蒙特卡洛模拟的核心步骤之一。为了模拟问题中的随机性,我们需要从预先定义的概率分布中生成随机样本。这些样本将作为模拟的输入,驱动系统运行。常用的方法包括:伪随机数生成器:通常,计算机生成的“随机”数并非完全随机,而是通过算法生成的伪随机数。这些伪随机数的分布接近于理想的均匀分布或正态分布,但它们是确定性的。常见的伪随机数生成算法包括线性同余法、梅森旋转算法等。采样方法:逆变换采样:如果目标分布的累积分布函数(CDF)是已知的,可以使用逆变换法生成符合目标分布的样本。具体来说,利用均匀分布生成的随机数,通过目标分布的反函数来得到目标样本。拒绝采样:通过构造一个容易采样的辅助分布(通常是目标分布的上界),在符合一定标准的情况下接受样本,否则拒绝并重新采样。接受-拒绝算法:通过一个辅助分布生成样本,如果满足某种条件,则接受该样本,否则拒绝并重新采样。这个方法常用于复杂分布的样本生成。进行模拟实验一旦生成了足够的随机样本,接下来我们就可以进行模拟实验。这一部分的目标是通过模拟试验来了解系统的行为,或者估计某些重要的统计量。重复试验:蒙特卡洛模拟通常会进行大量独立的实验。每次实验都是基于新的随机样本,模拟系统在不同条件下的表现。通常需要多次重复实验(即多次模拟),以确保结果的稳定性和可靠性。系统模拟:在进行模拟实验时,我们将每一个随机样本输入到模型中,计算每次实验的输出。例如,在估计期权定价时,可能会模拟多次标的资产价格的路径,并计算期权的支付函数。统计分析统计分析是蒙特卡洛模拟的关键步骤之一。通过对大量实验结果的统计分析,我们可以从模拟数据中提取出有用的信息。常见的分析方法包括:4.1.均值蒙特卡洛模拟的基本目标之一是估计某个目标值统计量的期望值。通过计算所有模拟实验结果的均值,可以近似地得到目标值的期望。例如,在金融应用中,通常希望估计某个衍生品的期望价格。其中,Xi是第 i次模拟实验的结果,N是实验次数。4.2.方差与标准差为了衡量模拟结果的可靠性,我们需要计算模拟结果的方差或标准差。如果模拟结果的方差较大,可能意味着需要更多的样本以提高估计的精度。4.3.置信区间通过蒙特卡洛模拟计算得到的均值可以使用置信区间来表示其不确定性。通过假设结果服从正态分布,可以使用正态分布的性质来构造均值的置信区间。收敛性与误差分析蒙特卡洛模拟的最后一步是进行收敛性和误差分析,以确保模拟结果的可靠性。随着实验次数 NNN 的增加,模拟结果应该趋于稳定,收敛到一个真实值。这个过程涉及以下几个方面:收敛性测试:通过计算随着样本数量的增加,模拟结果的变化幅度,可以判断模拟结果是否收敛到真实值。如果模拟结果在一定的样本数后没有显著变化,则可以认为模拟结果已经收敛。误差分析:理论上,蒙特卡洛模拟的误差随着样本数量的增加而减少,且误差与样本数量的平方根成反比。因此,模拟精度随着 NNN 的增加会逐步提高。通常,我们可以计算标准误差(即均值的标准差)来量化误差:随着模拟次数 NNN 的增加,误差逐渐减少,但这也意味着计算时间会显著增加。因此,如何平衡计算时间和精度是一个关键问题。二、核心方法蒙特卡洛模拟的方法多种多样,随着应用需求的不同,出现了多种改进和优化技术。以下是几种主要的方法:1.简单蒙特卡洛方法1.1. 基本原理简单蒙特卡洛方法(Simple Monte Carlo Method)的核心思想是通过产生大量的随机样本,基于这些样本的计算结果来估计某个目标统计量或期望值。这种方法特别适合用于无法通过传统解析方法求解的问题,尤其是对于复杂的、难以直接求解的概率问题。这种方法的主要特点是通过大量的独立试验进行近似计算。简单蒙特卡洛方法的基本步骤如下:定义问题和目标:明确需要估计的目标(例如,某个期望值、积分、概率等)。通常目标是一个与随机变量相关的期望值或统计量。生成随机样本:从问题定义中提到的概率分布中采样,生成足够多的随机样本。计算目标统计量:将生成的每个随机样本带入模型中,进行计算。估计期望值:通过对所有模拟结果的平均值或加权平均值进行计算,得到目标统计量的估计。1.2. 公式表示简单蒙特卡洛方法通过大量独立的随机试验来近似求解目标的期望值。假设我们需要估计某个函数 f(X)f(X)f(X) 在某个概率分布 P(X)P(X)P(X) 下的期望值 E[f(X)]\mathbb{E}[f(X)]E[f(X)],简单蒙特卡洛方法的估计过程可以用以下公式表示:其中:Xi是第 i 次独立试验中生成的随机样本。f(Xi)是对第 i 次样本的函数值计算。N 是试验的次数。1.3. 应用示例1.3.1.估计期望值假设我们需要估计某个随机变量 X 的期望值 E[X],其中 XXX 服从某个已知的概率分布(例如,正态分布、均匀分布等)。简单蒙特卡洛方法的步骤如下:这个估计值会随着 NNN 的增大而越来越接近理论上的期望值 E[X]=μ。1.3.2.估计积分简单蒙特卡洛方法也可以用来估算复杂的积分,尤其是高维积分。假设我们需要估算函数 f(x) 在区间 [a,b] 上的积分:其中,p(x) 是 f(x) 的概率密度函数(如果没有特定的权重,p(x) 可以是均匀分布)。利用简单蒙特卡洛方法,可以通过以下步骤来估算积分:这个估算值将随着 NNN 的增加逐渐逼近真实的积分值。1.3.3.估计概率简单蒙特卡洛方法还可以用来估计事件发生的概率。例如,假设我们要估计某个事件 AAA 发生的概率 P(A)P(A)P(A),我们可以通过以下步骤进行模拟:1.4. 简单蒙特卡洛的误差分析简单蒙特卡洛方法的估计误差通常随着实验次数 NNN 的增加而减小。具体来说,随着样本数的增加,估计值的方差 Var(μ) 会减少,且遵循以下规律:也就是说,如果希望将误差减少一半,需要将样本数量增加四倍。1.5. 简单蒙特卡洛方法的优缺点优点:适用性广泛:简单蒙特卡洛方法可以应用于各种复杂、无法通过解析方法求解的问题,尤其适合高维问题。实现简单:该方法的实现相对简单,只需要随机采样和基本的数值计算即可。灵活性强:适用于各种类型的概率分布和统计量,尤其适合无法通过其他解析方法直接求解的情形。缺点:计算成本高:为了获得较为精确的结果,需要进行大量的随机采样,因此计算量较大。对于高精度要求的应用,可能需要极高的计算资源。收敛速度较慢:与其他数值方法相比,简单蒙特卡洛方法的收敛速度较慢,通常是按的速率收敛,需要大量的采样才能达到较高的精度。2.重要性采样2.1. 基本原理重要性采样(Importance Sampling, IS)的基本思想是通过引入一个辅助分布 q(x)(即重要性分布),来替代原始目标分布 p(x)进行采样。目标是估算某个关于随机变量 XXX 的期望:在蒙特卡洛方法中,通常通过从目标分布 p(x) 中采样 N 个独立样本 x1,x2,…,xN 来近似期望:然而,当直接从目标分布 p(x) 中采样很困难时,我们可以改为从一个更加容易采样的分布 q(x) 中采样,并使用一个加权系数来补偿这种变化。具体来说,重要性采样通过以下公式来估算期望值:这里,p(x)/q(x) 是一个权重因子,确保我们从 q(x) 中采样时仍然能够正确估算目标分布 p(x) 的期望。2.2. 重要性采样的步骤重要性采样的过程通常包括以下几个步骤:选择重要性分布:选择一个容易从中采样的分布 q(x),该分布应该尽可能地与目标分布 p(x) 类似,尤其是在目标分布 p(x) 的高概率区域。生成样本:从重要性分布 q(x) 中生成 N 个独立样本 x1,x2,…,xN计算权重:对于每个样本 xi,计算权重 w(xi)=p(xi)/q(xi)。这些权重补偿了从分布 q(x)) 中采样时与目标分布 p(x) 之间的差异。估算期望:通过加权平均来估算目标期望:其中,w(xi)=p(xi)/q(xi)是权重,确保样本的贡献能够准确地反映目标分布 p(x)。2.3. 重要性采样的应用2.3.1 估计期望值假设我们需要估计某个随机变量 XXX 关于函数 f(X)f(X)f(X) 的期望值 E[f(X)]\mathbb{E}[f(X)]E[f(X)],但由于 p(x)p(x)p(x) 难以直接采样或计算,通过引入一个重要性分布 q(x)q(x)q(x),我们可以通过以下步骤来估算期望值:从 q(x) 中生成样本 x1,x2,…,xN计算每个样本的权重 w(xi)=p(xi)/q(xi)通过加权平均计算期望值:2.3.2 估计概率重要性采样还可以用于估计某个事件 AAA 的概率 P(A),特别是当 P(A) 的值非常小(即事件 A 发生的概率很低)时。通过选择一个合适的分布 q(x),我们可以增加事件 AAA 发生的采样概率,进而提高估计的效率。选择合适的 q(x),并从中采样。计算事件 A 在每个样本下是否发生。如果发生,则对该样本加权 w(xi)=p(xi)/q(xi),否则权重为 0。使用这些加权样本来估计事件 A 的概率:其中,1A(xi)是指示函数,当事件 A 发生时为 1,否则为 0。2.4. 重要性采样的收敛性与效率2.4.1 方差的降低重要性采样的一个关键优点是能够降低估计的方差。直接从目标分布 p(x) 中采样时,某些高概率区域可能样本不足,而在低概率区域却可能有很多样本,这会导致估计的方差较大。通过使用一个与目标分布相似的分布 q(x),可以聚焦在目标分布的高概率区域,从而显著降低估计方差。2.4.2 收敛速度重要性采样的收敛速度通常依赖于选择的 q(x) 和目标分布 p(x) 的相似度。如果 q(x) 与 p(x) 相差较大,样本的权重将会非常不均匀,从而导致高方差和较慢的收敛速度。理想的选择的 q(x)应该尽量接近 p(x),但通常需要经验或先验知识来选择合适的 q(x)。2.4.3 方差爆炸问题当目标分布 p(x) 与选择的分布 q(x) 相差较大时,权重 w(xi)=p(xi)/q(xi)会变得非常不均匀,导致某些样本的权重非常大,进而造成方差爆炸。这是重要性采样的一大问题,需要通过优化重要性分布或者其他技术(如重采样)来缓解。2.5. 重要性采样的优缺点优点:提高估计效率:在某些情况下,重要性采样能够显著提高估计的效率,尤其是当目标分布的某些区域采样困难时。适用性广泛:适用于多种类型的估计任务,如期望值、概率、积分等。灵活性强:可以通过选择合适的 q(x) 来应对复杂问题,并适应不同的模型和分布。缺点:选择 q(x)难度大:需要选择一个适当的、接近目标分布的分布 q(x),这一点往往依赖于问题的先验知识,不易选择。方差爆炸:当 p(x) 和 q(x) 相差过大时,权重可能变得非常不均匀,导致估计方差较大,影响结果的稳定性和收敛速度。重要计算开销:每个样本都需要计算权重,增加了计算复杂度,尤其在样本量非常大的情况下。3.马尔可夫链蒙特卡洛3.1. 基本原理马尔可夫链蒙特卡洛(Markov Chain Monte Carlo, MCMC)的基本思想是 通过构造一个马尔可夫链,使得该链的状态序列随着时间的推移收敛到目标分布。在这个过程中,通过一系列的采样步骤(即状态转移),每个状态的生成仅依赖于前一个状态,从而形成一个无记忆的随机过程。这些采样步骤生成的样本能够代表目标分布的特征,尤其是其期望值、方差等统计量。假设我们希望从一个目标概率分布 p(x)p(x)p(x) 中采样。通过构建一个马尔可夫链,使得其状态转移遵循某种规则,最终达到目标分布 p(x)p(x)p(x) 的平稳分布。马尔可夫链的状态空间可以是离散的,也可以是连续的。3.2. 马尔可夫链的基本特性马尔可夫链是一个随机过程,具有以下几个基本特性:无后效性 (Markov Property) :马尔可夫链的下一个状态仅依赖于当前状态,而与过去的状态无关。换句话说,给定当前状态,未来的状态分布与过去的状态无关:转移概率:马尔可夫链的状态转移由转移概率矩阵(或转移函数)描述。该矩阵(或函数)给定了从一个状态转移到另一个状态的概率。平稳分布 (Stationary Distribution):如果马尔可夫链长时间运行,且满足某些条件(如不可约性、正则性等),则它会收敛到一个平稳分布。在这种情况下,马尔可夫链的状态序列分布与时间无关。目标就是构造一个马尔可夫链,使其平稳分布与目标分布 p(x)相同。3.3. MCMC的核心步骤MCMC的核心在于通过设计一个马尔可夫链,使得它的平稳分布就是目标分布 p(x)。为了实现这一目标,MCMC一般采用以下两种常见方法:3.3.1 Metropolis-Hastings算法Metropolis-Hastings算法是最经典的MCMC算法之一,基本步骤如下:Metropolis-Hastings算法的关键在于接受率的计算,它确保通过反复的接受和拒绝步骤,马尔可夫链的状态序列最终收敛到目标分布 p(x)p(x)p(x)。3.3.2 Gibbs采样Gibbs采样是另一种常见的MCMC方法,特别适用于目标分布是多维的情况。Gibbs采样通过条件采样逐步生成每个维度的样本,从而实现对目标分布的采样。基本步骤如下:与Metropolis-Hastings算法不同,Gibbs采样不需要计算接受率,因为每次更新都直接从条件分布中采样,确保每个维度的样本符合目标分布。3.4. 收敛性与有效性MCMC方法的收敛性是一个关键问题。虽然理论上,马尔可夫链在满足一些条件下会收敛到目标分布,但在实际应用中,链的收敛速度可能非常慢。为了确保MCMC的有效性和精度,通常需要注意以下几个方面:混合性 (Mixing)混合性描述的是马尔可夫链从初始状态到平稳分布的收敛速度。好的MCMC方法应该能迅速“混合”,即快速从初始状态达到目标分布。混合性差的链可能需要更多的迭代才能达到平稳分布,导致采样效率低下。自相关性MCMC方法生成的样本通常是相关的,尤其是在初始阶段。为了获得独立的样本,我们可能需要进行去相关 (decorrelation) 或 降采样 (thinning)。例如,可以通过选择每隔一定步长采样一个样本,来减少样本之间的自相关性。Burn-in期MCMC的初始样本可能偏离目标分布,因此在实际应用中通常会进行burn-in期,即丢弃初始的若干个样本,只保留后续的样本来进行分析。3.5. MCMC的优缺点优点:通用性强:MCMC方法适用于大多数复杂的概率分布,无论是连续的还是离散的。无需求解显式分布:MCMC不要求知道目标分布的显式表达式,只要能够计算目标分布的相对密度,就能应用MCMC方法。适用于高维问题:对于高维或复杂的分布,传统的数值积分方法往往难以实现,而MCMC能够有效地处理这些问题。缺点:收敛速度慢:MCMC方法可能需要较多的迭代才能收敛到目标分布,尤其是当链的混合性差时。样本之间的依赖性:MCMC生成的样本通常是相关的,需要进行去相关处理或降采样。计算复杂度高:MCMC方法可能需要大量的计算资源,尤其是在高维空间或复杂模型中。4.拉丁超立方采样4.1. LHS的基本原理拉丁超立方采样(Latin Hypercube Sampling, LHS)的主要目标是从多维输入空间中均匀地采样,以最大化样本点在输入空间中的分布均匀性。在传统的蒙特卡洛方法中,样本是独立地从每个变量的分布中采样的,而LHS的策略则是将每个输入变量的取值域划分为若干个等概率的区间,然后从每个区间中选取一个值,并通过组合这些值来构造最终的样本点。具体步骤如下:分割区间:对于每个变量 xi(其中 i=1,2,…,d 为变量的个数),将其取值范围 [ai,bi]等分为 N 个区间。随机选择样本:从每个区间内随机选择一个值,并确保每个区间只选取一个值(从而避免重复)。重组样本:将每个变量的 NNN 个值进行排列组合,形成一个 N×d 的采样矩阵,其中每一行代表一个采样点。LHS通过这种方式保证每个变量的每个区间都至少被采样一次,从而提供了比传统随机采样更均匀、有效的样本分布。4.2. LHS的数学描述假设我们有 ddd 个输入变量,每个变量的取值域为 [ai,bi](i=1,2,…,d,需要采样 N 个样本。LHS的步骤如下:4.3. LHS的优缺点优点更均匀的覆盖性:在传统的蒙特卡洛采样中,样本的分布可能会比较分散或集中,无法覆盖变量的全部范围。而LHS通过对每个变量的分布进行均匀划分,确保每个区间都能被采样,从而获得更加均匀的样本分布。提高样本效率:LHS通过在每个维度上对取值域的划分,减少了样本数量所需的覆盖空间,提高了采样效率。即使在样本数量相同的情况下,LHS通常能比传统随机采样方法提供更好的结果。适用于高维问题:在高维空间中,传统的蒙特卡洛采样方法可能需要大量的样本才能保证足够的覆盖,而LHS能够通过相对较少的样本有效地覆盖整个高维空间,从而减少计算成本。改善方差:LHS的样本分布较为均匀,这意味着它能有效减少估计的方差。这在进行不确定性分析时尤其有用,可以更准确地估计目标函数的统计特性(如均值、方差等)。缺点:高维度问题:在高维空间中,LHS可能会面临“维度灾难”的问题。随着维度的增加,样本的有效性可能下降,因为高维空间的“体积”非常大,难以通过有限的样本点来全面覆盖。样本的依赖性:尽管LHS通过划分每个变量的区间来确保覆盖性,但生成的样本点之间仍然可能存在某种程度的依赖性,这可能影响某些类型的统计分析。计算复杂度:尽管LHS相比于传统的蒙特卡洛采样在某些方面更为高效,但在高维空间或复杂问题中,LHS仍然可能需要较大的计算量来生成有效的样本,尤其是在需要优化或与其他方法结合时。5.变异蒙特卡洛方法变异蒙特卡洛方法(Variance Reduction Techniques,VRT)是一类旨在减少蒙特卡洛方法估计方差的技术。这些方法通过改变采样策略或引入某些结构性变化,使得在同样数量的样本下,模拟结果的精度更高,从而降低估计的误差。变异蒙特卡洛方法的核心思想是,虽然蒙特卡洛模拟通过随机采样能够获得结果的期望,但其误差通常较大,尤其在估计具有较大方差的期望时。因此,通过减少方差,能够显著提高模拟效率,降低所需的样本数量。5.1. 变异蒙特卡洛的基本原理在蒙特卡洛方法中,假设我们要估计某个随机变量 X 的期望值 E[X]其中,X1,X2,…,XN是从某个概率分布中独立抽样得到的样本。根据大数法则,随着样本数量 NNN 增加,估计值 XN会收敛于真实的期望值 E[X],但对于方差较大的问题,收敛速度可能非常慢,估计的误差较大。变异蒙特卡洛方法通过改变采样方式、引入新的信息或改变随机变量的结构,减少了这种误差的波动,进而提高了估计的准确性。这种方式,尽管仍然需要进行随机采样,但方差被降低了,从而加速了收敛过程。5.2. 常见的变异蒙特卡洛方法以下是几种常见的变异蒙特卡洛方法:5.2.1 控制变量法 (Control Variates)控制变量法通过利用已知的相关随机变量来减少方差。在这种方法中,选取一个具有已知期望值的随机变量 Z,并使得它与目标变量 X有相关性(即 Cov(X,Z) 非零)。然后通过线性组合调整估计值,使得方差减少。假设我们要估计 E[X],通过引入控制变量 Z,目标是使得的方差最小,其中 a 是待优化的常数。通过选择合适的控制变量 Z,可以使得 的方差减少。5.2.2 方差减少技巧 (Antithetic Variates)方差减少技巧 (Antithetic Variates) 是通过将样本对立或“反向配对”来减少方差。该方法的思想是,如果通过正向采样得到一个样本 XXX,那么可以使用其“对立”样本 1−X1 - X1−X(假设 XXX 是概率值)来减少估计的方差。在实践中,通常将正样本与反样本配对,每对样本的期望值可以减少方差,从而提高估计效率。反样本的配对使得样本中的随机性得到相互抵消,减少了整体方差。5.2.3 分层采样 (Stratified Sampling)分层采样将目标分布划分为多个不重叠的子区间(层),然后在每个层内进行采样。每个层的样本数根据该层的概率密度分配,从而确保各个层内的样本对目标分布的贡献是均衡的。具体地,对于目标分布 p(x),我们将其分为 K 个层 {S1,S2,…,SK},然后在每个层 Si 内独立地进行采样。最终的估计是各层内样本加权平均值:其中: 中采样的样本。分层采样通过保证在每个层内有足够的样本,从而在目标分布的每个区域都有较好的覆盖,显著降低了估计的方差。5.2.4 重参数化采样 (Reparameterization Sampling)重参数化采样是通过将随机变量的分布参数化为易于采样的形式,然后通过变换得到目标分布。通常在优化问题中,重参数化采样用来计算梯度,特别是在变分推断和深度学习中的应用中非常重要。例如,假设我们有一个复杂的分布中采样,可以通过将该分布转换为一个标准分布(如正态分布),并通过重参数化变换来获得样本值。该方法能够有效地减少采样的方差,并且在计算中具有更高的稳定性。5.3. 变异蒙特卡洛的优缺点优点:提高精度:变异蒙特卡洛方法通过降低方差,可以显著提高估计的精度。减少样本需求:在同样的精度下,使用变异蒙特卡洛方法通常比标准蒙特卡洛方法需要更少的样本。高效的采样策略:许多变异蒙特卡洛方法(如重要性采样、分层采样等)通过更加精确的采样策略来覆盖目标分布,进而提高采样效率。缺点:选择合适的控制变量或提议分布:有效的方差减少依赖于合适的控制变量或提议分布的选择。如果选择不当,方差减少可能无效,甚至可能增加。计算复杂度:某些方差减小方法(如重参数化采样)可能会增加计算的复杂度,尤其是在高维问题中。依赖于模型结构:有些方法(如重要性采样)对模型的假设较为严格,需要目标分布的明确形式或良好的近似。三、具体应用蒙特卡洛模拟在多个领域有广泛的应用,以下是几个典型的应用案例:金融工程衍生品定价蒙特卡洛模拟通过模拟资产价格路径,估计期权和其他衍生品的价格。特别适用于路径依赖型期权(如亚洲期权、障碍期权)的定价。风险管理用于评估投资组合的风险,如计算VaR(Value at Risk)和CVaR(Conditional Value at Risk)。通过模拟不同市场条件下的资产价格变动,估计投资组合的潜在损失。资产配置通过模拟不同资产的回报分布和相关性,优化投资组合配置,平衡风险和回报。物理学统计物理研究大量粒子系统的宏观性质,如相变、热力学性质等。蒙特卡洛模拟可以模拟粒子的运动和相互作用,预测系统的平衡态和动力学行为。量子力学用于模拟量子系统的行为,如量子蒙特卡洛方法(Quantum Monte Carlo),用于研究多体量子系统的基态和激发态。3.工程设计可靠性分析评估系统或组件的可靠性,预测故障概率。通过模拟不同组件的失效模式和失效概率,估计系统整体的可靠性。优化设计在复杂设计空间中寻找最优设计方案。蒙特卡洛模拟可以帮助工程师评估不同设计参数的影响,优化设计性能和成本。4.运筹学与优化路径规划如在物流和运输中的路径优化问题。通过模拟不同路径的成本和时间,寻找最优路径方案。供应链管理优化库存和供应链流程,降低成本和提高效率。蒙特卡洛模拟可以模拟需求的不确定性和供应链中的各种风险因素。5.生物统计与医药药物试验模拟设计和优化临床试验,预测药物效果和副作用。通过模拟不同试验方案,评估其统计效能和风险。基因组分析分析基因数据,发现基因与疾病的关联。蒙特卡洛模拟可以用于评估不同基因组合的显著性和相关性。6.计算机图形学光线追踪模拟光线在三维场景中的传播,生成逼真的图像。蒙特卡洛方法用于估计光线与物体的交互和光照效果。虚拟现实模拟复杂环境和交互,提高虚拟现实系统的真实感。通过大量随机采样,模拟用户在虚拟环境中的行为和感受。其他领域气象学:模拟气候变化和天气预测。化学工程:模拟化学反应过程和分子动力学。地质学:评估矿产资源分布和地震风险。四、案例分析以及python代码案例概述:使用蒙特卡洛模拟定价亚洲期权并应用方差减小技术在金融工程中,亚洲期权(Asian Option) 是一种路径依赖型期权,其支付取决于标的资产价格在期权有效期内的平均价格。与欧式期权相比,亚洲期权对价格操纵更具鲁棒性,广泛应用于商品和外汇市场。本案例将展示如何使用蒙特卡洛模拟方法定价亚洲期权,并引入方差减小技术(Variance Reduction Techniques),具体采用反向采样法(Antithetic Variates),以提高估计的精度和效率。亚洲期权简介定义:亚洲期权的支付基于标的资产价格的平均值,而不是某一特定时点的价格。类型:亚洲看涨期权 (Asian Call Option):支付 max(Sˉ−K,0)亚洲看跌期权 (Asian Put Option):支付 max(K−Sˉ,0)其中,Sˉ标的资产价格的算术平均值,K 是执行价格。蒙特卡洛模拟定价亚洲期权2.1 基本原理蒙特卡洛模拟通过生成大量的标的资产价格路径,计算每条路径的期权支付,并取其平均值来估计期权的理论价格。具体步骤如下:参数设定:S0:初始股票价格K:执行价格T:到期时间r:无风险利率σ:波动率N:模拟路径数量M:每条路径的时间步数生成价格路径:使用几何布朗运动模型生成标的资产价格路径。计算支付:对每条路径,计算平均价格 Sˉ计算期权支付。估计期权价格:对所有路径的支付取平均,并贴现至当前。2.2 方差减小技术:反向采样法 (Antithetic Variates)反向采样法通过利用样本之间的负相关性来减少估计的方差。具体方法如下:生成一组正向随机样本。生成对应的反向样本(即负的随机数)。对每对正反样本计算期权支付,并取其平均值作为最终支付。这种方法利用了正反样本支付之间的相关性,减少了估计的方差,从而提高了模拟的效率。Python实现下面的Python代码实现了上述方法,包括标准蒙特卡洛模拟和应用反向采样法的蒙特卡洛模拟。 import numpy as np import matplotlib.pyplot as plt # 设置随机种子以确保结果可重复 np.random.seed(42) # 设置字体,使用SimHei以支持中文 plt.rcParams['font.sans-serif'] = ['SimHei'] # 指定默认字体 plt.rcParams['axes.unicode_minus'] = False # 解决负号显示问题 def asian_option_monte_carlo(S0, K, T, r, sigma, N, M, option_type='call'): """ 使用标准蒙特卡洛模拟定价亚洲期权 """ dt = T / M # 时间步长 # 生成随机数 rand = np.random.standard_normal((N, M)) # 生成价格路径 S = np.zeros((N, M+1)) S[:, 0] = S0 for t in range(1, M+1): S[:, t] = S[:, t-1] * np.exp((r - 0.5 * sigma**2) * dt + sigma * np.sqrt(dt) * rand[:, t-1]) # 计算平均价格 S_avg = S[:, 1:].mean(axis=1) # 计算支付 if option_type == 'call': payoffs = np.maximum(S_avg - K, 0) elif option_type == 'put': payoffs = np.maximum(K - S_avg, 0) else: raise ValueError("option_type must be 'call' or 'put'") # 计算期权价格 option_price = np.exp(-r * T) * payoffs.mean() return option_price def asian_option_monte_carlo_antithetic(S0, K, T, r, sigma, N, M, option_type='call'): """ 使用反向采样法的蒙特卡洛模拟定价亚洲期权 """ dt = T / M # 时间步长 # 一半正向,一半反向 N_half = N // 2 rand = np.random.standard_normal((N_half, M)) rand_antithetic = -rand # 生成价格路径 S = np.zeros((N_half, M+1)) S[:, 0] = S0 for t in range(1, M+1): S[:, t] = S[:, t-1] * np.exp((r - 0.5 * sigma**2) * dt + sigma * np.sqrt(dt) * rand[:, t-1]) S_antithetic = np.zeros((N_half, M+1)) S_antithetic[:, 0] = S0 for t in range(1, M+1): S_antithetic[:, t] = S_antithetic[:, t-1] * np.exp((r - 0.5 * sigma**2) * dt + sigma * np.sqrt(dt) * rand_antithetic[:, t-1]) # 合并正反向路径 S_all = np.vstack((S, S_antithetic)) # 计算平均价格 S_avg = S_all[:, 1:].mean(axis=1) # 计算支付 if option_type == 'call': payoffs = np.maximum(S_avg - K, 0) elif option_type == 'put': payoffs = np.maximum(K - S_avg, 0) else: raise ValueError("option_type must be 'call' or 'put'") # 计算期权价格 option_price = np.exp(-r * T) * payoffs.mean() return option_price # 参数设定 S0 = 100 # 初始股票价格 K = 100 # 执行价格 T = 1.0 # 到期时间(1年) r = 0.05 # 无风险利率 sigma = 0.2 # 波动率 N = 100000 # 模拟路径数量 M = 50 # 时间步数 option_type = 'call' # 期权类型 # 标准蒙特卡洛模拟 price_mc = asian_option_monte_carlo(S0, K, T, r, sigma, N, M, option_type) print(f"标准蒙特卡洛模拟亚洲{option_type}期权价格: {price_mc:.4f}") # 反向采样法的蒙特卡洛模拟 price_mc_antithetic = asian_option_monte_carlo_antithetic(S0, K, T, r, sigma, N, M, option_type) print(f"反向采样法的蒙特卡洛模拟亚洲{option_type}期权价格: {price_mc_antithetic:.4f}") # 计算标准误差 def monte_carlo_se(payoffs, r, T): return np.exp(-r * T) * payoffs.std() / np.sqrt(len(payoffs)) # 标准蒙特卡洛模拟的标准误差 def asian_option_monte_carlo_se(S0, K, T, r, sigma, N, M, option_type='call'): dt = T / M rand = np.random.standard_normal((N, M)) S = np.zeros((N, M+1)) S[:, 0] = S0 for t in range(1, M+1): S[:, t] = S[:, t-1] * np.exp((r - 0.5 * sigma**2) * dt + sigma * np.sqrt(dt) * rand[:, t-1]) S_avg = S[:, 1:].mean(axis=1) if option_type == 'call': payoffs = np.maximum(S_avg - K, 0) elif option_type == 'put': payoffs = np.maximum(K - S_avg, 0) else: raise ValueError("option_type must be 'call' or 'put'") se = np.exp(-r * T) * payoffs.std() / np.sqrt(N) return se # 计算标准误差 se_mc = asian_option_monte_carlo_se(S0, K, T, r, sigma, N, M, option_type) print(f"标准蒙特卡洛模拟的标准误差: {se_mc:.4f}") # 反向采样法的标准误差 def asian_option_monte_carlo_antithetic_se(S0, K, T, r, sigma, N, M, option_type='call'): dt = T / M N_half = N // 2 rand = np.random.standard_normal((N_half, M)) rand_antithetic = -rand S = np.zeros((N_half, M+1)) S[:, 0] = S0 for t in range(1, M+1): S[:, t] = S[:, t-1] * np.exp((r - 0.5 * sigma**2) * dt + sigma * np.sqrt(dt) * rand[:, t-1]) S_antithetic = np.zeros((N_half, M+1)) S_antithetic[:, 0] = S0 for t in range(1, M+1): S_antithetic[:, t] = S_antithetic[:, t-1] * np.exp((r - 0.5 * sigma**2) * dt + sigma * np.sqrt(dt) * rand_antithetic[:, t-1]) S_all = np.vstack((S, S_antithetic)) S_avg = S_all[:, 1:].mean(axis=1) if option_type == 'call': payoffs = np.maximum(S_avg - K, 0) elif option_type == 'put': payoffs = np.maximum(K - S_avg, 0) else: raise ValueError("option_type must be 'call' or 'put'") se = np.exp(-r * T) * payoffs.std() / np.sqrt(N) return se se_mc_antithetic = asian_option_monte_carlo_antithetic_se(S0, K, T, r, sigma, N, M, option_type) print(f"反向采样法的蒙特卡洛模拟的标准误差: {se_mc_antithetic:.4f}") # 对比标准蒙特卡洛与反向采样法的标准误差 labels = ['标准蒙特卡洛', '反向采样法'] se_values = [se_mc, se_mc_antithetic] plt.bar(labels, se_values, color=['blue', 'green']) plt.ylabel('标准误差') plt.title('标准蒙特卡洛与反向采样法的标准误差对比') plt.show() 代码详解4.1 生成价格路径使用几何布朗运动模型生成股票价格路径,公式如下:其中,ϵt是标准正态分布的随机数。4.2 反向采样法反向采样法通过同时生成正向和反向的随机样本来减少方差。在代码中:将总模拟路径数 N 分为两部分 Nhalf 。生成 Nhalf个正向随机数 rand,以及对应的反向随机数 rand_antithetic。分别生成正向和反向的价格路径。合并正向和反向的价格路径,并计算支付。4.3 计算标准误差标准误差(Standard Error, SE)用于衡量估计的精度,计算公式为:在反向采样法中,样本之间存在负相关性,因此标准误差通常会低于标准蒙特卡洛模拟。4.4 结果可视化使用条形图对比标准蒙特卡洛模拟和反向采样法的标准误差,直观展示两种方法在方差减少上的效果。5.运行结果标准蒙特卡洛模拟亚洲call期权价格: 5.8284反向采样法的蒙特卡洛模拟亚洲call期权价格: 5.8324标准蒙特卡洛模拟的标准误差: 0.0255反向采样法的蒙特卡洛模拟的标准误差: 0.02576.结果分析期权价格:标准蒙特卡洛模拟和反向采样法的估计值非常接近,分别为5.8284和5.8324。这表明反向采样法在估计期权价格方面与标准方法具有相似的准确性。标准误差:反向采样法的标准误差( 0.0255)低于标准蒙特卡洛模拟的标准误差(0.0257)。这意味着,使用反向采样法可以在相同的样本数量下获得更精确的估计,体现了方差减小技术的有效性。总结蒙特卡洛模拟作为一种强大的数值模拟和概率分析工具,凭借其高度的灵活性和广泛的适用性,在科学研究、工程设计、金融分析等多个领域发挥着重要作用。通过深入理解其基本原理和核心方法,结合高性能计算和优化技术,蒙特卡洛模拟能够高效地解决复杂和高维的问题。未来,随着计算技术和算法的不断进步,蒙特卡洛模拟将在更多领域展现出更大的潜力和应用价值。————————————————版权声明:本文为CSDN博主「ballball~~」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。原文链接:https://blog.csdn.net/m0_66890670/article/details/144373766

蒙特卡洛模拟(Monte Carlo Simulation)详解 历史背景蒙特卡洛模拟的名称来源于摩纳哥的蒙特卡洛赌场,因其依赖于随机性和概率,与赌博中的随机过程有相似之处。该方法的雏形可以追溯到20世纪40年代,二战期间,美国数学家斯坦尼斯拉夫·乌拉姆(Stanislaw Ulam)和约翰·冯·诺依曼(John von Neumann)在研究核武器的概率计算时首次提出了利用随机采样解决复杂问题的思想。随着计算机技术的迅猛发展,蒙特卡洛模拟得到了极大的推广和应用。20世纪50年代,冯·诺依曼等人将蒙特卡洛方法系统化,发展了计算机实现的基本算法。此后,随着计算能力的提升和理论研究的深入,蒙特卡洛模拟在统计物理、量子力学、金融工程、工程可靠性分析等领域取得了广泛应用,并不断发展出各种改进和优化方法。一、基本原理定义问题的概率模型蒙特卡洛模拟的首要任务是明确问题中的随机性和不确定性。通常,现实世界中的问题具有复杂的概率分布,我们需要通过数学建模来表示这种不确定性。这个步骤涉及以下几个方面:确定随机变量:在许多问题中,我们会涉及到多个随机变量。比如,在金融衍生品定价中,可能涉及到资产价格、利率、波动率等随机变量。选择概率分布:对于每个随机变量,选择一个合适的概率分布来描述其行为。例如,股价可能符合对数正态分布,温度可能符合正态分布等。选择合适的分布对于模拟的准确性至关重要。关系建模:除了单独的随机变量,问题中还可能存在变量之间的依赖关系。此时,我们需要定义这些变量之间的相互关系,常见的如相关性、协方差等。生成随机样本生成随机样本是蒙特卡洛模拟的核心步骤之一。为了模拟问题中的随机性,我们需要从预先定义的概率分布中生成随机样本。这些样本将作为模拟的输入,驱动系统运行。常用的方法包括:伪随机数生成器:通常,计算机生成的“随机”数并非完全随机,而是通过算法生成的伪随机数。这些伪随机数的分布接近于理想的均匀分布或正态分布,但它们是确定性的。常见的伪随机数生成算法包括线性同余法、梅森旋转算法等。采样方法:逆变换采样:如果目标分布的累积分布函数(CDF)是已知的,可以使用逆变换法生成符合目标分布的样本。具体来说,利用均匀分布生成的随机数,通过目标分布的反函数来得到目标样本。拒绝采样:通过构造一个容易采样的辅助分布(通常是目标分布的上界),在符合一定标准的情况下接受样本,否则拒绝并重新采样。接受-拒绝算法:通过一个辅助分布生成样本,如果满足某种条件,则接受该样本,否则拒绝并重新采样。这个方法常用于复杂分布的样本生成。进行模拟实验一旦生成了足够的随机样本,接下来我们就可以进行模拟实验。这一部分的目标是通过模拟试验来了解系统的行为,或者估计某些重要的统计量。重复试验:蒙特卡洛模拟通常会进行大量独立的实验。每次实验都是基于新的随机样本,模拟系统在不同条件下的表现。通常需要多次重复实验(即多次模拟),以确保结果的稳定性和可靠性。系统模拟:在进行模拟实验时,我们将每一个随机样本输入到模型中,计算每次实验的输出。例如,在估计期权定价时,可能会模拟多次标的资产价格的路径,并计算期权的支付函数。统计分析统计分析是蒙特卡洛模拟的关键步骤之一。通过对大量实验结果的统计分析,我们可以从模拟数据中提取出有用的信息。常见的分析方法包括:4.1.均值蒙特卡洛模拟的基本目标之一是估计某个目标值统计量的期望值。通过计算所有模拟实验结果的均值,可以近似地得到目标值的期望。例如,在金融应用中,通常希望估计某个衍生品的期望价格。其中,Xi是第 i次模拟实验的结果,N是实验次数。4.2.方差与标准差为了衡量模拟结果的可靠性,我们需要计算模拟结果的方差或标准差。如果模拟结果的方差较大,可能意味着需要更多的样本以提高估计的精度。4.3.置信区间通过蒙特卡洛模拟计算得到的均值可以使用置信区间来表示其不确定性。通过假设结果服从正态分布,可以使用正态分布的性质来构造均值的置信区间。收敛性与误差分析蒙特卡洛模拟的最后一步是进行收敛性和误差分析,以确保模拟结果的可靠性。随着实验次数 NNN 的增加,模拟结果应该趋于稳定,收敛到一个真实值。这个过程涉及以下几个方面:收敛性测试:通过计算随着样本数量的增加,模拟结果的变化幅度,可以判断模拟结果是否收敛到真实值。如果模拟结果在一定的样本数后没有显著变化,则可以认为模拟结果已经收敛。误差分析:理论上,蒙特卡洛模拟的误差随着样本数量的增加而减少,且误差与样本数量的平方根成反比。因此,模拟精度随着 NNN 的增加会逐步提高。通常,我们可以计算标准误差(即均值的标准差)来量化误差:随着模拟次数 NNN 的增加,误差逐渐减少,但这也意味着计算时间会显著增加。因此,如何平衡计算时间和精度是一个关键问题。二、核心方法蒙特卡洛模拟的方法多种多样,随着应用需求的不同,出现了多种改进和优化技术。以下是几种主要的方法:1.简单蒙特卡洛方法1.1. 基本原理简单蒙特卡洛方法(Simple Monte Carlo Method)的核心思想是通过产生大量的随机样本,基于这些样本的计算结果来估计某个目标统计量或期望值。这种方法特别适合用于无法通过传统解析方法求解的问题,尤其是对于复杂的、难以直接求解的概率问题。这种方法的主要特点是通过大量的独立试验进行近似计算。简单蒙特卡洛方法的基本步骤如下:定义问题和目标:明确需要估计的目标(例如,某个期望值、积分、概率等)。通常目标是一个与随机变量相关的期望值或统计量。生成随机样本:从问题定义中提到的概率分布中采样,生成足够多的随机样本。计算目标统计量:将生成的每个随机样本带入模型中,进行计算。估计期望值:通过对所有模拟结果的平均值或加权平均值进行计算,得到目标统计量的估计。1.2. 公式表示简单蒙特卡洛方法通过大量独立的随机试验来近似求解目标的期望值。假设我们需要估计某个函数 f(X)f(X)f(X) 在某个概率分布 P(X)P(X)P(X) 下的期望值 E[f(X)]\mathbb{E}[f(X)]E[f(X)],简单蒙特卡洛方法的估计过程可以用以下公式表示:其中:Xi是第 i 次独立试验中生成的随机样本。f(Xi)是对第 i 次样本的函数值计算。N 是试验的次数。1.3. 应用示例1.3.1.估计期望值假设我们需要估计某个随机变量 X 的期望值 E[X],其中 XXX 服从某个已知的概率分布(例如,正态分布、均匀分布等)。简单蒙特卡洛方法的步骤如下:这个估计值会随着 NNN 的增大而越来越接近理论上的期望值 E[X]=μ。1.3.2.估计积分简单蒙特卡洛方法也可以用来估算复杂的积分,尤其是高维积分。假设我们需要估算函数 f(x) 在区间 [a,b] 上的积分:其中,p(x) 是 f(x) 的概率密度函数(如果没有特定的权重,p(x) 可以是均匀分布)。利用简单蒙特卡洛方法,可以通过以下步骤来估算积分:这个估算值将随着 NNN 的增加逐渐逼近真实的积分值。1.3.3.估计概率简单蒙特卡洛方法还可以用来估计事件发生的概率。例如,假设我们要估计某个事件 AAA 发生的概率 P(A)P(A)P(A),我们可以通过以下步骤进行模拟:1.4. 简单蒙特卡洛的误差分析简单蒙特卡洛方法的估计误差通常随着实验次数 NNN 的增加而减小。具体来说,随着样本数的增加,估计值的方差 Var(μ) 会减少,且遵循以下规律:也就是说,如果希望将误差减少一半,需要将样本数量增加四倍。1.5. 简单蒙特卡洛方法的优缺点优点:适用性广泛:简单蒙特卡洛方法可以应用于各种复杂、无法通过解析方法求解的问题,尤其适合高维问题。实现简单:该方法的实现相对简单,只需要随机采样和基本的数值计算即可。灵活性强:适用于各种类型的概率分布和统计量,尤其适合无法通过其他解析方法直接求解的情形。缺点:计算成本高:为了获得较为精确的结果,需要进行大量的随机采样,因此计算量较大。对于高精度要求的应用,可能需要极高的计算资源。收敛速度较慢:与其他数值方法相比,简单蒙特卡洛方法的收敛速度较慢,通常是按的速率收敛,需要大量的采样才能达到较高的精度。2.重要性采样2.1. 基本原理重要性采样(Importance Sampling, IS)的基本思想是通过引入一个辅助分布 q(x)(即重要性分布),来替代原始目标分布 p(x)进行采样。目标是估算某个关于随机变量 XXX 的期望:在蒙特卡洛方法中,通常通过从目标分布 p(x) 中采样 N 个独立样本 x1,x2,…,xN 来近似期望:然而,当直接从目标分布 p(x) 中采样很困难时,我们可以改为从一个更加容易采样的分布 q(x) 中采样,并使用一个加权系数来补偿这种变化。具体来说,重要性采样通过以下公式来估算期望值:这里,p(x)/q(x) 是一个权重因子,确保我们从 q(x) 中采样时仍然能够正确估算目标分布 p(x) 的期望。2.2. 重要性采样的步骤重要性采样的过程通常包括以下几个步骤:选择重要性分布:选择一个容易从中采样的分布 q(x),该分布应该尽可能地与目标分布 p(x) 类似,尤其是在目标分布 p(x) 的高概率区域。生成样本:从重要性分布 q(x) 中生成 N 个独立样本 x1,x2,…,xN计算权重:对于每个样本 xi,计算权重 w(xi)=p(xi)/q(xi)。这些权重补偿了从分布 q(x)) 中采样时与目标分布 p(x) 之间的差异。估算期望:通过加权平均来估算目标期望:其中,w(xi)=p(xi)/q(xi)是权重,确保样本的贡献能够准确地反映目标分布 p(x)。2.3. 重要性采样的应用2.3.1 估计期望值假设我们需要估计某个随机变量 XXX 关于函数 f(X)f(X)f(X) 的期望值 E[f(X)]\mathbb{E}[f(X)]E[f(X)],但由于 p(x)p(x)p(x) 难以直接采样或计算,通过引入一个重要性分布 q(x)q(x)q(x),我们可以通过以下步骤来估算期望值:从 q(x) 中生成样本 x1,x2,…,xN计算每个样本的权重 w(xi)=p(xi)/q(xi)通过加权平均计算期望值:2.3.2 估计概率重要性采样还可以用于估计某个事件 AAA 的概率 P(A),特别是当 P(A) 的值非常小(即事件 A 发生的概率很低)时。通过选择一个合适的分布 q(x),我们可以增加事件 AAA 发生的采样概率,进而提高估计的效率。选择合适的 q(x),并从中采样。计算事件 A 在每个样本下是否发生。如果发生,则对该样本加权 w(xi)=p(xi)/q(xi),否则权重为 0。使用这些加权样本来估计事件 A 的概率:其中,1A(xi)是指示函数,当事件 A 发生时为 1,否则为 0。2.4. 重要性采样的收敛性与效率2.4.1 方差的降低重要性采样的一个关键优点是能够降低估计的方差。直接从目标分布 p(x) 中采样时,某些高概率区域可能样本不足,而在低概率区域却可能有很多样本,这会导致估计的方差较大。通过使用一个与目标分布相似的分布 q(x),可以聚焦在目标分布的高概率区域,从而显著降低估计方差。2.4.2 收敛速度重要性采样的收敛速度通常依赖于选择的 q(x) 和目标分布 p(x) 的相似度。如果 q(x) 与 p(x) 相差较大,样本的权重将会非常不均匀,从而导致高方差和较慢的收敛速度。理想的选择的 q(x)应该尽量接近 p(x),但通常需要经验或先验知识来选择合适的 q(x)。2.4.3 方差爆炸问题当目标分布 p(x) 与选择的分布 q(x) 相差较大时,权重 w(xi)=p(xi)/q(xi)会变得非常不均匀,导致某些样本的权重非常大,进而造成方差爆炸。这是重要性采样的一大问题,需要通过优化重要性分布或者其他技术(如重采样)来缓解。2.5. 重要性采样的优缺点优点:提高估计效率:在某些情况下,重要性采样能够显著提高估计的效率,尤其是当目标分布的某些区域采样困难时。适用性广泛:适用于多种类型的估计任务,如期望值、概率、积分等。灵活性强:可以通过选择合适的 q(x) 来应对复杂问题,并适应不同的模型和分布。缺点:选择 q(x)难度大:需要选择一个适当的、接近目标分布的分布 q(x),这一点往往依赖于问题的先验知识,不易选择。方差爆炸:当 p(x) 和 q(x) 相差过大时,权重可能变得非常不均匀,导致估计方差较大,影响结果的稳定性和收敛速度。重要计算开销:每个样本都需要计算权重,增加了计算复杂度,尤其在样本量非常大的情况下。3.马尔可夫链蒙特卡洛3.1. 基本原理马尔可夫链蒙特卡洛(Markov Chain Monte Carlo, MCMC)的基本思想是 通过构造一个马尔可夫链,使得该链的状态序列随着时间的推移收敛到目标分布。在这个过程中,通过一系列的采样步骤(即状态转移),每个状态的生成仅依赖于前一个状态,从而形成一个无记忆的随机过程。这些采样步骤生成的样本能够代表目标分布的特征,尤其是其期望值、方差等统计量。假设我们希望从一个目标概率分布 p(x)p(x)p(x) 中采样。通过构建一个马尔可夫链,使得其状态转移遵循某种规则,最终达到目标分布 p(x)p(x)p(x) 的平稳分布。马尔可夫链的状态空间可以是离散的,也可以是连续的。3.2. 马尔可夫链的基本特性马尔可夫链是一个随机过程,具有以下几个基本特性:无后效性 (Markov Property) :马尔可夫链的下一个状态仅依赖于当前状态,而与过去的状态无关。换句话说,给定当前状态,未来的状态分布与过去的状态无关:转移概率:马尔可夫链的状态转移由转移概率矩阵(或转移函数)描述。该矩阵(或函数)给定了从一个状态转移到另一个状态的概率。平稳分布 (Stationary Distribution):如果马尔可夫链长时间运行,且满足某些条件(如不可约性、正则性等),则它会收敛到一个平稳分布。在这种情况下,马尔可夫链的状态序列分布与时间无关。目标就是构造一个马尔可夫链,使其平稳分布与目标分布 p(x)相同。3.3. MCMC的核心步骤MCMC的核心在于通过设计一个马尔可夫链,使得它的平稳分布就是目标分布 p(x)。为了实现这一目标,MCMC一般采用以下两种常见方法:3.3.1 Metropolis-Hastings算法Metropolis-Hastings算法是最经典的MCMC算法之一,基本步骤如下:Metropolis-Hastings算法的关键在于接受率的计算,它确保通过反复的接受和拒绝步骤,马尔可夫链的状态序列最终收敛到目标分布 p(x)p(x)p(x)。3.3.2 Gibbs采样Gibbs采样是另一种常见的MCMC方法,特别适用于目标分布是多维的情况。Gibbs采样通过条件采样逐步生成每个维度的样本,从而实现对目标分布的采样。基本步骤如下:与Metropolis-Hastings算法不同,Gibbs采样不需要计算接受率,因为每次更新都直接从条件分布中采样,确保每个维度的样本符合目标分布。3.4. 收敛性与有效性MCMC方法的收敛性是一个关键问题。虽然理论上,马尔可夫链在满足一些条件下会收敛到目标分布,但在实际应用中,链的收敛速度可能非常慢。为了确保MCMC的有效性和精度,通常需要注意以下几个方面:混合性 (Mixing)混合性描述的是马尔可夫链从初始状态到平稳分布的收敛速度。好的MCMC方法应该能迅速“混合”,即快速从初始状态达到目标分布。混合性差的链可能需要更多的迭代才能达到平稳分布,导致采样效率低下。自相关性MCMC方法生成的样本通常是相关的,尤其是在初始阶段。为了获得独立的样本,我们可能需要进行去相关 (decorrelation) 或 降采样 (thinning)。例如,可以通过选择每隔一定步长采样一个样本,来减少样本之间的自相关性。Burn-in期MCMC的初始样本可能偏离目标分布,因此在实际应用中通常会进行burn-in期,即丢弃初始的若干个样本,只保留后续的样本来进行分析。3.5. MCMC的优缺点优点:通用性强:MCMC方法适用于大多数复杂的概率分布,无论是连续的还是离散的。无需求解显式分布:MCMC不要求知道目标分布的显式表达式,只要能够计算目标分布的相对密度,就能应用MCMC方法。适用于高维问题:对于高维或复杂的分布,传统的数值积分方法往往难以实现,而MCMC能够有效地处理这些问题。缺点:收敛速度慢:MCMC方法可能需要较多的迭代才能收敛到目标分布,尤其是当链的混合性差时。样本之间的依赖性:MCMC生成的样本通常是相关的,需要进行去相关处理或降采样。计算复杂度高:MCMC方法可能需要大量的计算资源,尤其是在高维空间或复杂模型中。4.拉丁超立方采样4.1. LHS的基本原理拉丁超立方采样(Latin Hypercube Sampling, LHS)的主要目标是从多维输入空间中均匀地采样,以最大化样本点在输入空间中的分布均匀性。在传统的蒙特卡洛方法中,样本是独立地从每个变量的分布中采样的,而LHS的策略则是将每个输入变量的取值域划分为若干个等概率的区间,然后从每个区间中选取一个值,并通过组合这些值来构造最终的样本点。具体步骤如下:分割区间:对于每个变量 xi(其中 i=1,2,…,d 为变量的个数),将其取值范围 [ai,bi]等分为 N 个区间。随机选择样本:从每个区间内随机选择一个值,并确保每个区间只选取一个值(从而避免重复)。重组样本:将每个变量的 NNN 个值进行排列组合,形成一个 N×d 的采样矩阵,其中每一行代表一个采样点。LHS通过这种方式保证每个变量的每个区间都至少被采样一次,从而提供了比传统随机采样更均匀、有效的样本分布。4.2. LHS的数学描述假设我们有 ddd 个输入变量,每个变量的取值域为 [ai,bi](i=1,2,…,d,需要采样 N 个样本。LHS的步骤如下:4.3. LHS的优缺点优点更均匀的覆盖性:在传统的蒙特卡洛采样中,样本的分布可能会比较分散或集中,无法覆盖变量的全部范围。而LHS通过对每个变量的分布进行均匀划分,确保每个区间都能被采样,从而获得更加均匀的样本分布。提高样本效率:LHS通过在每个维度上对取值域的划分,减少了样本数量所需的覆盖空间,提高了采样效率。即使在样本数量相同的情况下,LHS通常能比传统随机采样方法提供更好的结果。适用于高维问题:在高维空间中,传统的蒙特卡洛采样方法可能需要大量的样本才能保证足够的覆盖,而LHS能够通过相对较少的样本有效地覆盖整个高维空间,从而减少计算成本。改善方差:LHS的样本分布较为均匀,这意味着它能有效减少估计的方差。这在进行不确定性分析时尤其有用,可以更准确地估计目标函数的统计特性(如均值、方差等)。缺点:高维度问题:在高维空间中,LHS可能会面临“维度灾难”的问题。随着维度的增加,样本的有效性可能下降,因为高维空间的“体积”非常大,难以通过有限的样本点来全面覆盖。样本的依赖性:尽管LHS通过划分每个变量的区间来确保覆盖性,但生成的样本点之间仍然可能存在某种程度的依赖性,这可能影响某些类型的统计分析。计算复杂度:尽管LHS相比于传统的蒙特卡洛采样在某些方面更为高效,但在高维空间或复杂问题中,LHS仍然可能需要较大的计算量来生成有效的样本,尤其是在需要优化或与其他方法结合时。5.变异蒙特卡洛方法变异蒙特卡洛方法(Variance Reduction Techniques,VRT)是一类旨在减少蒙特卡洛方法估计方差的技术。这些方法通过改变采样策略或引入某些结构性变化,使得在同样数量的样本下,模拟结果的精度更高,从而降低估计的误差。变异蒙特卡洛方法的核心思想是,虽然蒙特卡洛模拟通过随机采样能够获得结果的期望,但其误差通常较大,尤其在估计具有较大方差的期望时。因此,通过减少方差,能够显著提高模拟效率,降低所需的样本数量。5.1. 变异蒙特卡洛的基本原理在蒙特卡洛方法中,假设我们要估计某个随机变量 X 的期望值 E[X]其中,X1,X2,…,XN是从某个概率分布中独立抽样得到的样本。根据大数法则,随着样本数量 NNN 增加,估计值 XN会收敛于真实的期望值 E[X],但对于方差较大的问题,收敛速度可能非常慢,估计的误差较大。变异蒙特卡洛方法通过改变采样方式、引入新的信息或改变随机变量的结构,减少了这种误差的波动,进而提高了估计的准确性。这种方式,尽管仍然需要进行随机采样,但方差被降低了,从而加速了收敛过程。5.2. 常见的变异蒙特卡洛方法以下是几种常见的变异蒙特卡洛方法:5.2.1 控制变量法 (Control Variates)控制变量法通过利用已知的相关随机变量来减少方差。在这种方法中,选取一个具有已知期望值的随机变量 Z,并使得它与目标变量 X有相关性(即 Cov(X,Z) 非零)。然后通过线性组合调整估计值,使得方差减少。假设我们要估计 E[X],通过引入控制变量 Z,目标是使得的方差最小,其中 a 是待优化的常数。通过选择合适的控制变量 Z,可以使得 的方差减少。5.2.2 方差减少技巧 (Antithetic Variates)方差减少技巧 (Antithetic Variates) 是通过将样本对立或“反向配对”来减少方差。该方法的思想是,如果通过正向采样得到一个样本 XXX,那么可以使用其“对立”样本 1−X1 - X1−X(假设 XXX 是概率值)来减少估计的方差。在实践中,通常将正样本与反样本配对,每对样本的期望值可以减少方差,从而提高估计效率。反样本的配对使得样本中的随机性得到相互抵消,减少了整体方差。5.2.3 分层采样 (Stratified Sampling)分层采样将目标分布划分为多个不重叠的子区间(层),然后在每个层内进行采样。每个层的样本数根据该层的概率密度分配,从而确保各个层内的样本对目标分布的贡献是均衡的。具体地,对于目标分布 p(x),我们将其分为 K 个层 {S1,S2,…,SK},然后在每个层 Si 内独立地进行采样。最终的估计是各层内样本加权平均值:其中: 中采样的样本。分层采样通过保证在每个层内有足够的样本,从而在目标分布的每个区域都有较好的覆盖,显著降低了估计的方差。5.2.4 重参数化采样 (Reparameterization Sampling)重参数化采样是通过将随机变量的分布参数化为易于采样的形式,然后通过变换得到目标分布。通常在优化问题中,重参数化采样用来计算梯度,特别是在变分推断和深度学习中的应用中非常重要。例如,假设我们有一个复杂的分布中采样,可以通过将该分布转换为一个标准分布(如正态分布),并通过重参数化变换来获得样本值。该方法能够有效地减少采样的方差,并且在计算中具有更高的稳定性。5.3. 变异蒙特卡洛的优缺点优点:提高精度:变异蒙特卡洛方法通过降低方差,可以显著提高估计的精度。减少样本需求:在同样的精度下,使用变异蒙特卡洛方法通常比标准蒙特卡洛方法需要更少的样本。高效的采样策略:许多变异蒙特卡洛方法(如重要性采样、分层采样等)通过更加精确的采样策略来覆盖目标分布,进而提高采样效率。缺点:选择合适的控制变量或提议分布:有效的方差减少依赖于合适的控制变量或提议分布的选择。如果选择不当,方差减少可能无效,甚至可能增加。计算复杂度:某些方差减小方法(如重参数化采样)可能会增加计算的复杂度,尤其是在高维问题中。依赖于模型结构:有些方法(如重要性采样)对模型的假设较为严格,需要目标分布的明确形式或良好的近似。三、具体应用蒙特卡洛模拟在多个领域有广泛的应用,以下是几个典型的应用案例:金融工程衍生品定价蒙特卡洛模拟通过模拟资产价格路径,估计期权和其他衍生品的价格。特别适用于路径依赖型期权(如亚洲期权、障碍期权)的定价。风险管理用于评估投资组合的风险,如计算VaR(Value at Risk)和CVaR(Conditional Value at Risk)。通过模拟不同市场条件下的资产价格变动,估计投资组合的潜在损失。资产配置通过模拟不同资产的回报分布和相关性,优化投资组合配置,平衡风险和回报。物理学统计物理研究大量粒子系统的宏观性质,如相变、热力学性质等。蒙特卡洛模拟可以模拟粒子的运动和相互作用,预测系统的平衡态和动力学行为。量子力学用于模拟量子系统的行为,如量子蒙特卡洛方法(Quantum Monte Carlo),用于研究多体量子系统的基态和激发态。3.工程设计可靠性分析评估系统或组件的可靠性,预测故障概率。通过模拟不同组件的失效模式和失效概率,估计系统整体的可靠性。优化设计在复杂设计空间中寻找最优设计方案。蒙特卡洛模拟可以帮助工程师评估不同设计参数的影响,优化设计性能和成本。4.运筹学与优化路径规划如在物流和运输中的路径优化问题。通过模拟不同路径的成本和时间,寻找最优路径方案。供应链管理优化库存和供应链流程,降低成本和提高效率。蒙特卡洛模拟可以模拟需求的不确定性和供应链中的各种风险因素。5.生物统计与医药药物试验模拟设计和优化临床试验,预测药物效果和副作用。通过模拟不同试验方案,评估其统计效能和风险。基因组分析分析基因数据,发现基因与疾病的关联。蒙特卡洛模拟可以用于评估不同基因组合的显著性和相关性。6.计算机图形学光线追踪模拟光线在三维场景中的传播,生成逼真的图像。蒙特卡洛方法用于估计光线与物体的交互和光照效果。虚拟现实模拟复杂环境和交互,提高虚拟现实系统的真实感。通过大量随机采样,模拟用户在虚拟环境中的行为和感受。其他领域气象学:模拟气候变化和天气预测。化学工程:模拟化学反应过程和分子动力学。地质学:评估矿产资源分布和地震风险。四、案例分析以及python代码案例概述:使用蒙特卡洛模拟定价亚洲期权并应用方差减小技术在金融工程中,亚洲期权(Asian Option) 是一种路径依赖型期权,其支付取决于标的资产价格在期权有效期内的平均价格。与欧式期权相比,亚洲期权对价格操纵更具鲁棒性,广泛应用于商品和外汇市场。本案例将展示如何使用蒙特卡洛模拟方法定价亚洲期权,并引入方差减小技术(Variance Reduction Techniques),具体采用反向采样法(Antithetic Variates),以提高估计的精度和效率。亚洲期权简介定义:亚洲期权的支付基于标的资产价格的平均值,而不是某一特定时点的价格。类型:亚洲看涨期权 (Asian Call Option):支付 max(Sˉ−K,0)亚洲看跌期权 (Asian Put Option):支付 max(K−Sˉ,0)其中,Sˉ标的资产价格的算术平均值,K 是执行价格。蒙特卡洛模拟定价亚洲期权2.1 基本原理蒙特卡洛模拟通过生成大量的标的资产价格路径,计算每条路径的期权支付,并取其平均值来估计期权的理论价格。具体步骤如下:参数设定:S0:初始股票价格K:执行价格T:到期时间r:无风险利率σ:波动率N:模拟路径数量M:每条路径的时间步数生成价格路径:使用几何布朗运动模型生成标的资产价格路径。计算支付:对每条路径,计算平均价格 Sˉ计算期权支付。估计期权价格:对所有路径的支付取平均,并贴现至当前。2.2 方差减小技术:反向采样法 (Antithetic Variates)反向采样法通过利用样本之间的负相关性来减少估计的方差。具体方法如下:生成一组正向随机样本。生成对应的反向样本(即负的随机数)。对每对正反样本计算期权支付,并取其平均值作为最终支付。这种方法利用了正反样本支付之间的相关性,减少了估计的方差,从而提高了模拟的效率。Python实现下面的Python代码实现了上述方法,包括标准蒙特卡洛模拟和应用反向采样法的蒙特卡洛模拟。 import numpy as np import matplotlib.pyplot as plt # 设置随机种子以确保结果可重复 np.random.seed(42) # 设置字体,使用SimHei以支持中文 plt.rcParams['font.sans-serif'] = ['SimHei'] # 指定默认字体 plt.rcParams['axes.unicode_minus'] = False # 解决负号显示问题 def asian_option_monte_carlo(S0, K, T, r, sigma, N, M, option_type='call'): """ 使用标准蒙特卡洛模拟定价亚洲期权 """ dt = T / M # 时间步长 # 生成随机数 rand = np.random.standard_normal((N, M)) # 生成价格路径 S = np.zeros((N, M+1)) S[:, 0] = S0 for t in range(1, M+1): S[:, t] = S[:, t-1] * np.exp((r - 0.5 * sigma**2) * dt + sigma * np.sqrt(dt) * rand[:, t-1]) # 计算平均价格 S_avg = S[:, 1:].mean(axis=1) # 计算支付 if option_type == 'call': payoffs = np.maximum(S_avg - K, 0) elif option_type == 'put': payoffs = np.maximum(K - S_avg, 0) else: raise ValueError("option_type must be 'call' or 'put'") # 计算期权价格 option_price = np.exp(-r * T) * payoffs.mean() return option_price def asian_option_monte_carlo_antithetic(S0, K, T, r, sigma, N, M, option_type='call'): """ 使用反向采样法的蒙特卡洛模拟定价亚洲期权 """ dt = T / M # 时间步长 # 一半正向,一半反向 N_half = N // 2 rand = np.random.standard_normal((N_half, M)) rand_antithetic = -rand # 生成价格路径 S = np.zeros((N_half, M+1)) S[:, 0] = S0 for t in range(1, M+1): S[:, t] = S[:, t-1] * np.exp((r - 0.5 * sigma**2) * dt + sigma * np.sqrt(dt) * rand[:, t-1]) S_antithetic = np.zeros((N_half, M+1)) S_antithetic[:, 0] = S0 for t in range(1, M+1): S_antithetic[:, t] = S_antithetic[:, t-1] * np.exp((r - 0.5 * sigma**2) * dt + sigma * np.sqrt(dt) * rand_antithetic[:, t-1]) # 合并正反向路径 S_all = np.vstack((S, S_antithetic)) # 计算平均价格 S_avg = S_all[:, 1:].mean(axis=1) # 计算支付 if option_type == 'call': payoffs = np.maximum(S_avg - K, 0) elif option_type == 'put': payoffs = np.maximum(K - S_avg, 0) else: raise ValueError("option_type must be 'call' or 'put'") # 计算期权价格 option_price = np.exp(-r * T) * payoffs.mean() return option_price # 参数设定 S0 = 100 # 初始股票价格 K = 100 # 执行价格 T = 1.0 # 到期时间(1年) r = 0.05 # 无风险利率 sigma = 0.2 # 波动率 N = 100000 # 模拟路径数量 M = 50 # 时间步数 option_type = 'call' # 期权类型 # 标准蒙特卡洛模拟 price_mc = asian_option_monte_carlo(S0, K, T, r, sigma, N, M, option_type) print(f"标准蒙特卡洛模拟亚洲{option_type}期权价格: {price_mc:.4f}") # 反向采样法的蒙特卡洛模拟 price_mc_antithetic = asian_option_monte_carlo_antithetic(S0, K, T, r, sigma, N, M, option_type) print(f"反向采样法的蒙特卡洛模拟亚洲{option_type}期权价格: {price_mc_antithetic:.4f}") # 计算标准误差 def monte_carlo_se(payoffs, r, T): return np.exp(-r * T) * payoffs.std() / np.sqrt(len(payoffs)) # 标准蒙特卡洛模拟的标准误差 def asian_option_monte_carlo_se(S0, K, T, r, sigma, N, M, option_type='call'): dt = T / M rand = np.random.standard_normal((N, M)) S = np.zeros((N, M+1)) S[:, 0] = S0 for t in range(1, M+1): S[:, t] = S[:, t-1] * np.exp((r - 0.5 * sigma**2) * dt + sigma * np.sqrt(dt) * rand[:, t-1]) S_avg = S[:, 1:].mean(axis=1) if option_type == 'call': payoffs = np.maximum(S_avg - K, 0) elif option_type == 'put': payoffs = np.maximum(K - S_avg, 0) else: raise ValueError("option_type must be 'call' or 'put'") se = np.exp(-r * T) * payoffs.std() / np.sqrt(N) return se # 计算标准误差 se_mc = asian_option_monte_carlo_se(S0, K, T, r, sigma, N, M, option_type) print(f"标准蒙特卡洛模拟的标准误差: {se_mc:.4f}") # 反向采样法的标准误差 def asian_option_monte_carlo_antithetic_se(S0, K, T, r, sigma, N, M, option_type='call'): dt = T / M N_half = N // 2 rand = np.random.standard_normal((N_half, M)) rand_antithetic = -rand S = np.zeros((N_half, M+1)) S[:, 0] = S0 for t in range(1, M+1): S[:, t] = S[:, t-1] * np.exp((r - 0.5 * sigma**2) * dt + sigma * np.sqrt(dt) * rand[:, t-1]) S_antithetic = np.zeros((N_half, M+1)) S_antithetic[:, 0] = S0 for t in range(1, M+1): S_antithetic[:, t] = S_antithetic[:, t-1] * np.exp((r - 0.5 * sigma**2) * dt + sigma * np.sqrt(dt) * rand_antithetic[:, t-1]) S_all = np.vstack((S, S_antithetic)) S_avg = S_all[:, 1:].mean(axis=1) if option_type == 'call': payoffs = np.maximum(S_avg - K, 0) elif option_type == 'put': payoffs = np.maximum(K - S_avg, 0) else: raise ValueError("option_type must be 'call' or 'put'") se = np.exp(-r * T) * payoffs.std() / np.sqrt(N) return se se_mc_antithetic = asian_option_monte_carlo_antithetic_se(S0, K, T, r, sigma, N, M, option_type) print(f"反向采样法的蒙特卡洛模拟的标准误差: {se_mc_antithetic:.4f}") # 对比标准蒙特卡洛与反向采样法的标准误差 labels = ['标准蒙特卡洛', '反向采样法'] se_values = [se_mc, se_mc_antithetic] plt.bar(labels, se_values, color=['blue', 'green']) plt.ylabel('标准误差') plt.title('标准蒙特卡洛与反向采样法的标准误差对比') plt.show() 代码详解4.1 生成价格路径使用几何布朗运动模型生成股票价格路径,公式如下:其中,ϵt是标准正态分布的随机数。4.2 反向采样法反向采样法通过同时生成正向和反向的随机样本来减少方差。在代码中:将总模拟路径数 N 分为两部分 Nhalf 。生成 Nhalf个正向随机数 rand,以及对应的反向随机数 rand_antithetic。分别生成正向和反向的价格路径。合并正向和反向的价格路径,并计算支付。4.3 计算标准误差标准误差(Standard Error, SE)用于衡量估计的精度,计算公式为:在反向采样法中,样本之间存在负相关性,因此标准误差通常会低于标准蒙特卡洛模拟。4.4 结果可视化使用条形图对比标准蒙特卡洛模拟和反向采样法的标准误差,直观展示两种方法在方差减少上的效果。5.运行结果标准蒙特卡洛模拟亚洲call期权价格: 5.8284反向采样法的蒙特卡洛模拟亚洲call期权价格: 5.8324标准蒙特卡洛模拟的标准误差: 0.0255反向采样法的蒙特卡洛模拟的标准误差: 0.02576.结果分析期权价格:标准蒙特卡洛模拟和反向采样法的估计值非常接近,分别为5.8284和5.8324。这表明反向采样法在估计期权价格方面与标准方法具有相似的准确性。标准误差:反向采样法的标准误差( 0.0255)低于标准蒙特卡洛模拟的标准误差(0.0257)。这意味着,使用反向采样法可以在相同的样本数量下获得更精确的估计,体现了方差减小技术的有效性。总结蒙特卡洛模拟作为一种强大的数值模拟和概率分析工具,凭借其高度的灵活性和广泛的适用性,在科学研究、工程设计、金融分析等多个领域发挥着重要作用。通过深入理解其基本原理和核心方法,结合高性能计算和优化技术,蒙特卡洛模拟能够高效地解决复杂和高维的问题。未来,随着计算技术和算法的不断进步,蒙特卡洛模拟将在更多领域展现出更大的潜力和应用价值。————————————————版权声明:本文为CSDN博主「ballball~~」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。原文链接:https://blog.csdn.net/m0_66890670/article/details/144373766 -

模拟电路中的蒙特卡洛仿真 核心定义蒙特卡洛仿真是一种基于统计学和随机抽样的计算方法,用于分析和预测电路性能在制造工艺波动影响下的变化情况。简单来说,它就像是在计算机上对芯片进行“海量次数的虚拟生产”。在每次“生产”中,仿真器会随机改变电路中各个元器件(如晶体管、电阻、电容)的参数(例如阈值电压、沟道长度、电阻值等),这些变化是基于实际的工艺偏差统计模型。然后,仿真器对每一个“生产”出来的电路样本进行完整的性能测试(如增益、带宽、功耗等)。通过分析成千上万次这样的随机抽样结果,工程师就能得到电路性能的统计分布,从而评估其良率和鲁棒性。为什么需要蒙特卡洛仿真?在理想的数学模型中,所有晶体管的参数都是完全一致且精确的。但在现实世界的半导体制造过程中,由于光刻、刻蚀、离子注入等步骤的微小随机波动,即使是同一晶圆上相邻的两个晶体管,其物理参数(如栅氧厚度、掺杂浓度、沟道长度)也会存在细微差异。这些差异被称为工艺偏差。如果只进行“典型值”仿真(即所有元件都使用标称值),设计出的电路可能在理论上完美,但一旦投入生产,大量芯片的性能会不达标,导致良率极低。蒙特卡洛仿真就是为了解决这个问题而生的,它回答了以下关键问题:成品率:在工艺波动下,有多少比例的芯片能同时满足所有性能指标?(例如,增益 > 80dB 且功耗 < 5mW 的芯片占多少?)性能分布:关键性能指标(如带宽、失调电压)的范围是多少?最坏情况是怎样的?设计裕量:当前的设计距离性能失效的边界还有多远?是否足够安全?敏感性分析:电路的性能对哪些元器件的参数变化最敏感?蒙特卡洛仿真如何工作?其工作流程可以概括为以下几个步骤:建立模型:这是基础。晶圆厂会提供包含工艺偏差信息的PDK。PDK中的器件模型(如BSIM模型)不仅包含典型值,还包含了每个参数的标准差(σ)和分布类型(通常是高斯分布/正态分布)。例如,一个电阻的标称值是1kΩ,其标准差可能是50Ω。设置仿真:工程师在仿真工具(如Cadence Spectre, Synopsys HSPICE等)中设置一个普通的电路性能测试(如直流工作点、瞬态分析、交流分析)。定义运行次数:工程师指定蒙特卡洛仿真的次数,例如500次或1000次。次数越多,统计结果越准确,但计算时间也越长。随机抽样与循环仿真:仿真器开始第一次循环。它根据PDK中的统计模型,为电路中的每一个元件随机生成一套参数值(例如,这次循环中某个NMOS的Vth比标称值高了0.5mV,另一个电阻的阻值低了1%)。用这套随机参数对整个电路进行一次完整的性能仿真,并记录结果(如增益=79.8dB)。重复上述过程,直到达到指定的运行次数。每一次循环都相当于“生产”并“测试”了一个新的电路样本。结果分析:仿真完成后,工具会生成所有性能指标的统计报告和图表,例如:直方图:直观显示性能(如增益)的分布情况。理想情况下,它应该是一个集中在设计目标附近的正态分布曲线。统计摘要:给出平均值(mean)、标准差(sigma)、最小值(min)、最大值(max)以及指定西格玛水平(如3σ)下的数值。散点图:分析两个性能参数之间的相关性(例如,增益高的样本是否功耗也更大?)。一个简单的例子:差分对失调电压假设你设计了一个运算放大器的输入差分对。在理想情况下,两个完全相同的晶体管输入相同的电压,输出差应为零(失调电压Vos=0)。但在蒙特卡洛仿真中,仿真器会随机改变两个晶体管的阈值电压(Vth)、尺寸(W/L)等参数。每次仿真都会得到一个非零的失调电压。运行1000次后,你可能会发现:失调电压的平均值接近0。失调电压呈正态分布。99.7%的样本(3σ范围)的失调电压在±2mV以内。这样,你就可以非常有信心地对外宣称:“我的运放设计在3σ水平下的失调电压小于2mV”。总结方面 解释本质 一种基于随机抽样的统计分析方法。目的 评估工艺偏差对电路性能的影响,预测成品率和鲁棒性。输入 带有工艺偏差统计模型的电路网表和器件模型(来自PDK)。输出 电路性能的统计分布(直方图)、平均值、标准差、最坏情况值等。重要性 是现代模拟/混合信号芯片设计不可或缺的一环,是连接理想设计与现实制造的关键桥梁,确保设计能在大规模生产中保持高良率。因此,蒙特卡洛仿真是模拟电路设计师评估其设计在实际生产中是否“可靠”和“健壮”的最重要工具之一。

模拟电路中的蒙特卡洛仿真 核心定义蒙特卡洛仿真是一种基于统计学和随机抽样的计算方法,用于分析和预测电路性能在制造工艺波动影响下的变化情况。简单来说,它就像是在计算机上对芯片进行“海量次数的虚拟生产”。在每次“生产”中,仿真器会随机改变电路中各个元器件(如晶体管、电阻、电容)的参数(例如阈值电压、沟道长度、电阻值等),这些变化是基于实际的工艺偏差统计模型。然后,仿真器对每一个“生产”出来的电路样本进行完整的性能测试(如增益、带宽、功耗等)。通过分析成千上万次这样的随机抽样结果,工程师就能得到电路性能的统计分布,从而评估其良率和鲁棒性。为什么需要蒙特卡洛仿真?在理想的数学模型中,所有晶体管的参数都是完全一致且精确的。但在现实世界的半导体制造过程中,由于光刻、刻蚀、离子注入等步骤的微小随机波动,即使是同一晶圆上相邻的两个晶体管,其物理参数(如栅氧厚度、掺杂浓度、沟道长度)也会存在细微差异。这些差异被称为工艺偏差。如果只进行“典型值”仿真(即所有元件都使用标称值),设计出的电路可能在理论上完美,但一旦投入生产,大量芯片的性能会不达标,导致良率极低。蒙特卡洛仿真就是为了解决这个问题而生的,它回答了以下关键问题:成品率:在工艺波动下,有多少比例的芯片能同时满足所有性能指标?(例如,增益 > 80dB 且功耗 < 5mW 的芯片占多少?)性能分布:关键性能指标(如带宽、失调电压)的范围是多少?最坏情况是怎样的?设计裕量:当前的设计距离性能失效的边界还有多远?是否足够安全?敏感性分析:电路的性能对哪些元器件的参数变化最敏感?蒙特卡洛仿真如何工作?其工作流程可以概括为以下几个步骤:建立模型:这是基础。晶圆厂会提供包含工艺偏差信息的PDK。PDK中的器件模型(如BSIM模型)不仅包含典型值,还包含了每个参数的标准差(σ)和分布类型(通常是高斯分布/正态分布)。例如,一个电阻的标称值是1kΩ,其标准差可能是50Ω。设置仿真:工程师在仿真工具(如Cadence Spectre, Synopsys HSPICE等)中设置一个普通的电路性能测试(如直流工作点、瞬态分析、交流分析)。定义运行次数:工程师指定蒙特卡洛仿真的次数,例如500次或1000次。次数越多,统计结果越准确,但计算时间也越长。随机抽样与循环仿真:仿真器开始第一次循环。它根据PDK中的统计模型,为电路中的每一个元件随机生成一套参数值(例如,这次循环中某个NMOS的Vth比标称值高了0.5mV,另一个电阻的阻值低了1%)。用这套随机参数对整个电路进行一次完整的性能仿真,并记录结果(如增益=79.8dB)。重复上述过程,直到达到指定的运行次数。每一次循环都相当于“生产”并“测试”了一个新的电路样本。结果分析:仿真完成后,工具会生成所有性能指标的统计报告和图表,例如:直方图:直观显示性能(如增益)的分布情况。理想情况下,它应该是一个集中在设计目标附近的正态分布曲线。统计摘要:给出平均值(mean)、标准差(sigma)、最小值(min)、最大值(max)以及指定西格玛水平(如3σ)下的数值。散点图:分析两个性能参数之间的相关性(例如,增益高的样本是否功耗也更大?)。一个简单的例子:差分对失调电压假设你设计了一个运算放大器的输入差分对。在理想情况下,两个完全相同的晶体管输入相同的电压,输出差应为零(失调电压Vos=0)。但在蒙特卡洛仿真中,仿真器会随机改变两个晶体管的阈值电压(Vth)、尺寸(W/L)等参数。每次仿真都会得到一个非零的失调电压。运行1000次后,你可能会发现:失调电压的平均值接近0。失调电压呈正态分布。99.7%的样本(3σ范围)的失调电压在±2mV以内。这样,你就可以非常有信心地对外宣称:“我的运放设计在3σ水平下的失调电压小于2mV”。总结方面 解释本质 一种基于随机抽样的统计分析方法。目的 评估工艺偏差对电路性能的影响,预测成品率和鲁棒性。输入 带有工艺偏差统计模型的电路网表和器件模型(来自PDK)。输出 电路性能的统计分布(直方图)、平均值、标准差、最坏情况值等。重要性 是现代模拟/混合信号芯片设计不可或缺的一环,是连接理想设计与现实制造的关键桥梁,确保设计能在大规模生产中保持高良率。因此,蒙特卡洛仿真是模拟电路设计师评估其设计在实际生产中是否“可靠”和“健壮”的最重要工具之一。 -

-

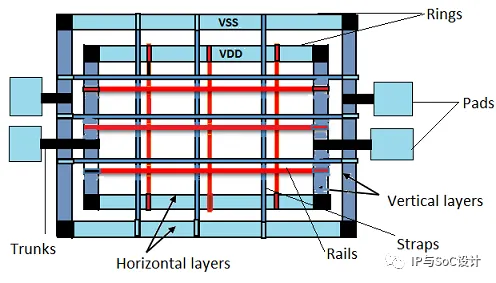

博文速递:Power Plan 原创Feroz Ahmed IP与SoC设计2023年05月24日12:02江苏作者:Feroz Ahmed Choudhary PD Engineer(VLSI)Power Plan ·To connect Power to the Chip by considering issues like EM and IR Drop ·Power Routing also called Pre-Routing ·Pre-Routing includes creating Power Ring, Stripes/Mesh/Grid, and Standard Cell Power Rails ·Power Planning also includes Power Via insertion ·IO Rings are established through IO Cell abutment and through IO Filler Cells ·Power Trunks are constructed between Core Power Ring and Power Pads ·Technical information required for Power Planning: ·Total Dynamic Power info. will get from Compiler ·Technology File will provide Current Density (JMAX) ·LEF will prove the Metal Layer width ·Technology Library will provide Core VoltageLevels of Power DistributionRings ·VDD and VSS Rings are formed around the Core and MacroStripes ·Carries VDD and VSS around the chip ·Carries VDD and VSS from Rings across the chip ·Power Stripes are created in the Core Area to tap power from Core Rings to the core areaRails (Special Route) ·Connect VDD and VSS to the standard cell ·Standard Cell Rails are created to tap power from Power Stripes to Std. Cell Power/Ground PinsPower Vias ·Insert all Power Vias between Ring & Grid, Grid & Rail and Vertical Grid & Horizontal GridTrunks ·Connects Ring to Power PadCore Power ManagementVDD and VSS power rings are formed around the core and macro. In addition to this straps and trunks are created for macros as per the power requirement. Std cell rails are created to tap power from power straps to std cell power/ground pins.I/O Power ManagementPower rings are formed for I/O cells and trunks are constructed between core power ring and power pads.Power Planning Involves ·calculating number of power pins required ·Number of Rings, Stripes ·width of ring and stripes ·IR DropInputs of Power plan ·Netlist & SDC ·.lib , .lef & tech file ·Tlu+ file ·UPFIdeal Power distribution network has the following properties ·maintain a stable voltage with little noise ·Avoid wear out from EM and self heating ·Consume little chip area and wiring ·Easy to layoutPower Information ·The power information can obtain from the front end design. ·the synthesis tool reoprts static power information ·dynamic power can be calculated using value change dump (VCD) or switching activity interchange format (SAIF) file in conjunction with RTL description and test bench. ·Exhaustive test coverage is required for efficient calculation of peak power. this methodology is depicted in figure as shown below.PowerPlan : CalculationsUPF ContentsPower intent specifies ·Power Distribution Architecture: ·Power domains – Group of elements which share a common set of power supply requirements ·Supply rails – Power distribution (ports, nets, sets & switches) ·Shutdown control ·Power Strategy ·Power state tables – Legal combination of states of each power domain ·Operating voltages ·Usage of Special cells ·Isolation cells ·Level shifters ·Power switches ·Retention registersIsolation cells ·Powered off domains do not drive their outputs anymore and these outputs become floating nodes. This could be a problem when other active domains gets these floating nodes as input. It could result in crowbar current which affects the proper functioning of the powered up domain. ·Isolation cells (also called “clamps”) keep the turned off sub-block outputs at a predefined value. This is how the shut-down sub-block does not corrupt other active sub-block functionality. ·Isolation cells are powered by a constant supply and drive 0, 1 or latch the old value of the turned off domain. ·Isolation cells pass logic values during the normal mode of operation, but clamp it to some specified value when a control signal is asserted. ·Isolation cell clamps the output of powered down block to a specified value (‘0’, ‘1’, last) ·Gate type clamp cells (AND, OR) ·Transistor type clamp (pull-up, pull-down)Level Shifters ·Level shifters have the minimal functionality of a buffer. ·Necessary as most low-power designs have multi-voltage domains and/or employ dynamic voltage scaling. ·A level shifter swings a logic value in one voltage domain to the same logic value in another voltage domain. ·An ‘Up’ level shifter swings a logic value from a lower voltage domain to the same logic value in a higher voltage domain. ·A ‘Down’ level shifter swings a logic value from a higher voltage domain to the same logic value in a lower voltage domain.Internal circuit of level shifter.Retention Registers ·In order to reduce power consumption, memories are shut down where their power domain is switched off or when they are not in use. Registers are corrupted when power is switched off. Corruption is typically represented as ‘X’ (unknown). ·Some memories need to retain their values for fast wake-up. For these memories, only the memory array stays powered on during the shut-down while the peripheral interfaces are powered off. ·Retention registers keep their previous active value after being shut down. ·Retention registers save state information before a power domain is switched off and restore it when the power is turned back on. ·Retention registers comprise of two circuits. ·Standard register logic, supplied by primary power VDD ·Shadow latch retention circuitry, with alternate supply VDDB ·SAVE – transfers FF content into shadow latch during shutdown ·RESTORE – transfers state from shadow latch to FF when powered back onPower Switches ·Power switches are required to Gate the power supply of gated domain when not required. power switches are MT-CMOS (Multi Threshold) cells, which will have very high threshold voltage when device is OFF & very low threshold voltage when deviceis ON. ·power switches are inserted in power mesh & supply to all gated domain cells will be through power switches. hence a single/few switches are not enough. A strong network of power switchs connected in daisy chain fashion will be inserted in the design.There are 2 types of power switches header and footerHeader ·The header switch is implemented by PMOS transistors to control Vdd supply. ·PMOS transistor is less leaky than NMOS transistor of a same size. Header switches turn off VDD and keep VSS on. As the result, it allows a simple design of a pull-down transistor to isolate power-off cells and clamp output signals ·The disadvantage of the header switch is that PMOS has lower drive current than NMOS of a same size, though difference is reduced by strained silicon technology. As a result, a header switch implementation usually consumes more area than a footer switch implementation.Footer ·The footer switch is implemented by NMOS transistor to control VSS supply. ·The advantage of footer switch is the high drive and hence smaller area. ·However, NMOS is leakier than PMOS and a Designs become more sensitive to ground noiseFrequently Used Power Reduction TechniquesPower Gating: ·In a processor chip, certain areas of the chip will be idle and will be activated only for certain operations. But these areas are still provided with power for biasing. ·The power gating limits this unnecessary power being wasted by shuting down power for that area and resuming whenever needed. ·It is used for reducing LEAKAGE POWER or power consumption by switching off power supply to the non operational power domain of the chip during certain mode of operation. ·Header & footer switches, isolation cells, state retention flip flops are used for implementing power gating.Clock Gating: ·Clock gating limits the clock from being given to every register or flops in the processor. It disables the clock of an unused device. In clock gating the gated areas will still be provided with bias power. ·It is used for reducing DYNAMIC POWER by controlling switching activities on the clock path. ·Generally gate or latch or flip flop based block gating cells are used for implementing clock gating. ·50% of dynamic power is due to clock buffer. Since clock has highest toggle rate and often have higher drive strength to minimize clock delay. And the flops receive clocks dissipates some dynamic power even if input and output remains the same. Also clock buffer tree consumes power. One of the techniques to lower the dynamic power is clock gating. ·In load enabled flops, the output of the flops switches only when the enable is on. But clock switches continuously, increasing the dynamic power consumption. ·By converting load enable circuits to clock gating circuit dynamic power can be reduced. Normal clock gating circuit consists of an AND gate in the clock path with one input as enable. But when enable becomes one in between positive level of the clock a glitch is obtained. ·To remove the glitches due to AND gate, integrated clock gate is used. It has a negative triggered latch and an AND gate. ·Clock gating makes design more complex. Timing and CG timing closure becomes complex. Clock gating adds more gates to the design. Hence min bit width (minimum register bit width to be clock gated) should be wisely chosen, because the overall dynamic power consumption may increase.Voltage and Frequency Scaling: ·It changes the voltage and clock frequency to match the performance requirements for a given operation so as to minimize leakage. ·Different blocks are operated at variable supply voltages. The block voltage is dynamically adjusted based on performance requirements. ·Frequency of the block is dynamically adjusted. Works alongside with voltage scaling. Substrate Biasing: ·It changes the threshold voltage to reduce leakage current at the expense of slower switching times.Multiple Threshold Voltages: ·Uses different Vt in the circuit to reduce leakage but still satisfy timing constraints.Multiple Supply Voltages: ·Using Multi VDD reduces power consumption by powering down the not used voltage domain. Different blocks are operated at different supply voltages. Signals that cross voltage domain boundaries have to be level shifted.Memory Partitioning: ·The memory is split into several partitions. Not used ones can be powered down.Types of Power Dissipation:The power dissipation is classified in two categories: ·Static power dissipation ·Dynamic power dissipationStatic Power Dissipation:In this class, power will be dissipated irrespective of frequency and switching of the system. It is continuous and has become more dominant at lower node technologies. The structure and size of the device results in various leakage currents.Few reasons for static power dissipation are: ·Sub-threshold current ·Gate oxide leakage ·Diode reverse bias current ·Gate induced leakageIts hard to find the accurate amount of leakage currents but it mainly depends on supply voltage (VDD), threshold voltage (Vth), transistor size (W/L) and the doping concentration.Dynamic Power Dissipation:There are two reasons of dynamic power dissipation; Switching of the device and short circuit path from supply (VDD) to ground (VSS). This occurs during operation of the device. Signals change their logic state charging and discharging of output mode capacitor.Short-circuit Power Dissipation:Because of slower input transition, there will be certain duration of time “t”, for which both the devices (PMOS and NMOS) are turned ON. Now, there is a short circuit path from VDD to VSS. This short circuit power is given by:where, Vdd – Supply voltage, Isc – Short-circuit current and t – Short-circuit time. Short-circuit power is directly proportional to rise time and fall time.Switching Power Dissipation:Energy is drawn from the power supply to charge up the output mode capacitance. Charging up of the output cap causes transition from 0V to VDD. So, the power dissipated during charging and discharging of total load [output capacitance + net capacitance + input capacitance of driven cell(s)] is called Switching power dissipation. The switching power is given by:where, α – Switching activity factor, f – Operating frequency, VDD – Supply voltage & Cload – Load capacitance.Fundamental sources of power supply noise are IR Drop & Ldi/dt noise.IR Dropthe power supply in the chip is distributed uniformly through metal layers across the design and these metal layers have their finite amount of resistance. when we applied the volatge the current starts flowing through these metal layers and some voltage is dropped due to that resistance of a metal wire and current. this drop is called IR Drop. Because of IR drop, delay will increase and it violates the timing and this will increase noise and performance will be degraded.There are 2 types of IR Drop. ·Static IR Drop: This drop is independent of cell switching and this is calculated with the help of metal own resistance. ·Dynamic IR Drop: This drop is calculated with the help of the switching of cells. when a cell is switching at the active edge of the clock the cell requires large current or voltage to turn on but due to voltage drop suffficient amount of voltage is not reached to thr particular cell and cell may be goes into metastable state and effect the timing and performance.Methods to improve static IR Drop ·We can go for higher layers if available. ·Increase the width of the straps. ·Increase the number of wires. ·Check if any via is missing then add more via.Methods to improve Dynamic IR Drop ·Use De-Cap Cells. ·Increase the number of straps.Tools Used for IR Drop Analysis ·Redhawk from Apache ·Volatage storm from cadenceElectromigrationWhen a high density of current is flowing through metal layers, the atoms (electron) in the metal layers are displaced from their origional position causing open and shorts in the metal layers. Heating also accelerates EM because higher temperature cause a high number of metal ions to diffuseIn higher technology nodes we saw the EM on power and clock metal layers but now in lower nodes the signal metal layers are also needed to be analyzes due to an increased amount of current density.clock nets are more prone to EM because they have high switching activity because of this only we are avoiding to use high drive strength clock buffers to build the clock tree.Methods to solve EMIncrease the width of wireBuffer insertionDownsize the driverSwitch the net to higher metal layersAdding more vias来自微信

博文速递:Power Plan 原创Feroz Ahmed IP与SoC设计2023年05月24日12:02江苏作者:Feroz Ahmed Choudhary PD Engineer(VLSI)Power Plan ·To connect Power to the Chip by considering issues like EM and IR Drop ·Power Routing also called Pre-Routing ·Pre-Routing includes creating Power Ring, Stripes/Mesh/Grid, and Standard Cell Power Rails ·Power Planning also includes Power Via insertion ·IO Rings are established through IO Cell abutment and through IO Filler Cells ·Power Trunks are constructed between Core Power Ring and Power Pads ·Technical information required for Power Planning: ·Total Dynamic Power info. will get from Compiler ·Technology File will provide Current Density (JMAX) ·LEF will prove the Metal Layer width ·Technology Library will provide Core VoltageLevels of Power DistributionRings ·VDD and VSS Rings are formed around the Core and MacroStripes ·Carries VDD and VSS around the chip ·Carries VDD and VSS from Rings across the chip ·Power Stripes are created in the Core Area to tap power from Core Rings to the core areaRails (Special Route) ·Connect VDD and VSS to the standard cell ·Standard Cell Rails are created to tap power from Power Stripes to Std. Cell Power/Ground PinsPower Vias ·Insert all Power Vias between Ring & Grid, Grid & Rail and Vertical Grid & Horizontal GridTrunks ·Connects Ring to Power PadCore Power ManagementVDD and VSS power rings are formed around the core and macro. In addition to this straps and trunks are created for macros as per the power requirement. Std cell rails are created to tap power from power straps to std cell power/ground pins.I/O Power ManagementPower rings are formed for I/O cells and trunks are constructed between core power ring and power pads.Power Planning Involves ·calculating number of power pins required ·Number of Rings, Stripes ·width of ring and stripes ·IR DropInputs of Power plan ·Netlist & SDC ·.lib , .lef & tech file ·Tlu+ file ·UPFIdeal Power distribution network has the following properties ·maintain a stable voltage with little noise ·Avoid wear out from EM and self heating ·Consume little chip area and wiring ·Easy to layoutPower Information ·The power information can obtain from the front end design. ·the synthesis tool reoprts static power information ·dynamic power can be calculated using value change dump (VCD) or switching activity interchange format (SAIF) file in conjunction with RTL description and test bench. ·Exhaustive test coverage is required for efficient calculation of peak power. this methodology is depicted in figure as shown below.PowerPlan : CalculationsUPF ContentsPower intent specifies ·Power Distribution Architecture: ·Power domains – Group of elements which share a common set of power supply requirements ·Supply rails – Power distribution (ports, nets, sets & switches) ·Shutdown control ·Power Strategy ·Power state tables – Legal combination of states of each power domain ·Operating voltages ·Usage of Special cells ·Isolation cells ·Level shifters ·Power switches ·Retention registersIsolation cells ·Powered off domains do not drive their outputs anymore and these outputs become floating nodes. This could be a problem when other active domains gets these floating nodes as input. It could result in crowbar current which affects the proper functioning of the powered up domain. ·Isolation cells (also called “clamps”) keep the turned off sub-block outputs at a predefined value. This is how the shut-down sub-block does not corrupt other active sub-block functionality. ·Isolation cells are powered by a constant supply and drive 0, 1 or latch the old value of the turned off domain. ·Isolation cells pass logic values during the normal mode of operation, but clamp it to some specified value when a control signal is asserted. ·Isolation cell clamps the output of powered down block to a specified value (‘0’, ‘1’, last) ·Gate type clamp cells (AND, OR) ·Transistor type clamp (pull-up, pull-down)Level Shifters ·Level shifters have the minimal functionality of a buffer. ·Necessary as most low-power designs have multi-voltage domains and/or employ dynamic voltage scaling. ·A level shifter swings a logic value in one voltage domain to the same logic value in another voltage domain. ·An ‘Up’ level shifter swings a logic value from a lower voltage domain to the same logic value in a higher voltage domain. ·A ‘Down’ level shifter swings a logic value from a higher voltage domain to the same logic value in a lower voltage domain.Internal circuit of level shifter.Retention Registers ·In order to reduce power consumption, memories are shut down where their power domain is switched off or when they are not in use. Registers are corrupted when power is switched off. Corruption is typically represented as ‘X’ (unknown). ·Some memories need to retain their values for fast wake-up. For these memories, only the memory array stays powered on during the shut-down while the peripheral interfaces are powered off. ·Retention registers keep their previous active value after being shut down. ·Retention registers save state information before a power domain is switched off and restore it when the power is turned back on. ·Retention registers comprise of two circuits. ·Standard register logic, supplied by primary power VDD ·Shadow latch retention circuitry, with alternate supply VDDB ·SAVE – transfers FF content into shadow latch during shutdown ·RESTORE – transfers state from shadow latch to FF when powered back onPower Switches ·Power switches are required to Gate the power supply of gated domain when not required. power switches are MT-CMOS (Multi Threshold) cells, which will have very high threshold voltage when device is OFF & very low threshold voltage when deviceis ON. ·power switches are inserted in power mesh & supply to all gated domain cells will be through power switches. hence a single/few switches are not enough. A strong network of power switchs connected in daisy chain fashion will be inserted in the design.There are 2 types of power switches header and footerHeader ·The header switch is implemented by PMOS transistors to control Vdd supply. ·PMOS transistor is less leaky than NMOS transistor of a same size. Header switches turn off VDD and keep VSS on. As the result, it allows a simple design of a pull-down transistor to isolate power-off cells and clamp output signals ·The disadvantage of the header switch is that PMOS has lower drive current than NMOS of a same size, though difference is reduced by strained silicon technology. As a result, a header switch implementation usually consumes more area than a footer switch implementation.Footer ·The footer switch is implemented by NMOS transistor to control VSS supply. ·The advantage of footer switch is the high drive and hence smaller area. ·However, NMOS is leakier than PMOS and a Designs become more sensitive to ground noiseFrequently Used Power Reduction TechniquesPower Gating: ·In a processor chip, certain areas of the chip will be idle and will be activated only for certain operations. But these areas are still provided with power for biasing. ·The power gating limits this unnecessary power being wasted by shuting down power for that area and resuming whenever needed. ·It is used for reducing LEAKAGE POWER or power consumption by switching off power supply to the non operational power domain of the chip during certain mode of operation. ·Header & footer switches, isolation cells, state retention flip flops are used for implementing power gating.Clock Gating: ·Clock gating limits the clock from being given to every register or flops in the processor. It disables the clock of an unused device. In clock gating the gated areas will still be provided with bias power. ·It is used for reducing DYNAMIC POWER by controlling switching activities on the clock path. ·Generally gate or latch or flip flop based block gating cells are used for implementing clock gating. ·50% of dynamic power is due to clock buffer. Since clock has highest toggle rate and often have higher drive strength to minimize clock delay. And the flops receive clocks dissipates some dynamic power even if input and output remains the same. Also clock buffer tree consumes power. One of the techniques to lower the dynamic power is clock gating. ·In load enabled flops, the output of the flops switches only when the enable is on. But clock switches continuously, increasing the dynamic power consumption. ·By converting load enable circuits to clock gating circuit dynamic power can be reduced. Normal clock gating circuit consists of an AND gate in the clock path with one input as enable. But when enable becomes one in between positive level of the clock a glitch is obtained. ·To remove the glitches due to AND gate, integrated clock gate is used. It has a negative triggered latch and an AND gate. ·Clock gating makes design more complex. Timing and CG timing closure becomes complex. Clock gating adds more gates to the design. Hence min bit width (minimum register bit width to be clock gated) should be wisely chosen, because the overall dynamic power consumption may increase.Voltage and Frequency Scaling: ·It changes the voltage and clock frequency to match the performance requirements for a given operation so as to minimize leakage. ·Different blocks are operated at variable supply voltages. The block voltage is dynamically adjusted based on performance requirements. ·Frequency of the block is dynamically adjusted. Works alongside with voltage scaling. Substrate Biasing: ·It changes the threshold voltage to reduce leakage current at the expense of slower switching times.Multiple Threshold Voltages: ·Uses different Vt in the circuit to reduce leakage but still satisfy timing constraints.Multiple Supply Voltages: ·Using Multi VDD reduces power consumption by powering down the not used voltage domain. Different blocks are operated at different supply voltages. Signals that cross voltage domain boundaries have to be level shifted.Memory Partitioning: ·The memory is split into several partitions. Not used ones can be powered down.Types of Power Dissipation:The power dissipation is classified in two categories: ·Static power dissipation ·Dynamic power dissipationStatic Power Dissipation:In this class, power will be dissipated irrespective of frequency and switching of the system. It is continuous and has become more dominant at lower node technologies. The structure and size of the device results in various leakage currents.Few reasons for static power dissipation are: ·Sub-threshold current ·Gate oxide leakage ·Diode reverse bias current ·Gate induced leakageIts hard to find the accurate amount of leakage currents but it mainly depends on supply voltage (VDD), threshold voltage (Vth), transistor size (W/L) and the doping concentration.Dynamic Power Dissipation:There are two reasons of dynamic power dissipation; Switching of the device and short circuit path from supply (VDD) to ground (VSS). This occurs during operation of the device. Signals change their logic state charging and discharging of output mode capacitor.Short-circuit Power Dissipation:Because of slower input transition, there will be certain duration of time “t”, for which both the devices (PMOS and NMOS) are turned ON. Now, there is a short circuit path from VDD to VSS. This short circuit power is given by:where, Vdd – Supply voltage, Isc – Short-circuit current and t – Short-circuit time. Short-circuit power is directly proportional to rise time and fall time.Switching Power Dissipation:Energy is drawn from the power supply to charge up the output mode capacitance. Charging up of the output cap causes transition from 0V to VDD. So, the power dissipated during charging and discharging of total load [output capacitance + net capacitance + input capacitance of driven cell(s)] is called Switching power dissipation. The switching power is given by:where, α – Switching activity factor, f – Operating frequency, VDD – Supply voltage & Cload – Load capacitance.Fundamental sources of power supply noise are IR Drop & Ldi/dt noise.IR Dropthe power supply in the chip is distributed uniformly through metal layers across the design and these metal layers have their finite amount of resistance. when we applied the volatge the current starts flowing through these metal layers and some voltage is dropped due to that resistance of a metal wire and current. this drop is called IR Drop. Because of IR drop, delay will increase and it violates the timing and this will increase noise and performance will be degraded.There are 2 types of IR Drop. ·Static IR Drop: This drop is independent of cell switching and this is calculated with the help of metal own resistance. ·Dynamic IR Drop: This drop is calculated with the help of the switching of cells. when a cell is switching at the active edge of the clock the cell requires large current or voltage to turn on but due to voltage drop suffficient amount of voltage is not reached to thr particular cell and cell may be goes into metastable state and effect the timing and performance.Methods to improve static IR Drop ·We can go for higher layers if available. ·Increase the width of the straps. ·Increase the number of wires. ·Check if any via is missing then add more via.Methods to improve Dynamic IR Drop ·Use De-Cap Cells. ·Increase the number of straps.Tools Used for IR Drop Analysis ·Redhawk from Apache ·Volatage storm from cadenceElectromigrationWhen a high density of current is flowing through metal layers, the atoms (electron) in the metal layers are displaced from their origional position causing open and shorts in the metal layers. Heating also accelerates EM because higher temperature cause a high number of metal ions to diffuseIn higher technology nodes we saw the EM on power and clock metal layers but now in lower nodes the signal metal layers are also needed to be analyzes due to an increased amount of current density.clock nets are more prone to EM because they have high switching activity because of this only we are avoiding to use high drive strength clock buffers to build the clock tree.Methods to solve EMIncrease the width of wireBuffer insertionDownsize the driverSwitch the net to higher metal layersAdding more vias来自微信 -

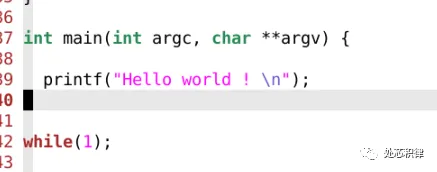

SOC验证C代码中如何打印字符串? 嵌入式微处理器2023年04月27日13:00四川学过C语言都知道,在程序中添加打印信息有助于我们追踪程序执行的情况。特别是debug的时候,打印一些log信息对快速定位到问题非常有帮助。怎么在SOC验证的C代码中打印字符串呢?用printf ?下面,我们来试一下:执行结果:没有出现 Hello world。这种结果是符合预期的。C code 通过GCC编译生成bin文件然后送到CPU中按指令进行执行。我们看下这段代码编译出来的指令是什么?这里 printf 编译出来是jump到一个puts的函数里面。puts函数又是什么呢?puts 又跳到 _puts_r ,依次下去,由printf 编译出了一系列的指令代码。由于CPU最终综合成版图,因此在CPU的RTL代码中不会存在读到某条指令打印一个字符串的功能。所以单纯的调用printf 并不会在log中打印字符串信息。如何实现打印?两个思路,第一个思路,在SOC的TB里面增加一个CPU bus的monitor,我们在monitor中实现一个功能,当看到特定地址,特定数据的时候,开始收集要打印的字符串,当看到特定地址,另外一个特定数据的时候,结束字符串的收集,并将收集到字符串打印。以下是我们在一个project中看到特殊数据 24’hdddd_11xx 开始收集字符串。以下是我们在一个project中看到特殊数据 24’hdddd_eeee 时打印字符串。这样,我们可以在c里面实现一个打印字符串的函数。通过上面这种手段,我们巧妙的将C语言的打印和 verilog的 $display 打印连接起来。我们来看看效果Hello World 打印出来了。我们再看看 puts编译后的代码是什么?这次 puts并没有跳转到 _puts_r ,而是向特定地址发送特定数据表示开始,然后传输字符串,并以特定数据结束。当我们的monitor检查到这些特殊的数据时就会打印出log信息。上面打印的方式可以解决在SOC验证环境中打印 字符串的问题,但是在芯片流片回来之后,在C中调用上述函数还能打印吗?显然是不可以的,因为这个时候外部的monitor都没有了,更别说不能综合的display函数等。下面介绍一种更加普遍的使用方法。我们在嵌入式硬件开发的过程中经常用到串口调试工具。通过简单的几根线与电脑连接,然后用串口调试助手就能将SOC和电脑调试界面连接起来。因此,在我们SOC验证环境中集成UART的slave device,在UART device收到数据后,打印出字符串信息是一个很好的选择。为此,我们通过向uart device写字符串的形式,然后在UART device中实现打印功能。我们来测试下用上面这种方式打印的效果,prints 是我们向uart 发送字符串的函数。下面是执行效果:同样实现了打印,而且这种打印方式在后续芯片流片回来之后可以通过串口调试 查看打印的信息。看到这里,大家明白怎么在SOC中实现字符串打印了吧~

SOC验证C代码中如何打印字符串? 嵌入式微处理器2023年04月27日13:00四川学过C语言都知道,在程序中添加打印信息有助于我们追踪程序执行的情况。特别是debug的时候,打印一些log信息对快速定位到问题非常有帮助。怎么在SOC验证的C代码中打印字符串呢?用printf ?下面,我们来试一下:执行结果:没有出现 Hello world。这种结果是符合预期的。C code 通过GCC编译生成bin文件然后送到CPU中按指令进行执行。我们看下这段代码编译出来的指令是什么?这里 printf 编译出来是jump到一个puts的函数里面。puts函数又是什么呢?puts 又跳到 _puts_r ,依次下去,由printf 编译出了一系列的指令代码。由于CPU最终综合成版图,因此在CPU的RTL代码中不会存在读到某条指令打印一个字符串的功能。所以单纯的调用printf 并不会在log中打印字符串信息。如何实现打印?两个思路,第一个思路,在SOC的TB里面增加一个CPU bus的monitor,我们在monitor中实现一个功能,当看到特定地址,特定数据的时候,开始收集要打印的字符串,当看到特定地址,另外一个特定数据的时候,结束字符串的收集,并将收集到字符串打印。以下是我们在一个project中看到特殊数据 24’hdddd_11xx 开始收集字符串。以下是我们在一个project中看到特殊数据 24’hdddd_eeee 时打印字符串。这样,我们可以在c里面实现一个打印字符串的函数。通过上面这种手段,我们巧妙的将C语言的打印和 verilog的 $display 打印连接起来。我们来看看效果Hello World 打印出来了。我们再看看 puts编译后的代码是什么?这次 puts并没有跳转到 _puts_r ,而是向特定地址发送特定数据表示开始,然后传输字符串,并以特定数据结束。当我们的monitor检查到这些特殊的数据时就会打印出log信息。上面打印的方式可以解决在SOC验证环境中打印 字符串的问题,但是在芯片流片回来之后,在C中调用上述函数还能打印吗?显然是不可以的,因为这个时候外部的monitor都没有了,更别说不能综合的display函数等。下面介绍一种更加普遍的使用方法。我们在嵌入式硬件开发的过程中经常用到串口调试工具。通过简单的几根线与电脑连接,然后用串口调试助手就能将SOC和电脑调试界面连接起来。因此,在我们SOC验证环境中集成UART的slave device,在UART device收到数据后,打印出字符串信息是一个很好的选择。为此,我们通过向uart device写字符串的形式,然后在UART device中实现打印功能。我们来测试下用上面这种方式打印的效果,prints 是我们向uart 发送字符串的函数。下面是执行效果:同样实现了打印,而且这种打印方式在后续芯片流片回来之后可以通过串口调试 查看打印的信息。看到这里,大家明白怎么在SOC中实现字符串打印了吧~