搜索到

344

篇与

的结果

-

ASIC设计学习总结(包括:工具及书籍文档推荐 、软件环境搭建、RTL设计、验证、工艺库说明、形式验证、综合等共12部分) 原创tfpwl——lj EET0P2019年02月07日09:57之前介绍过了了芯片设计全流程介绍(芯片设计全流程详解 包括:正向流程和反向流程)。由于当时的经验十分有限,所以对于正向设计,特别是对于从RTL级代码开始的设计介绍得不是很清楚。经过这一段时间的学习,对于从RTL级代码开始的Asic芯片设计有了更多的认识,现在总结一下,一方面给自己整理思路,另一方面也希望抛砖引玉,让大家各抒己见,分享一下各自的设计经验,促进我们的共同进步。笔者原本打算详细的介绍学习中的收获,将各类知识点写成文章,但经过反复考量之后,发现这种详细照搬别人知识的做法其实没什么意思。与其原封不动的转述别人书中的内容,不如直接提供参阅的书目,这样就免得在转述别人的知识的时候误解作者想要表达的真正意义。所以本系列的文章,笔者将个人学习的经验加以整合,将经验知识点罗列出来,并附加所参阅的书籍。另外涉及到实践操作过程的章节,将会把具体使用的工具罗列出来,并附上一些参考性的代码和脚本。本系列文章主要分为十二个部分,分别为:(一)工具及书籍文档推荐(二)软件环境搭建(三)RTL设计(四)验证(五)工艺库说明(六)形式验证(七)综合(八)可测性设计(九)低功耗设计(十)静态时序分析(十一)数模混合仿真(十二)可测性设计介绍这么多,不是显得个人有多少经验,其实本人也只是菜鸟,关注这么多内容,主要是为了让自己的知识储备更全面一下,这样考虑设计问题的时候遗漏的东西会更少一些。在本系列文章中,每个章节的详略是不同的,主要是跟个人工作经验有关,有介绍得简单的地方,麻烦大家帮忙补充。每个部分的内容基本采用“理论+工具+示例”的行文结构,有些EDA工具笔者没有使用过的就暂不能提供实例了。(一)工具及书籍文档一、前言对于RTL级的Asic设计所涉及到的软件是非常之多的,笔者也并没有每一个都使用过。二、工具介绍RTL代码规则检查工具:nlint,spyglass。这两个软件主要是用于检查代码的语法和语义错误的,并且比其他的工具能检测出更多的问题,比如说命名规格,时序风险,功耗等。详细介绍请参考软件的使用教程,nlint有Windows版和linux版,软件的linux版本和使用教程可以在eetop上搜索到。RTL代码仿真工具:这类仿真工具有较多的组合,比如说:qustasim/modelsim,NC_verilog+Verdi,VCS+DVE,VCS+Verdi等等。目前笔者使用的组合是VCS+Verdi。这两个软件是业内主流的仿真软件,还可以结合UVM库进行仿真,当然这是验证方法学的内容。综合工具:Design Complier。最常用的综合工具,没有之一,该软件主要是将RTL代码“翻译+优化+映射”成与工艺库对应的门级网表。并且还包含功耗分析软件Power Complier和边界扫描寄存器插入软件 BSD Complier。可测性设计:DFT Complier + TetraMAX。软件在DC之后使用,DFT Complier 用于将设计的内部寄存器替换成扫描寄存器并组成一条或多条扫描链,TetraMAX是用于自动生成测试向量的。形式验证工具:Formality、Conforml(candence出品)。等价性验证工具,主要是在DFT Complier插入扫描链之后进行验证,另外,在版图综合时钟树,插入BUFFER之后,也需要用该工具进行等效性验证。静态时序分析工具: Prime Time。业界最常用的时序分析工具之一,该软件包括功耗分析PTPX工具,功耗分析必备。cadence也有对应的时序分析工具——Encounter Timing System。自动布局布线工具(APR):ICC,Enconter。其中Encounter是Cadence公司的。数模混合仿真: nanosim + VCS,nanosim的升级版为XA。这是一篇有关于synopsysEDA工具软件的介绍,希望对于EDA软件的用途不清楚的伙伴有帮助。http://bbs.eetop.cn/thread-151171-1-1.html三、书籍推荐《Verilog HDL 硬件描述语言》《设计与验证Verilog HDL》《企业用verilog代码风格规范》《verilog语言编码风格》《verilogHDL代码风格规范》《Verilog HDL高级数字设计》《Soc设计方法与实现》《高级ASIC芯片综合》《华为Verilog典型电路设计》《数字IC系统设计》《数字集成电路--电路、系统与设计》《专用集成电路设计实用教程》《集成电路静态时序分析与建模》《CMOS集成电路后端设计与实战》《makefile教程》《鸟哥的私房菜》《SystemVerilog与功能验证》《UVM实战》《通信IC设计(上下册)》《数字图像处理与图像通信》《数字信号处理的FPGA实现中文版》各类Synopsy userguide,EETOP有16年版的。三、工艺库说明使用DC,PT,FM,ICC或者ENCOUNTER软件需要工艺库文件,主要包括数字逻辑单元文件,符号库,综合库,寄生电容参数库,版图文件LEF,milkway库等等。有关工艺库各文件夹的作用,笔者将会在将“工艺库说明”的章节进行详细介绍,如果有遗漏还请大家包涵。(二)环境搭建一、前言先介绍一下个人的使用环境。由于网络上已经存在很多安装教程,笔者就不再废话,直接给出他们的连接,并附带其他需要注意的关键点,如果有安装问题,请追问。Synopsys软件安装包下载地址在笔者前一篇文章“工具及书籍文档”,都是来自EETOP的大牛们提供的。在安装的过程中需要具备一些Linux系统的使用经验,不然会很难理解这些步骤是做什么的。个人的环境如下:1、vmware 12;2、RHEL6.5系统;3、synopsys软件,Lib Complier,VCS,Verdi,Desgin Complier,PrimeTime,Formality,ICC。一共7个软件,几乎都是15年版本的。二、步骤环境搭建需要准备以下三件事:1,vmware12虚拟机安装;安装教程如下。https://jingyan.baidu.com/article/215817f78879c21edb142379.html2, RHEL6.5操作系统安装,当然也可以使用CentOs6.5,安装教程如下。http://www.linuxidc.com/Linux/2016-05/131701.htm ——》RHEL6.5https://www.kafan.cn/edu/488101.html ——》Centos6.5a、安装vmware tools。在虚拟机中把系统安装好了之后,需要安装vmware tools,安装教程如下,http://www.linuxidc.com/Linux/2015-08/122031.htm ,安装该软件之后才可以启用共享文件夹以利于RHEL6.5与windows系统进行文件交换。b、更新YUM源,RHEL和Centos都需要更新YUM源,操作步骤一致,YUM是一个链接到软件库的一个软件,随后安装软件需要用到。https://jingyan.baidu.com/article/b24f6c8239c6aa86bee5da60.html注意:该教程某些步骤可能会失效,需要结合自己具体的情况使用。安装好YUM之后,可以使用yum install gvim命令测试一下。c、安装GCC,G++,这两个软件在VCS+Verdi仿真时会调用到。命令:yum install gcc命令:yum install gcc-c++3、 Synopsys软件安装Synopsys软件安装教程,链接如下:https://wenku.baidu.com/view/c02c271d9b6648d7c0c74670.htmlhttp://bbs.eetop.cn/thread-553702-1-1.html高版本和低版本的Synopsy软件安装步骤一致,区别在于license的问题。用EETOP上的最新license即可使用15版的软件。在使用RHEL操作系统需要懂一些SHELL脚本,makefile脚本,这样便于提高操作效率,后文会提到。注意:此外还需要修改四个文件的hostname,使得这四处的hostname保持一致。a、synopsys.dat中的第一行hostname;b、synopsys.bashrc中的export SNPSLMD_LICENSE_FILE=27000@localhost行,“@”符号后的hostname;c、/etc/sysconfig/network配置文件中hostname;d、/etc/hosts配置文件中的127.0.0.1这一行的 ,第三个参数hostname;这四个hostname一定要一致,才能正确启动DC,PT,FM,ICC,VCS,VERDI软件。在启动DC,PT,FM,ICC,VCS,VERDI软件之前需要先启动Synopsys的license管理器。有关软件的使用教程可以参考官方的userguide。或者EETOP上,小伙伴们的教程。(三)工艺库说明(略,请点击阅读原文查看)(四)RTL设计数字电路设计RTL设计所需要的理论知识庞杂而繁多,本文所介绍的内容均由个人参阅了许多书籍之后加以整合的,很多内容本人也不是很熟,只是罗列出来作为参考学习的资料。主要有三个部分的内容,第一部分主要是数字电路设计的基础,这是在大学时期应该予以掌握的内容,第二部分是进阶的学习内容附带一个专业方向——MCU,第三部分是有关于各类算法处理的专业知识,需要更多的复合型知识,例如通信方向需要有较好的数学功底—傅立叶变换。由于这部分内容实在太多,个人没有能力也没有必要将每一部分的内容都详细的罗列出来,所以这里只是整理出一些需要把握的关键点。至于具体的内容,还请大家按照个人需求,参阅推荐的各类书籍。一、基础组合逻辑与时序逻辑:布尔代数,卡诺图,基本与非门,锁存器,触发器,冲突与冒险。——《Verilog HDL高级数字设计》Verilog语言基础:数值类型,表达式与运算符,assign语句,always语句,if-else语句,case语句,阻塞与非阻塞。——《Verilog HDL 硬件描述语言》状态机:一段式、二段式、三段式状态机的区别;独热码、二进制码、格雷码的区别及应用场合。——《Verilog HDL高级数字设计》同步电路和异步电路:两者的本质,异步电路跨时钟域,亚稳态。——IC_learner博客复位与时钟:同步复位、异步复位、异步复位同步释放的区别,时钟分频——二分频、三分频、任意整数分频,门控时钟,时钟切换。——《深入浅出玩转FPGA》,百度文档数据通路与控制通路:本质上任何数字电路都可以划分为简单的两种类型——控制通路与数据通路,控制通路的核心是状态机,数据通路是各类算术处理算法、并行总线等等。——《Verilog HDL高级数字设计》Testbench验证:无论什么电路,最终都需要验证其功能的正确性。Testbench的结构主要由a,复位和时钟,b,激励产生电路,c,系统监视器,d,结果比较电路,e,波形产生函数,f,待验证的MODULE等主要模块组成,其中,b是最重要的模块,一切验证都是从激励信号开始的。——《verilogHDL代码风格规范》。初学者推荐使用windows版qustasim 或者modelsim 仿真工具,简单又方便,以后可学习使用VCS+Verdi(比较折腾人)。二、进阶代码风格:良好的代码风格很有必要,参考一下企业用的代码风格,有助于个人养成良好的编码习惯。——《企业用verilog代码风格规范》《verilog语言编码风格》基本常用电路:具备以上庞杂的理论基础之后,需要积累一些常用的基础电路。——《华为Verilog典型电路设计》接口电路,I2C,UART,SPI:接口电路是中小规模芯片常用的对外接口电路,无论是与上位机(PC)通信还是控制其它芯片。I2C从机常用于EEPROM芯片中,主机可以直接使用单片机模拟,ARM单片机直接集成了I2C主机,I2C的IP代码网络上有现成的;UART是全双工电路,宏晶单片机通过UART进行烧录,SPI电路最常用于SD卡上。——《Verilog HDL高级数字设计》《通信IC设计(上下册)》有简单的UART和SPI的代码。RISC,8051 MCU ——IP:通过下载EETOP上相关的IP及文档来学习。 三、专业数值的表示方法:浮点数,定点数的表示办法——《Verilog HDL高级数字设计》《通信IC设计(上下册)》算术处理算法:浮点数的加法、乘法电路设计。——《Verilog HDL高级数字设计》通信算法:FIR滤波器,IIR滤波器,傅立叶变换,冗余编码等等各种通信方向必须掌握的。——《通信IC设计(上下册)》《数字信号处理的FPGA实现》图像处理算法:静态图像,动态图像去噪。——《数字图像处理与图像通信》SOC:SOC类芯片的组成结构,AMBA总线,IP复用,SV验证。——《Soc设计方法与实现》四、工具:文档代码编辑器:GVIM,Notpad++RTL设计规则检查:Nlin,spyglass(五)验证(1)一、前言借助于前文RTL设计中提到的UART代码,本章节将在后面给出对应的testbench以及说明如何在questa/modelsim、VCS+DVE、VCS+Verdi工具中使用。推荐书籍:《vcs User Guide 2016》二、TestbenchTestbench的结构,正如上文提到的,主要由a,复位和时钟,b,激励产生电路,c,系统监视器,d,结果比较电路,e,波形产生函数,f,待验证的MODULE,g,控制仿真时间这几个部分组成。本章节提供的testbench只包含a,b,e,f,g部分,至于c,d更高级的内容,暂时无法涉及,questa/modelsim将不会使用到e部分的代码,使用questa/modelsim仿真时要屏蔽掉全部e段的内容。同样,在使用VCS+DVE进行仿真时要屏蔽VCS+VERDI的e段内容三、工具使用3.1modelsim仿真对于modelsim仿真, 仿真文件包含:1,verilog源文件(前文已全部提供);2,testbench文件(后面会提供)modelsim使用教程:https://wenku.baidu.com/view/db638e25b9d528ea81c779cc.html有关在modelsim软件中如何使用本示例请参考以上教程。仿真结果图:3.2 VCS+DVE和VCS+VERDI仿真对于VCS+DVE和VCS+VERDI, 仿真文件包含:1,verilog源文件(前文已全部提供);2,testbench文件(后面会提供),3,包含verilog、testbench文件路径的uart.f文件(必要时需自行修改),4,makefile仿真启动文件。在终端中运行make命令即可运行仿真,一定要注意文件路径问题。makefile教程:http://blog.csdn.net/liang13664759/article/details/1771246VCS+DVE 使用教程,https://wenku.baidu.com/view/48912cf558fb770bf68a55b4.htmlDVE是VCS软件自带的波形查看器。本章实例对应的VCS+DVE makefile启动脚本:all:VCS DVE VCS: vcs -f uart.f -full64 -debug_all -R DVE: dve -vpd wave.vpd -mode64 将以上内容复制到文本文件中,并将该文本文件改名为makeflile。uart.f内容:/home/Lance/synopsys/UART/testbench.v //必须放在文件中的第一行。/home/Lance/synopsys/UART/UART_XMTR.v/home/Lance/synopsys/UART/Control_Unit.v /home/Lance/synopsys/UART/Datapath_Unit.v/home/Lance/synopsys/UART/UART_RCVR.v/home/Lance/synopsys/UART/Control_Unit2.v/home/Lance/synopsys/UART/Datapath_Unit2.v DVE波形查看器启动命令:dve -vpd wave.vpd -mode64此外,在运行makefile启动脚本之前,还需要在testbench中添加如下代码:initialbegin $vcdplusfile("wave.vpd");//保存的波形文件名字 $vcdpluson(1,tb);//tb对应testbench文件的内的module名字 end该段代码为e,波形产生函数,主要是生成DVE波形查看器使用的VPD格式的波形文件。仿真结果图:VCS+Verdi,Verdi是debussy的升级版,是一个独立的软件,这对软件组合使用方式与VCS+DVE差不多。VCS+Verdi makefile启动脚本:all:VCS VERDI VCS:vcs +v2k -sverilog -debug_all -P /usr/synopsys/Verdi/K-2015.09/share/PLI/VCS/LINUX64/novas.tab /usr/synopsys/Verdi/K-2015.09/share/PLI/VCS/LINUX64/pli.a +vcs+lic+wait \ -f uart.f -y ./ +libext+.v -full64 -RVERDI: verdi -f uart.f -ssf wave.fsdb & 将以上内容复制到文本文件中,并将该文本文件改名为makeflile。注意:-P /usr/synopsys/Verdi/K-2015.09/share/PLI/VCS/LINUX64/novas.tab /usr/synopsys/Verdi/K-2015.09/share/PLI/VCS/LINUX64/pli.a主要是调用Verdi的接口函数以生成fsdb波形。 Verdi波形查看器启动命令:verdi -f uart.f -ssf wave.fsdb &此外,在运行makefile启动命令前,还需要在testbench中添加如下代码:initialbegin $fsdbDumpfile("wave.fsdb"); $fsdbDumpvars(0,tb); end 以生成Verdi波形查看器使用的FSDB格式的波形文件。注意: 启动脚本相关问题,需要学习makefile有关内容,有关VCS和Verdi的详细使用教程,还请参考其它资料。 (七) 综合(八)形式验证(九)数模混合仿真(十)静态时序分析(十一)低功耗设计(十二)可测性设计(由于篇幅关系,以上章节请点击阅读原文前往作者博客查看)推荐阅读:关注EETOP公众号,后台输入 芯片,查看如下文章ASIC前后端设计经典的细节讲解IC大牛10多年的设计分享:数字典型电路知识结构地图及代码实现关于华为海思,这篇文章值得一看俄国没有高端芯片,为什么却能造出一流武器?别拦我,我要做芯片!芯片春秋·ARM传中国芯酸往事印度芯酸往事国防军工芯片行业深度报告一位美国芯片公司华人高管对中国芯片行业的思考学习、积累、交流-IC设计高手的成长之路女生学微电子是一种什么体验?MIPS架构开放了,10天设计一款完全免费的MIPS处理器(附源码)性能之殇:从冯·诺依曼瓶颈谈起AI芯片设计与开发概览AI 芯片和传统芯片有何区别?一个资深工程师老王关于AI芯片的技术感悟隔隔壁老王:AI芯片与她怎么选?终于有人把云计算、大数据和人工智能讲明白了!尺寸减半、功率翻番!——氮化镓技术的现在和未来逻辑综合 Design Compiler 资料大全集成电路制造技术简史版图中Metal专题——线宽选择麒麟980内核照片:NPU在哪呢?有哪些只有IC工程师才能get到的梗?为什么7nm工艺制程这么难?从7nm看芯片行业的“贫富差距”什么是台积电的SoIC? RISC-V打入主流市场的诸多问题RISC-V架构有何优势?关于RISC-V 终于有人讲明白了!ASIC低功耗设计实例分析及书籍推荐ASIC设计学习总结之可测性设计及书籍推荐ASIC设计学习总结之静态时序分析概要及书籍推荐ASIC设计学习总结之工具及书籍文档小芯片大价值 | ASIC工程师如此值钱到底为什么?芯片面积估计方法简介自主研发通信芯片有多难?通信行业老兵告诉你,没那么简单!RISC-V精简到何种程度?能省的都省了!多核CPU设计及RISC-V相关资料时序设计与约束资料汇总模拟版图讲义GDSII转DEF的flow简介机器学习将越来越依赖FPGA和SoCVerilog基本功之:流水线设计Pipeline Design先进封装发展趋势分析PPT先进封装发展现状分析PPT可测试性设计与ATPG麒麟980是如何诞生的?敢于失败,勇于尝试!(附:华为早期型号处理器研发过程)IC模拟版图设计讲义 Verilog CPU设计实例。。。。(共260篇)

ASIC设计学习总结(包括:工具及书籍文档推荐 、软件环境搭建、RTL设计、验证、工艺库说明、形式验证、综合等共12部分) 原创tfpwl——lj EET0P2019年02月07日09:57之前介绍过了了芯片设计全流程介绍(芯片设计全流程详解 包括:正向流程和反向流程)。由于当时的经验十分有限,所以对于正向设计,特别是对于从RTL级代码开始的设计介绍得不是很清楚。经过这一段时间的学习,对于从RTL级代码开始的Asic芯片设计有了更多的认识,现在总结一下,一方面给自己整理思路,另一方面也希望抛砖引玉,让大家各抒己见,分享一下各自的设计经验,促进我们的共同进步。笔者原本打算详细的介绍学习中的收获,将各类知识点写成文章,但经过反复考量之后,发现这种详细照搬别人知识的做法其实没什么意思。与其原封不动的转述别人书中的内容,不如直接提供参阅的书目,这样就免得在转述别人的知识的时候误解作者想要表达的真正意义。所以本系列的文章,笔者将个人学习的经验加以整合,将经验知识点罗列出来,并附加所参阅的书籍。另外涉及到实践操作过程的章节,将会把具体使用的工具罗列出来,并附上一些参考性的代码和脚本。本系列文章主要分为十二个部分,分别为:(一)工具及书籍文档推荐(二)软件环境搭建(三)RTL设计(四)验证(五)工艺库说明(六)形式验证(七)综合(八)可测性设计(九)低功耗设计(十)静态时序分析(十一)数模混合仿真(十二)可测性设计介绍这么多,不是显得个人有多少经验,其实本人也只是菜鸟,关注这么多内容,主要是为了让自己的知识储备更全面一下,这样考虑设计问题的时候遗漏的东西会更少一些。在本系列文章中,每个章节的详略是不同的,主要是跟个人工作经验有关,有介绍得简单的地方,麻烦大家帮忙补充。每个部分的内容基本采用“理论+工具+示例”的行文结构,有些EDA工具笔者没有使用过的就暂不能提供实例了。(一)工具及书籍文档一、前言对于RTL级的Asic设计所涉及到的软件是非常之多的,笔者也并没有每一个都使用过。二、工具介绍RTL代码规则检查工具:nlint,spyglass。这两个软件主要是用于检查代码的语法和语义错误的,并且比其他的工具能检测出更多的问题,比如说命名规格,时序风险,功耗等。详细介绍请参考软件的使用教程,nlint有Windows版和linux版,软件的linux版本和使用教程可以在eetop上搜索到。RTL代码仿真工具:这类仿真工具有较多的组合,比如说:qustasim/modelsim,NC_verilog+Verdi,VCS+DVE,VCS+Verdi等等。目前笔者使用的组合是VCS+Verdi。这两个软件是业内主流的仿真软件,还可以结合UVM库进行仿真,当然这是验证方法学的内容。综合工具:Design Complier。最常用的综合工具,没有之一,该软件主要是将RTL代码“翻译+优化+映射”成与工艺库对应的门级网表。并且还包含功耗分析软件Power Complier和边界扫描寄存器插入软件 BSD Complier。可测性设计:DFT Complier + TetraMAX。软件在DC之后使用,DFT Complier 用于将设计的内部寄存器替换成扫描寄存器并组成一条或多条扫描链,TetraMAX是用于自动生成测试向量的。形式验证工具:Formality、Conforml(candence出品)。等价性验证工具,主要是在DFT Complier插入扫描链之后进行验证,另外,在版图综合时钟树,插入BUFFER之后,也需要用该工具进行等效性验证。静态时序分析工具: Prime Time。业界最常用的时序分析工具之一,该软件包括功耗分析PTPX工具,功耗分析必备。cadence也有对应的时序分析工具——Encounter Timing System。自动布局布线工具(APR):ICC,Enconter。其中Encounter是Cadence公司的。数模混合仿真: nanosim + VCS,nanosim的升级版为XA。这是一篇有关于synopsysEDA工具软件的介绍,希望对于EDA软件的用途不清楚的伙伴有帮助。http://bbs.eetop.cn/thread-151171-1-1.html三、书籍推荐《Verilog HDL 硬件描述语言》《设计与验证Verilog HDL》《企业用verilog代码风格规范》《verilog语言编码风格》《verilogHDL代码风格规范》《Verilog HDL高级数字设计》《Soc设计方法与实现》《高级ASIC芯片综合》《华为Verilog典型电路设计》《数字IC系统设计》《数字集成电路--电路、系统与设计》《专用集成电路设计实用教程》《集成电路静态时序分析与建模》《CMOS集成电路后端设计与实战》《makefile教程》《鸟哥的私房菜》《SystemVerilog与功能验证》《UVM实战》《通信IC设计(上下册)》《数字图像处理与图像通信》《数字信号处理的FPGA实现中文版》各类Synopsy userguide,EETOP有16年版的。三、工艺库说明使用DC,PT,FM,ICC或者ENCOUNTER软件需要工艺库文件,主要包括数字逻辑单元文件,符号库,综合库,寄生电容参数库,版图文件LEF,milkway库等等。有关工艺库各文件夹的作用,笔者将会在将“工艺库说明”的章节进行详细介绍,如果有遗漏还请大家包涵。(二)环境搭建一、前言先介绍一下个人的使用环境。由于网络上已经存在很多安装教程,笔者就不再废话,直接给出他们的连接,并附带其他需要注意的关键点,如果有安装问题,请追问。Synopsys软件安装包下载地址在笔者前一篇文章“工具及书籍文档”,都是来自EETOP的大牛们提供的。在安装的过程中需要具备一些Linux系统的使用经验,不然会很难理解这些步骤是做什么的。个人的环境如下:1、vmware 12;2、RHEL6.5系统;3、synopsys软件,Lib Complier,VCS,Verdi,Desgin Complier,PrimeTime,Formality,ICC。一共7个软件,几乎都是15年版本的。二、步骤环境搭建需要准备以下三件事:1,vmware12虚拟机安装;安装教程如下。https://jingyan.baidu.com/article/215817f78879c21edb142379.html2, RHEL6.5操作系统安装,当然也可以使用CentOs6.5,安装教程如下。http://www.linuxidc.com/Linux/2016-05/131701.htm ——》RHEL6.5https://www.kafan.cn/edu/488101.html ——》Centos6.5a、安装vmware tools。在虚拟机中把系统安装好了之后,需要安装vmware tools,安装教程如下,http://www.linuxidc.com/Linux/2015-08/122031.htm ,安装该软件之后才可以启用共享文件夹以利于RHEL6.5与windows系统进行文件交换。b、更新YUM源,RHEL和Centos都需要更新YUM源,操作步骤一致,YUM是一个链接到软件库的一个软件,随后安装软件需要用到。https://jingyan.baidu.com/article/b24f6c8239c6aa86bee5da60.html注意:该教程某些步骤可能会失效,需要结合自己具体的情况使用。安装好YUM之后,可以使用yum install gvim命令测试一下。c、安装GCC,G++,这两个软件在VCS+Verdi仿真时会调用到。命令:yum install gcc命令:yum install gcc-c++3、 Synopsys软件安装Synopsys软件安装教程,链接如下:https://wenku.baidu.com/view/c02c271d9b6648d7c0c74670.htmlhttp://bbs.eetop.cn/thread-553702-1-1.html高版本和低版本的Synopsy软件安装步骤一致,区别在于license的问题。用EETOP上的最新license即可使用15版的软件。在使用RHEL操作系统需要懂一些SHELL脚本,makefile脚本,这样便于提高操作效率,后文会提到。注意:此外还需要修改四个文件的hostname,使得这四处的hostname保持一致。a、synopsys.dat中的第一行hostname;b、synopsys.bashrc中的export SNPSLMD_LICENSE_FILE=27000@localhost行,“@”符号后的hostname;c、/etc/sysconfig/network配置文件中hostname;d、/etc/hosts配置文件中的127.0.0.1这一行的 ,第三个参数hostname;这四个hostname一定要一致,才能正确启动DC,PT,FM,ICC,VCS,VERDI软件。在启动DC,PT,FM,ICC,VCS,VERDI软件之前需要先启动Synopsys的license管理器。有关软件的使用教程可以参考官方的userguide。或者EETOP上,小伙伴们的教程。(三)工艺库说明(略,请点击阅读原文查看)(四)RTL设计数字电路设计RTL设计所需要的理论知识庞杂而繁多,本文所介绍的内容均由个人参阅了许多书籍之后加以整合的,很多内容本人也不是很熟,只是罗列出来作为参考学习的资料。主要有三个部分的内容,第一部分主要是数字电路设计的基础,这是在大学时期应该予以掌握的内容,第二部分是进阶的学习内容附带一个专业方向——MCU,第三部分是有关于各类算法处理的专业知识,需要更多的复合型知识,例如通信方向需要有较好的数学功底—傅立叶变换。由于这部分内容实在太多,个人没有能力也没有必要将每一部分的内容都详细的罗列出来,所以这里只是整理出一些需要把握的关键点。至于具体的内容,还请大家按照个人需求,参阅推荐的各类书籍。一、基础组合逻辑与时序逻辑:布尔代数,卡诺图,基本与非门,锁存器,触发器,冲突与冒险。——《Verilog HDL高级数字设计》Verilog语言基础:数值类型,表达式与运算符,assign语句,always语句,if-else语句,case语句,阻塞与非阻塞。——《Verilog HDL 硬件描述语言》状态机:一段式、二段式、三段式状态机的区别;独热码、二进制码、格雷码的区别及应用场合。——《Verilog HDL高级数字设计》同步电路和异步电路:两者的本质,异步电路跨时钟域,亚稳态。——IC_learner博客复位与时钟:同步复位、异步复位、异步复位同步释放的区别,时钟分频——二分频、三分频、任意整数分频,门控时钟,时钟切换。——《深入浅出玩转FPGA》,百度文档数据通路与控制通路:本质上任何数字电路都可以划分为简单的两种类型——控制通路与数据通路,控制通路的核心是状态机,数据通路是各类算术处理算法、并行总线等等。——《Verilog HDL高级数字设计》Testbench验证:无论什么电路,最终都需要验证其功能的正确性。Testbench的结构主要由a,复位和时钟,b,激励产生电路,c,系统监视器,d,结果比较电路,e,波形产生函数,f,待验证的MODULE等主要模块组成,其中,b是最重要的模块,一切验证都是从激励信号开始的。——《verilogHDL代码风格规范》。初学者推荐使用windows版qustasim 或者modelsim 仿真工具,简单又方便,以后可学习使用VCS+Verdi(比较折腾人)。二、进阶代码风格:良好的代码风格很有必要,参考一下企业用的代码风格,有助于个人养成良好的编码习惯。——《企业用verilog代码风格规范》《verilog语言编码风格》基本常用电路:具备以上庞杂的理论基础之后,需要积累一些常用的基础电路。——《华为Verilog典型电路设计》接口电路,I2C,UART,SPI:接口电路是中小规模芯片常用的对外接口电路,无论是与上位机(PC)通信还是控制其它芯片。I2C从机常用于EEPROM芯片中,主机可以直接使用单片机模拟,ARM单片机直接集成了I2C主机,I2C的IP代码网络上有现成的;UART是全双工电路,宏晶单片机通过UART进行烧录,SPI电路最常用于SD卡上。——《Verilog HDL高级数字设计》《通信IC设计(上下册)》有简单的UART和SPI的代码。RISC,8051 MCU ——IP:通过下载EETOP上相关的IP及文档来学习。 三、专业数值的表示方法:浮点数,定点数的表示办法——《Verilog HDL高级数字设计》《通信IC设计(上下册)》算术处理算法:浮点数的加法、乘法电路设计。——《Verilog HDL高级数字设计》通信算法:FIR滤波器,IIR滤波器,傅立叶变换,冗余编码等等各种通信方向必须掌握的。——《通信IC设计(上下册)》《数字信号处理的FPGA实现》图像处理算法:静态图像,动态图像去噪。——《数字图像处理与图像通信》SOC:SOC类芯片的组成结构,AMBA总线,IP复用,SV验证。——《Soc设计方法与实现》四、工具:文档代码编辑器:GVIM,Notpad++RTL设计规则检查:Nlin,spyglass(五)验证(1)一、前言借助于前文RTL设计中提到的UART代码,本章节将在后面给出对应的testbench以及说明如何在questa/modelsim、VCS+DVE、VCS+Verdi工具中使用。推荐书籍:《vcs User Guide 2016》二、TestbenchTestbench的结构,正如上文提到的,主要由a,复位和时钟,b,激励产生电路,c,系统监视器,d,结果比较电路,e,波形产生函数,f,待验证的MODULE,g,控制仿真时间这几个部分组成。本章节提供的testbench只包含a,b,e,f,g部分,至于c,d更高级的内容,暂时无法涉及,questa/modelsim将不会使用到e部分的代码,使用questa/modelsim仿真时要屏蔽掉全部e段的内容。同样,在使用VCS+DVE进行仿真时要屏蔽VCS+VERDI的e段内容三、工具使用3.1modelsim仿真对于modelsim仿真, 仿真文件包含:1,verilog源文件(前文已全部提供);2,testbench文件(后面会提供)modelsim使用教程:https://wenku.baidu.com/view/db638e25b9d528ea81c779cc.html有关在modelsim软件中如何使用本示例请参考以上教程。仿真结果图:3.2 VCS+DVE和VCS+VERDI仿真对于VCS+DVE和VCS+VERDI, 仿真文件包含:1,verilog源文件(前文已全部提供);2,testbench文件(后面会提供),3,包含verilog、testbench文件路径的uart.f文件(必要时需自行修改),4,makefile仿真启动文件。在终端中运行make命令即可运行仿真,一定要注意文件路径问题。makefile教程:http://blog.csdn.net/liang13664759/article/details/1771246VCS+DVE 使用教程,https://wenku.baidu.com/view/48912cf558fb770bf68a55b4.htmlDVE是VCS软件自带的波形查看器。本章实例对应的VCS+DVE makefile启动脚本:all:VCS DVE VCS: vcs -f uart.f -full64 -debug_all -R DVE: dve -vpd wave.vpd -mode64 将以上内容复制到文本文件中,并将该文本文件改名为makeflile。uart.f内容:/home/Lance/synopsys/UART/testbench.v //必须放在文件中的第一行。/home/Lance/synopsys/UART/UART_XMTR.v/home/Lance/synopsys/UART/Control_Unit.v /home/Lance/synopsys/UART/Datapath_Unit.v/home/Lance/synopsys/UART/UART_RCVR.v/home/Lance/synopsys/UART/Control_Unit2.v/home/Lance/synopsys/UART/Datapath_Unit2.v DVE波形查看器启动命令:dve -vpd wave.vpd -mode64此外,在运行makefile启动脚本之前,还需要在testbench中添加如下代码:initialbegin $vcdplusfile("wave.vpd");//保存的波形文件名字 $vcdpluson(1,tb);//tb对应testbench文件的内的module名字 end该段代码为e,波形产生函数,主要是生成DVE波形查看器使用的VPD格式的波形文件。仿真结果图:VCS+Verdi,Verdi是debussy的升级版,是一个独立的软件,这对软件组合使用方式与VCS+DVE差不多。VCS+Verdi makefile启动脚本:all:VCS VERDI VCS:vcs +v2k -sverilog -debug_all -P /usr/synopsys/Verdi/K-2015.09/share/PLI/VCS/LINUX64/novas.tab /usr/synopsys/Verdi/K-2015.09/share/PLI/VCS/LINUX64/pli.a +vcs+lic+wait \ -f uart.f -y ./ +libext+.v -full64 -RVERDI: verdi -f uart.f -ssf wave.fsdb & 将以上内容复制到文本文件中,并将该文本文件改名为makeflile。注意:-P /usr/synopsys/Verdi/K-2015.09/share/PLI/VCS/LINUX64/novas.tab /usr/synopsys/Verdi/K-2015.09/share/PLI/VCS/LINUX64/pli.a主要是调用Verdi的接口函数以生成fsdb波形。 Verdi波形查看器启动命令:verdi -f uart.f -ssf wave.fsdb &此外,在运行makefile启动命令前,还需要在testbench中添加如下代码:initialbegin $fsdbDumpfile("wave.fsdb"); $fsdbDumpvars(0,tb); end 以生成Verdi波形查看器使用的FSDB格式的波形文件。注意: 启动脚本相关问题,需要学习makefile有关内容,有关VCS和Verdi的详细使用教程,还请参考其它资料。 (七) 综合(八)形式验证(九)数模混合仿真(十)静态时序分析(十一)低功耗设计(十二)可测性设计(由于篇幅关系,以上章节请点击阅读原文前往作者博客查看)推荐阅读:关注EETOP公众号,后台输入 芯片,查看如下文章ASIC前后端设计经典的细节讲解IC大牛10多年的设计分享:数字典型电路知识结构地图及代码实现关于华为海思,这篇文章值得一看俄国没有高端芯片,为什么却能造出一流武器?别拦我,我要做芯片!芯片春秋·ARM传中国芯酸往事印度芯酸往事国防军工芯片行业深度报告一位美国芯片公司华人高管对中国芯片行业的思考学习、积累、交流-IC设计高手的成长之路女生学微电子是一种什么体验?MIPS架构开放了,10天设计一款完全免费的MIPS处理器(附源码)性能之殇:从冯·诺依曼瓶颈谈起AI芯片设计与开发概览AI 芯片和传统芯片有何区别?一个资深工程师老王关于AI芯片的技术感悟隔隔壁老王:AI芯片与她怎么选?终于有人把云计算、大数据和人工智能讲明白了!尺寸减半、功率翻番!——氮化镓技术的现在和未来逻辑综合 Design Compiler 资料大全集成电路制造技术简史版图中Metal专题——线宽选择麒麟980内核照片:NPU在哪呢?有哪些只有IC工程师才能get到的梗?为什么7nm工艺制程这么难?从7nm看芯片行业的“贫富差距”什么是台积电的SoIC? RISC-V打入主流市场的诸多问题RISC-V架构有何优势?关于RISC-V 终于有人讲明白了!ASIC低功耗设计实例分析及书籍推荐ASIC设计学习总结之可测性设计及书籍推荐ASIC设计学习总结之静态时序分析概要及书籍推荐ASIC设计学习总结之工具及书籍文档小芯片大价值 | ASIC工程师如此值钱到底为什么?芯片面积估计方法简介自主研发通信芯片有多难?通信行业老兵告诉你,没那么简单!RISC-V精简到何种程度?能省的都省了!多核CPU设计及RISC-V相关资料时序设计与约束资料汇总模拟版图讲义GDSII转DEF的flow简介机器学习将越来越依赖FPGA和SoCVerilog基本功之:流水线设计Pipeline Design先进封装发展趋势分析PPT先进封装发展现状分析PPT可测试性设计与ATPG麒麟980是如何诞生的?敢于失败,勇于尝试!(附:华为早期型号处理器研发过程)IC模拟版图设计讲义 Verilog CPU设计实例。。。。(共260篇) -

关于量子通信与量子计算,终于有人讲透了! EET0P2018年09月17日11:59来源:绿盟博客 作者:陈磊 原地址:http://blog.nsfocus.net/quantum-information-technology/本文首先介绍量子相关的基本概念、性质及基本原理;接着,从量子通信和量子计算两个部分阐述其原理与发展现状;然后,简单介绍了后量子密码学(也称抗量子密码体制)的发展情况;最后,对量子信息技术的发展进行总结与展望。文章目录1 引言2 量子信息简介2.1 量子概念2.2 量子基本特性2.3 量子信息2.4 量子信息学3 量子通信3.1 量子通信系统基本模型3.2 量子通信技术优势3.3 量子密钥分配基本原理3.4 量子隐形传态基本原理3.5 理论与试验研究进展3.6 产业化进展与面临的挑战4 量子计算4.1 典型量子算法4.2 量子机器学习与深度学习算法4.3 量子计算机4.4 量子编码5 后量子密码6 总结1 引言量子信息科学(Quantum Information)是以量子力学为基础,把量子系统“状态”所带有的物理信息,进行信息编码、计算和传输的全新信息技术。量子信息技术主要包括量子通信和量子计算,由于它们具有潜在的应用价值和重大的科学意义,正引起人们广泛的关注和研究。本文首先介绍量子相关的基本概念、性质及基本原理;接着,从量子通信和量子计算两个部分阐述其原理与发展现状;然后,简单介绍了后量子密码学(也称抗量子密码体制)的发展情况;最后,对量子信息技术的发展进行总结与展望。2 量子信息简介在本章中,首先介绍量子和量子信息基本概念及相关特性;然后介绍量子信息学领域的研究分支及其研究内容。2.1 量子概念量子(Quantum)属于一个微观的物理概念。如果一个物理量存在最小的不可分割的基本单位[1],那么称这个物理量是可量子化的,并把物理量的基本单位称为量子。现代物理中,将微观世界中所有的不可分割的微观粒子(光子、电子、原子等)或其状态等物理量统称为量子。量子这个概念最早由德国物理学家普朗克在1900年提出的,他假设黑体辐射中的辐射能量是不连续的,只能取能量基本单位的整数倍,这很好地解释了黑体辐射的实验现象。即假设对于一定频率的电磁辐射,物体只以“量子”的方式吸收和发射,每个“量子”的能量可以表示为:,为普朗克常数。量子假设的提出有力地冲击了牛顿力学为代表的经典物理学,促进物理学进入微观层面,奠定了现代物理学基础,进入了全新的领域。2.2 量子基本特性作为一种微观粒子,量子具有许多特别的基本特性,如量子力学三大基本原理:量子测不准也称为不确定性原理,即观察者不可能同时知道一个粒子的位置和它的速度,粒子位置的总是以一定的概率存在某一个不同的地方,而对未知状态系统的每一次测量都必将改变系统原来的状态。也就是说,测量后的微粒相比于测量之前,必然会产生变化。量子不可克隆量子不可克隆原理,即一个未知的量子态不能被完全地克隆。在量子力学中,不存在这样一个物理过程:实现对一个未知量子态的精确复制,使得每个复制态与初始量子态完全相同。量子不可区分量子不可区分原理,即不可能同时精确测量两个非正交量子态。事实上,由于非正交量子态具有不可区分性,无论采用任何测量方法,测量结果的都会有错误。除此之外,还包括以下基本特性:量子态叠加性(superposition)量子状态可以叠加,因此量子信息也是可以叠加的。这是量子计算中的可以实现并行性的重要基础,即可以同时输入和操作个量子比特的叠加态。量子态纠缠性(entanglement)两个及以上的量子在特定的(温度、磁场)环境下可以处于较稳定的量子纠缠状态,基于这种纠缠,某个粒子的作用将会瞬时地影响另一个粒子。爱因斯坦称其为: “幽灵般的超距作用”。量子态相干性(interference)量子力学中微观粒子间的相互叠加作用能产生类似经典力学中光的干涉现象。2.3 量子信息一个经典的二进制存储器只能存一个数:要么存 0,要么存 1。但一个二进制量子存储器却可以同时存储0和1这两个数。两个经典二进制存储器只能存储以下四个数的一个数: 00,01,10 或 11。倘若使用两个二进制量子存储器,则以上四个数可以同时被存储下来。按此规律,推广到N个二进制存储器的情况,理论上,N个量子存储器与N个经典存储器分别能够存储个数和1个数。由此可见,量子存储器的存储能力是呈指数增长的,它比经典存储器具有更强大的存储数据的能力,尤其是当 N很大时(如 N=250 ),量子存储器能够存储的数据量比宇宙中所有原子的数目还要多[1]。2.4 量子信息学量子信息学是量子力学与信息科学形成的一个交叉学科,该领域主要包括两个领域:量子通信和量子计算。其中量子通信主要研究的是量子介质的信息传递功能进行通信的一种技术,而量子计算则主要研究量子计算机和适合于量子计算机的量子算法。图 1 量子信息学的研究分支3 量子通信所谓量子通信,从概念角度来讲就是利用量子介质的信息传递功能进行通信的一种技术。它主要包括量子密钥分配、量子隐形传态等技术。量子密码 (Quantum Cryptography)是利用量子力学属性开发的密码系统。与传统的密码系统不同的是,它的安全性依赖于量子力学属性(不可测量和不可克隆等)而不是数学的复杂度理论。量子密钥分配是研究最为成熟的量子密码技术。在本章中,我们首先简单地介绍量子通信系统的基本模型以及优势,然后介绍量子密钥分配和量子隐形传态的基本原理。接着,概述量子通信的目前研究与发展现状。最后,总结量子通信目前存在的问题。3.1 量子通信系统基本模型量子通信体系架构包括量子态发生器、量子通道和量子测量装置以及经典信道等部分,其基本模型如图2所示。图 2 量子通信系统基本模型量子通信过程可以从发送端和接收端两个角度理解。在发送端,量子信源模块产生消息,消息通过量子编码模块转换成量子比特,量子比特通过量子调制模块得到以量子态为载体的量子信息,量子信息通过量子信道进行传输。除此以外,量子调制的模式信息(传统的信息)需要使用经典信道进行传输。在接收端,将接收到两部分信息:量子信道接收量子信息;经典信道接收额外的经典信息。这两部分信息通过解调和解码模块后,获得最终的消息。3.2 量子通信技术优势量子通信与传统通信技术相比,具有如下主要特点和优势:(1) 时效性高。量子通信的线路时延近乎为零,量子信道的信息效率相对于经典信道量子的信息效率高几十倍,传输速度快。(2) 抗干扰性能强。量子通信中的信息传输不通过传统信道(如传统移动通信为了使得通信不被干扰,需要约定好频率,而量子通信不需要考虑这些因素),与通信双方之间的传播媒介无关,不受空间环境的影响,具有完好的抗干扰性能。(3) 保密性能好。根据量子不可克隆定理,量子信息一经检测就会产生不可还原的改变,如果量子信息在传输中途被窃取,接收者必定能发现。(4) 隐蔽性能好。量子通信没有电磁辐射,第三方无法进行无线监听或探测。(5) 应用广泛。量子通信与传播媒介无关,传输不会被任何障碍阻隔,量子隐形传态通信还能穿越大气层。因此,量子通信应用广泛,既可在太空中通信,又可在海底通信,还可在光纤等介质中通信。3.3 量子密钥分配基本原理量子密钥分配 (Quantum Key Distribution, QKD)以量子态为信息载体,通过量子信道使通信收发双方共享密钥,是密码学与量子力学相结合的产物。QKD 技术在通信中并不传输密文,而是利用量子信道将密钥分配给通信双方,由于量子力学的测不准和量子不可克隆定理,攻击者无法获取正确的密钥。基于QKD 技术的保密通信系统结构如图3所示,其中上路负责密钥分配,下路负责传输加解密数据。在上路中,量子信道负责传输量子密钥,经典信道负责传输测量基[2]等额外需要的信息。下面,将以BB84[5]方案为例,具体地介绍两条信道起到的作用。图 3 基于QKD 的量子保密通信系统BB84 方案。1984 年,Brassard与Bennett联合提出了第一个实用型量子密钥分配系统—BB84 方案,系统架构如图4 所示。图 4 BB84协议示意图[20]该方案通过量子信道传送密钥,量子信道的信息载体是单个量子,通过量子的相位、极化方向或频率等物理量携带量子密钥信息。BB84 方案利用单个量子作为信息载体两组共扼基,每组基中的两个极化互相正交。由于理想状态的量子信道无法实现,BB84 方案还利用经典信道进行量子态测量方法的协商和码序列的验证。有趣的现象:接收端必须使用正确的测量基,才能正确地测出量子比特(光量子的偏振态);使用错误的测量基,测量结果将发生错误,同时光量子的偏振态发生改变,如图5所示。图 5测量基对测量结果的影响[20]有了以上基础后,理解BB84协议将变得相对容易,其主要步骤如下:量子信道部分(1) Alice发送随机的量子比特串给Bob。Alice随机选择四种偏振片,制备不同偏振状态的光量子,得到足够多的随机量子比特并将其发送给Bob。(2) Bob随机选择测量基测量量子比特。由于Bob并不知道光量子是由发送端那一种测量基编码的,所以他也只能随机选择测量基来进行测量。当选择正确的测量基时,测量的结果正确。当使用错误的测量结果时,测量结果错误。经典信道部分(3) Bob将使用的测量基发送给Alice。(4) Alice将接收的测量基与使用的测量基进行比较,并通过信息告诉Bob哪些位置的测量基是正确的。(5) Bob根据Alice的消息剔除错误的量子比特,并将选择少部分正确的测量结果告诉Alice。(6) Alice确认Bob测量结果的正确性。若错误,则说明存在量子信道可能存在窃听,停止通信或者返回第 (1) 步(由于实际的量子信道中也存在噪声,因此会根据一个错误率阈值判断是否窃听和停止通信)。若正确,剔除部分的量子比特,剩下的二进制串作为最终的密钥。并发送确认信息给Bob。(7) Bob收到确认信息。同样剔除部分的量子比特,剩下的二进制串作为最终的密钥。我们对BB84协议的安全性做一个简单的分析:如果Eve在量子信道中旁路窃听,由于量子不可克隆,因此Eve无法复制出一份相同的量子比特副本;如果他在量子信道中直接测量光量子,由于Eve不知正确的测量基,他也会随机选择,有50%的概率选择正确,50%的概率选择错误。若选择的测量基错误,有上述的有趣的现象可知,测量结果错误,同时光量子的偏振态发生改变。当协议的步骤由 (2) 执行到 (6) 时,Alice将发现到量子信道的窃听,那么她将终止这一过程。如果在经典信道进行窃听呢?实际上也是无效的。即使Eve知道了测量基信息(步骤 (3)),然而由于量子不可克隆,无法得到正确的量子比特串副本。由以上分析可知,BB84协议基于量子不可克隆等原理,实现安全的密钥分配过程。3.4 量子隐形传态基本原理量子隐形传态( Quantum Teleportation) 又称量子远程传态或量子离物传态,是利用量子纠缠的不确定特性,将某个量子的未知量子态通过EPR对(纠缠量子对)的一个量子传送到另一个地方(即EPR对中另一个量子),而原来的量子仍留在原处。如图所示6所示,Alice想和Bob通信,具体流程如下:(1) 制备两个有纠缠的EPR量子(粒子)对,然后将其分开,Alice和Bob各持一个,分别是粒子1和粒子2。(2) Alice粒子1和某一个未知量子态的粒子3进行联合测量,然后将测量结果通过经典信道传送给接Bob。此时,神奇的事情发生了:Bob持有的粒子2将随着Alice测量同时发生改变,由一量子态变成新的量子态。这是由于量子纠缠的作用,粒子2和粒子1之间如同有一根无形。(3) Bob根据接收的息和拥有粒子2做相应幺正变换(一种量子计算变换),根据这些信息,可以重构出粒子3的全貌。图 6 量子隐形传态原理图3.5 理论与试验研究进展1993年,学术界给出了一种利用量子技术传输信息的实际方案,4年后量子通信技术在奥地利科学家的实验室中正式完成了实验验证。经过十多年的发展,量子通信先后实现了信息传递从600m(2007年)到通信距离144km(2012年)的巨大跨越,标志量子通信从理论阶段走向实用化阶段。下面从量子密钥分配和量子隐形传态两个主要研究领域进行介绍。(1) 量子密钥分配国外:1993年,英国研究小组首先在光纤中,使用相位编码的方法实现了BB84方案,通信传输距离达10km;1995年,该小组将距离提升到30km。瑞士于1993年用偏振光子实现了BB84方案,光子波长1.3mm,传输距离1.1km,误码率0.54%;1995年,将距离提升到23km,误码率为3.4%;2002年,传输距离达到67km。2000年,美国实现自由空间量子密钥分配通信,传输距离达1.6km。2003年,欧洲研究小组实现自由空间中23km的通信。2008年10月,欧盟开通了8个用户的量子密码网络;同月,日本将量子通信速率提高100倍,20km时通信速率达到1.02Mbit/s,100km时通信速率达到10.1kbit/s。目前,国外光纤量子密钥分配的通信距离达300km,量子密钥协商速率最高试验记录在50km光纤传输中超过1Mb/s[2]。图7 北京—天津量子密码实验[1]国内:2004年,郭光灿团队完成了途径北京望京—河北香河—天津宝坻的量子密钥分配,距离125km。2008年,潘建伟团队建成基于商用光纤和诱骗态相位编码的3节点量子通信网络,节点间距离达20km,能实现实时网络通话和3方通话。2009年,郭光灿团队建成世界上第一个“量子政务网”。同年9月,中国科技大学建成世界上第一个5节点全通型量子通信网络,实现实时语音量子密码通信。2011年5月,王建宇团队研发出兼容经典激光通信的“星地量子通信系统”,实现了星地之间同时进行量子通信和经典激光通信。2012年2月17日,合肥市城域量子通信实验示范网建成并进入试运行阶段,具有46个节点,光纤长度1700km,通过6个接入交换和集控站,连接40组“量子电话”用户和16组“量子视频”用户。2013年5月,中科院在国际上首次成功实现星地量子密钥分发的全方位地面试验。同年11月,济南量子保密通信试验网建成,包括三个集控站、50个用户节点[2]。在2016年8月16日,我国发射首颗“墨子号”量子卫星,这标志着我国在全球已构建出首个天地一体化广域量子通信网络雏形,为未来实现覆盖全球的量子保密通信网络迈出了新的一步。(2) 量子隐形传态1997 年,奥地利Zeilinger小组首次成功实现了量子隐形传态通信; 1998 年初,意大利Rome 小组实现将量子态从纠缠光子对中的一个光子传递到另一个光子上的方案; 同年底,美国CIT 团队实现了连续变量(连续相干光场) 的量子隐形传态,美国学者用核磁共振( NMR) 的方法,实现了核自旋量子态的隐形传送。2001 年,美国Shih Y H 团队在脉冲参量下转换中,利用非线性方法实施Bell 基的测量,完成量子隐形传态。2002年,澳大利亚学者将信息编码的激光束进行了“远距传物”。1997 年,我国潘建伟和荷兰学者波密斯特等人合作,首次实现了未知量子态的远程传输;2004 年,潘建伟小组在国际上首次实现五光子纠缠和终端开放的量子态隐形传输,此后又首次实现6光子、8光子纠缠态; 2011 年,在国际上首次成功实现了百公里量级的自由空间量子隐形传态和纠缠分发,解决了通讯卫星的远距离信息传输问题。2012年9月,奥地利、加拿大、德国和挪威研究人员,实现了长达143公里的“隐形传输”[2]。3.6 产业化进展与面临的挑战量子通信的战略意义吸引了西方各国科研机构的关注,IBM、NIST、Battelle、NTT、东芝、西门子等著名公司和机构一直密切关注其发展并投资相关研究。英国政府在2013年发布了为期5年的量子信息技术专项,投入2.7亿英镑用于量子通信和量子计算等方面的研究成果转化,促进新应用和新产业的形成。国外成立了多个专门从事量子通信技术成果转化和商业推广的实体公司。例如美国的MagiQ公司和瑞士日内瓦大学成立的idQuantique公司等,能够提供QKD量子通信的商用化器件、系统和解决方案。法国电信研究院成立的SeQureNet公司从事连续变量量子密钥分发产品的开发。美国洛斯阿拉莫斯国家实验室成立了Qubittek公司,主攻智能电网安全通信领域[4]。国内开展量子通信相关研究的代表性机构包括中国科学技术大学、中国科学院微系统所和技术物理所、清华大学、山西大学和南京大学等。以中国科学技术大学相关研究团队为核心发起成立了科大国盾量子、安徽问天量子和山东量子等产业化实体,进行量子通信前沿研究成果向应用技术和用化产品的转化,国家对量子通信领域持续的专项投入和政策扶持为其发展提供了强劲动力。(a) 量子密钥分发机 (b) 量子安全加密手机图 8 科大国盾量子公司的产品相比其他量子信息技术,QKD无论在理论中、试验中还是实际应用中,都已经取得了一些重要的进展。然而,大规模的应用和推广仍然面临一系列的困难和挑战[4],主要表现以下四个方面:(1) 初期市场规模和用户群体十分有限。量子通信目前主要面向的是有高安全性要求的特定应用场景,如银行、政务和国防等通信网络环境。传统通信业界对于量子通信的应用目前仍然持观望态度,参与度和热情较低。(2) 产业化供应链的建立尚需时日。QKD 系统采用的单光子源和光子探测器等核心器件与传统光学器件完全不同,生产将面临量子设备特有的器件参数、制造工艺等新的挑战,因此需要一段时间的发展与适应。(3) 行业标准与规范研尚不完善。对于任何高新技术而言,测试认证和标准化是商用化推广的必备条件,而新型测试认证技术的开发通常是非常复杂、昂贵和耗时的。目前测评技术和标准化研究已经成为量子通信实用化的一大瓶颈。(4) 基础设施建立目前难以实现。QKD 系统前期需要更多的投入与改造,将原有传统的通信系统升级量子通信系统,将消耗巨额的经济成本。QKD 系统的量子态信号和传统强光信号的混传,所以大规模量子通信组网需要额外的光纤资源进行支持,将对量子通信系统的应用造成限制。此外,量子通信无法共享传统光通信设备等基础设备,需要进行全新部署, 造成前期大量软硬件升级改造的高投入要求。4 量子计算量子计算利用量子态的叠加性和纠缠性信息的运算和处理,其最显著优势在于“操作的并行性”,即个叠加态的量子信息进行一次变换,相当于对个量子信息同时进行操作。在本章中,我们将首先介绍三种典型的量子算法的原理,进而介绍量子机器学习与深度学习算法相关知识,最后介绍量子计算机的基本原理和量子编码相关知识。4.1 典型量子算法量子算法是量子计算的灵魂。可以说,没有量子算法就无法实现量子计算的并行性。因此,寻找和设计量子算法是量子计算的关键。在量子算法的研究中,出现了三个里程碑式的重要算法:Shor算法,Grove算法和HHL算法,它们都具有较高的理论意义和应用价值。(1) Shor算法1994年,应用数学家Shor 提出了一个实用的量子算法,通常称为Shor算法[12]。它的出现使得大整数分解问题在量子计算机中在多项式时间内解决成为可能,它计算复杂度仅为 。显然,相比经典算法,Shor算法相当于进行了指数加速。算法主要思想是将整数质因子分解问题转化为求解量子傅里叶变换的周期,将多个输入制备为量子态叠加,进行并行处理和操作,从而到到了量子加速的目的。在实际应用中, 2001年,IBM公司的研究小组首次在开发的核磁共振(Nuclear magnetic resonance,NMR)量子计算机中使用Shor算法,成功将15分解成3×5,这一成果引起业界广泛的关注和讨论。理论上,一旦更多量子比特的量子计算机研究成功,对于1000位大整数,采用 Shor算法可以在不到1秒内即可进行素因子分解,而采用传统计算机分解需要年(而宇宙的年龄为年)。由此可见在量子计算机面前,现有的公开密钥 RSA体系不再安全。(2) Grove算法搜索问题指的是从个未分类的元素中寻找出某个特定的元素。对于该问题,经典算法逐个地进行搜寻,直到找到满足的元素为止,平均需要,时间复杂度为。由于很多问题都可以看作一个搜索问题,如寻找对称密码(DES/AES等)的正确密钥,搜索方程的最佳参数等,因此Grover算法的用途十分广泛。(3) HHL算法由于机器学习算法中的某些求参过程同样可看作是该类问题,因此学者们已经将 HHL 算法应用到机器学习领域,比如 K-means 聚类,支持向量机,数据拟合等算法中,从而达到加速的目的。4.2 量子机器学习与深度学习算法在量子算法中,有一类算法是应用在机器学习或深度学习领域。由于近年来人工智能和机器学习/深度学习的研究热潮,同样带动了量子机器学习/深度学习的发展和研究。众所周知,传统的机器学习/深度学习算法仍然面临计算瓶颈的挑战。然而,若充分利用量子计算的并行性,则可以进一步优化传统机器学习算法的效率,突破计算瓶颈,加速人工智能进程。量子机器学习的研究可追溯到1995年,Kak最先提出量子神经计算的概念[15]。相继学者们提出了量子聚类、量子深度学习和量子向量机等算法。2015年,潘建伟教授团队在小型光量子计算机上,首次实现了量子机器学习算法[16]。从经典—量子的二元概念出发可以将机器学习问题按照数据和算法类型的不同分为4类,如表1所示[9]。表1 机器学习分类量子机器学习的训练数据必须以某种可以为量子计算机识别的格式载入(即制备量子叠加态),经过量子机器学习算法处理以后形成输出,而此时的输出结果是量子叠加态的,需要经过测量得到最终结果[9],该流程如图9所示。图9量子机器学习的基本流程表2概述了目前文献中见到的一些典型量子机器学习算法,及其所需资源和性能改善特征[9]。表2 主要量子机器学习算法如前所述,量子机器学习算法相比经典算法,有以下显著优势:(1) 量子加速。由于量子态的可叠加性,相比传统计算机,量子算法可以在不增加硬件的基础上实现并行计算,在此基础上利用Shor算法、HHL算法和Grover搜索等算法,可实现相对于完成同样功能的经典算法的二次甚至指数加速[4]。(2) 节省内存空间。将经典数据通过制备量子态叠加编码为量子数据,并利用量子并行性进行存储,可实现指数级地节省存储硬件需求。4.3 量子计算机所谓量子计算机,它是指具有量子计算能力的物理设备。为什么要出现这种设备呢?主要有两个原因:(1) 外部原因:摩尔定律失效。根据摩尔定律,集成电路上可容纳的晶体管数目每隔24个月增加一倍,性能也相应增加一倍。然而,一方面随着芯片元件集成度的提高会导致单位体积内散热增加,由于材料散热速度有限,就会出现计算速度上限,产生“热耗效应”。另一方面元件尺寸的不断缩小,在纳米甚至埃尺度下经典世界的物理规律不再适用,出现“尺寸效应”。(2) 内部原因:量子计算机的强并行性。这是量子计算机相比传统计算机的显著优势,量子计算机和量子算法相互结合,可以将计算效率进行二倍加速甚至指数加速,例如传统计算机计算需要1年的任务,使用量子计算机可能需要不足1秒的时间。不同于传统计算机,量子计算机用来存储数据的对象是量子比特;不同于传统计算机,量子计算机用使用量子逻辑门进行信息操作,如对单个量子操作的逻辑门:泡利-X门,泡利-Y门,泡利-Z门和Hadamard门等;对两个量子操作的双量子逻辑门:受控非门CNOT,受控互换门SWAP等等。这些量子的逻辑门的操作可以看做一种矩阵变换,即乘以幺正矩阵(可看做正交矩阵从实数域推广到复数域)的过程。图10以Hadamard门为例,表述了对量子态的形象操作过程。图 10 量子门的操作示意图由图可知,Hadamard门可以将一个量子态变成两个量子态的叠加状态。形象地说,猫生的状态通过Hadamard门转换成生和死的叠加态(概率为状态幅度的平方,概率各为50%)。这种性质十分有用,是实现并行计算基础,可以将N个输入数据转换成一个叠加的量子态,一次量子计算操作,相当于进行了N个数据操作,即实现了N次的并行,后文提到的量子算法正是利用这些量子逻辑门的变换特性。其他量子逻辑门的幺正矩阵有所不同,但操作也类似,这里不做赘述。此外,量子计算机用使用的量子逻辑门是可逆的;而传统计算机的逻辑门一般是不可逆的。前者操作后产生的能量耗散,而后者进行幺正矩阵变换可实现可逆计算,它几乎不会产生额外的热量,从而解决能耗上的问题。与传统的计算机相同的是,量子计算机的理论模型仍然是图灵机。不同的是,量子计算目前并没有操作系统,代替用量子算法进行控制,这决定了目前的量子计算机并不是通用的计算机,而属于某种量子算法的专用计算机。量子计算机和传统计算机的比较结果如表3所示。表3 量子计算机VS 传统计算机量子计算机的基本原理如图11所示。它主要的过程如下:(1) 选择合适的量子算法,将待解决问题编程为适应量子计算的问题。(2) 将输入的经典数据制备为量子叠加态。(3) 在量子计算机中,通过量子算法的操作步骤,将输入的量子态进行多次幺正操作,最终得到量子末态。(4) 对量子末态进行特殊的测量,得到经典的输出结果。图 11 量子计算机工作原理流程图[20]迄今为止,科学家用来尝试实现量子计算机的硬件系统有许多种,包括液态核磁共振、离子阱、线性光学、超导、半导体量子点等。其中,超导和半导体量子点由于可集乘度高,容错性好等优点,目前被认为是实现量子计算机的两种可能方案[1]。最近,IBM宣布的研制50比特和谷歌研制的72比特量子计算机都是基于低温超导系统的方案。4.4 量子编码理论上,需要极少的量子比特便可在量子计算机中实现复杂的量子计算。然而现实中,一方面量子信道上和量子设备中总存在各种噪声,如量子比特的热量等;另一方面量子的“退相干性”[5]。在量子计算,需要使得所有的量子位都持续处于一种“相干态”,然而在现实中很难做到,目前“相干态”仅能维持几百毫秒,随着量子比特的数量以及与环境相互作用的可能性增加,这个挑战将变得越来越大。这两个因素都能导致量子比特的状态翻转或随机化,导致从而导致量子计算失败。量子编码的目的正是为了纠正或防止这些量子比特发生的错误。虽然量子编码和经典编码的基本想法类似,即要以合适的方式引进信息冗余,以提高信息的抗干扰能力,但量子码可不是经典码的简单推广。在在量子情况下,编码存在着一些基本困难,表现在如下3方面[7]:(1) 经典编码中,为引入信息冗余,需要将一个比特复制多个比特。但在量子力学中,量子态不可克隆。(2) 经典编码在纠错时,需要进行测量,以确定错误图样。在量子情况下,测量会引起态坍缩,从而破坏量子相干性。(3) 经典码中的错误只有一种,即0,1之间的跃迁。而量子错误的自由度要大得多,对于一个确定的输入态,其输出态可以是二维空间中的任意态。量子编码按其原理,可分为量子纠错码、量子防错码、和量子避错码,其中量子纠错码是经典纠错码的量子推广。在各种量子纠错方案,实际上都假设了发生错误的量子比特数是给定的,例如常见的有纠一位错的量子码。典型的方案是Shor首次给出了一个新颖的纠错编码技术[17],利用9个量子比特来编码一个量子比特信息,可以纠正一位比特错误。5 后量子密码量子计算的快速发展,对当前广泛成熟使用的经典密码算法,特别是公钥密码算法(如RSA和ECC等)产生了极大的威胁和挑战,具体包括[11]:(1) 所有基于整数分解和离散对数上的非对称密码体制都是不安全的。如RSA、EEC公钥密码算法,它们在多项式时间内可以破解。那么当前主流的公钥加密、数字签名算法将不再安全。(2) 分组密码和序列密码的比特安全性将降低为原来密钥长度的1/2。为了抵抗这种攻击,对称加密算法通过增加密钥长度(2倍密钥长度)即可。(3) Hash 算法比特安全性将降低为原来的2/3。为了抵抗量子计算的攻击,人们提出抗量子密码体制,也称为后量子密码体制(Post-Quantum Cryptography),即在量子计算机出现之后仍然安全的密码体制。它主要包含基于 Hash的密码体制、基于编码的密码体制、基于格的密码体制和基于多变量的密码体制。事实上,从上述的影响结果来看,目前量子计算仅对公钥密码影响最大,而对分组密码、序列密码、哈希算法相对影响较小,因此可以看作它们也具有一定的抗量子计算攻击的特性。表4 抗量子密码体制及其具体算法目前,美国和欧洲正在大力对其投入研究,并快速推动其实用化。2015 年8月,美国国家安全局 NSA 宣布将当前美国政府所使用的“密码算法 B 套件”进行安全性升级,用于2015年至抗量子密码算法标准正式发布的空窗期,并最终过渡到抗量子密码算法。2016 年秋到2017年11月,NIST面向全球征集抗量子密码算法,然后进行 3~5年的密码分析工作,预计在 2022年到2023年,完成抗量子密码标准算法起草并发布。6 总结量子信息技术主要包含量子通信和量子计算两个分支,本文分别介绍了这两个分支技术。从理论角度的看,可用数学证明QKD能达到“绝对安全”。然而实践中由于设备和技术的缺陷,QKD不可能达到理想的“绝对安全”,离完全实用化进程还有很长的路需要探索。对此持既批判吹捧量子密码替代传统密码的极端观点,也看好未来量子密码的发展前景。从目前技术成熟度来看,量子密钥分配 ( QKD ) 是最为成熟的量子技术,它结合对称加密技术形成安全的保密通信系统,目前已经实现了商用化,但主要面向政务、国防、金融等安全性要求很高的特定应用场景,离全面推广和实用化还有很长的距离。从工业界研究热度来看,多数IT和互联网公司致力于研究量子计算,提出“量子计算+人工智能”,以解决计算力瓶颈问题。它具有广泛的应用价值,值得持续关注。从影响程度来看,量子计算的发展对以RSA和ECC为代表公钥密码学产生了巨大威胁,但对对称加密算法(如AES)的威胁较少。可预见将来,即使量子计算机被研发出来,传统密码也不会完全被替代,而将出现传统密码与量子密码(QKD)相互促进、共同繁荣的景象。从我国发展状况来看,量子通信技术发展速度迅猛,在理论研究和实验技术上均取得了许多重大突破,成果卓越。然而,量子算法、量子计算机的研究与欧美发达国家相比,仍有很大的差距,相关研究仍需努力。参考文献[1] 郭光灿,张昊,王琴. 量子信息技术发展概况[J]. 南京邮电大学学报(自然科学版), 2017, 37(3):1-14.[2] 徐兵杰,刘文林,毛钧庆,等. 量子通信技术发展现状及面临的问题研究[J]. 通信技术, 2014(5):463-468.[3] 王矿岩. 量子通信技术发展现状及面临的问题研究[J]. 通讯世界, 2017(1):110-111.[4] 赖俊森,吴冰冰,汤瑞,等. 量子通信应用现状及发展分析[J]. 电信科学, 2016, 32(3):123-129.[5] Bennett C H, Brassard G. Quantum cryptography: Public key distribution and coin tossing[J]. Theoretical Computer Science, 2014, 560:7-11.[6] 陈锦俊, 吴令安, 范桁. 量子保密通讯及经典密码[J]. 物理, 2017, 46(3):137-144.[7] 段路明, 郭光灿. 量子信息讲座 第三讲 量子编码[J]. 物理, 1998(8):496-499.[8] 韩永建. 量子计算原理及研究进展[J]. 科技导报, 2017, 35(23):70-75.[9] 陆思聪, 郑昱, 王晓霆,等. 量子机器学习[J]. 控制理论与应用, 2017(11).[10] 黄一鸣, 雷航, 李晓瑜. 量子机器学习算法综述[J]. 计算机学报, 2018(1).[11] 刘文瑞. 抗量子计算攻击密码体制发展分析[J]. 通信技术, 2017, 50(5): 1054-1059.[12] Shor P W. Algorithms for quantum computation: Discrete logarithms and factoring [C]// Proceedings of the 35th Annual IEEE Symposium on the Foundations of Computer Science. Piscataway, NJ: IEEE, 1994:124-134.[13] Grover L K. A fast quantum mechanical algorithm for database search[C]// Twenty-Eighth ACM Symposium on Theory of Computing. ACM, 1996:212-219.[14] Harrow A W, Hassidim A, Lloyd S. Quantum algorithm for linear systems of equations. Phys Rev Lett, 2009, 103:150502.[15] Kak S. On quantum neural computing[J]. Systems Control & Information, 1995, 52(3-4):143-160.[16] Su Z E, Wang X L, Lu C Y, et al. Entanglement-based machine learning on aquantum computer[J]. Physical Review Letters, 2015, 114(11):110504.[17] Shor P W. Scheme for reducing decoherence in quantum computer memory[J]. Physical Review A, 1995, 52(4):R2493.[18] 孙晓明. 量子计算若干前沿问题综述[J]. 中国科学:信息科学, 2016, 46(8):982.[19] 赵红敏. 量子纠错与经典纠错的比较[J]. 河北科技大学学报, 2008, 29(3):211-213.[20] Makarov V. Quantum cryptography and quantum cryptanalysis [D]. 2007.[1] 这里“不可分割”的含义应该这样理解,比如不可能分割出0.5个原子。[2]如图4所示,测量基对应为两种不同的偏振片,每个偏振片有两个正交的方向。当偏振片方向可以通过偏振片时,测量结果正确。当偏振片方向不是偏振片的方向,无法通过偏振片,测量结果错误。[3]由2.3节可知,20个量子比特可同时存储100万个号码。[4] 表示计算复杂度从降为。[5]通俗地讲,两束频率完全相同的光源产生相干的量子,它们是相互关联的,即对一个量子进行处理,影响就会立即传送到另一个量子,它们是量子并行处理的基础。但由于外部环境的原因,量子由“相干态”退化为“非相干态”,操作一个量子不会影响另一个量子,它们之间是独立的(类似经典计算机的比特),这就是所谓的“退相干性”。来自微信

关于量子通信与量子计算,终于有人讲透了! EET0P2018年09月17日11:59来源:绿盟博客 作者:陈磊 原地址:http://blog.nsfocus.net/quantum-information-technology/本文首先介绍量子相关的基本概念、性质及基本原理;接着,从量子通信和量子计算两个部分阐述其原理与发展现状;然后,简单介绍了后量子密码学(也称抗量子密码体制)的发展情况;最后,对量子信息技术的发展进行总结与展望。文章目录1 引言2 量子信息简介2.1 量子概念2.2 量子基本特性2.3 量子信息2.4 量子信息学3 量子通信3.1 量子通信系统基本模型3.2 量子通信技术优势3.3 量子密钥分配基本原理3.4 量子隐形传态基本原理3.5 理论与试验研究进展3.6 产业化进展与面临的挑战4 量子计算4.1 典型量子算法4.2 量子机器学习与深度学习算法4.3 量子计算机4.4 量子编码5 后量子密码6 总结1 引言量子信息科学(Quantum Information)是以量子力学为基础,把量子系统“状态”所带有的物理信息,进行信息编码、计算和传输的全新信息技术。量子信息技术主要包括量子通信和量子计算,由于它们具有潜在的应用价值和重大的科学意义,正引起人们广泛的关注和研究。本文首先介绍量子相关的基本概念、性质及基本原理;接着,从量子通信和量子计算两个部分阐述其原理与发展现状;然后,简单介绍了后量子密码学(也称抗量子密码体制)的发展情况;最后,对量子信息技术的发展进行总结与展望。2 量子信息简介在本章中,首先介绍量子和量子信息基本概念及相关特性;然后介绍量子信息学领域的研究分支及其研究内容。2.1 量子概念量子(Quantum)属于一个微观的物理概念。如果一个物理量存在最小的不可分割的基本单位[1],那么称这个物理量是可量子化的,并把物理量的基本单位称为量子。现代物理中,将微观世界中所有的不可分割的微观粒子(光子、电子、原子等)或其状态等物理量统称为量子。量子这个概念最早由德国物理学家普朗克在1900年提出的,他假设黑体辐射中的辐射能量是不连续的,只能取能量基本单位的整数倍,这很好地解释了黑体辐射的实验现象。即假设对于一定频率的电磁辐射,物体只以“量子”的方式吸收和发射,每个“量子”的能量可以表示为:,为普朗克常数。量子假设的提出有力地冲击了牛顿力学为代表的经典物理学,促进物理学进入微观层面,奠定了现代物理学基础,进入了全新的领域。2.2 量子基本特性作为一种微观粒子,量子具有许多特别的基本特性,如量子力学三大基本原理:量子测不准也称为不确定性原理,即观察者不可能同时知道一个粒子的位置和它的速度,粒子位置的总是以一定的概率存在某一个不同的地方,而对未知状态系统的每一次测量都必将改变系统原来的状态。也就是说,测量后的微粒相比于测量之前,必然会产生变化。量子不可克隆量子不可克隆原理,即一个未知的量子态不能被完全地克隆。在量子力学中,不存在这样一个物理过程:实现对一个未知量子态的精确复制,使得每个复制态与初始量子态完全相同。量子不可区分量子不可区分原理,即不可能同时精确测量两个非正交量子态。事实上,由于非正交量子态具有不可区分性,无论采用任何测量方法,测量结果的都会有错误。除此之外,还包括以下基本特性:量子态叠加性(superposition)量子状态可以叠加,因此量子信息也是可以叠加的。这是量子计算中的可以实现并行性的重要基础,即可以同时输入和操作个量子比特的叠加态。量子态纠缠性(entanglement)两个及以上的量子在特定的(温度、磁场)环境下可以处于较稳定的量子纠缠状态,基于这种纠缠,某个粒子的作用将会瞬时地影响另一个粒子。爱因斯坦称其为: “幽灵般的超距作用”。量子态相干性(interference)量子力学中微观粒子间的相互叠加作用能产生类似经典力学中光的干涉现象。2.3 量子信息一个经典的二进制存储器只能存一个数:要么存 0,要么存 1。但一个二进制量子存储器却可以同时存储0和1这两个数。两个经典二进制存储器只能存储以下四个数的一个数: 00,01,10 或 11。倘若使用两个二进制量子存储器,则以上四个数可以同时被存储下来。按此规律,推广到N个二进制存储器的情况,理论上,N个量子存储器与N个经典存储器分别能够存储个数和1个数。由此可见,量子存储器的存储能力是呈指数增长的,它比经典存储器具有更强大的存储数据的能力,尤其是当 N很大时(如 N=250 ),量子存储器能够存储的数据量比宇宙中所有原子的数目还要多[1]。2.4 量子信息学量子信息学是量子力学与信息科学形成的一个交叉学科,该领域主要包括两个领域:量子通信和量子计算。其中量子通信主要研究的是量子介质的信息传递功能进行通信的一种技术,而量子计算则主要研究量子计算机和适合于量子计算机的量子算法。图 1 量子信息学的研究分支3 量子通信所谓量子通信,从概念角度来讲就是利用量子介质的信息传递功能进行通信的一种技术。它主要包括量子密钥分配、量子隐形传态等技术。量子密码 (Quantum Cryptography)是利用量子力学属性开发的密码系统。与传统的密码系统不同的是,它的安全性依赖于量子力学属性(不可测量和不可克隆等)而不是数学的复杂度理论。量子密钥分配是研究最为成熟的量子密码技术。在本章中,我们首先简单地介绍量子通信系统的基本模型以及优势,然后介绍量子密钥分配和量子隐形传态的基本原理。接着,概述量子通信的目前研究与发展现状。最后,总结量子通信目前存在的问题。3.1 量子通信系统基本模型量子通信体系架构包括量子态发生器、量子通道和量子测量装置以及经典信道等部分,其基本模型如图2所示。图 2 量子通信系统基本模型量子通信过程可以从发送端和接收端两个角度理解。在发送端,量子信源模块产生消息,消息通过量子编码模块转换成量子比特,量子比特通过量子调制模块得到以量子态为载体的量子信息,量子信息通过量子信道进行传输。除此以外,量子调制的模式信息(传统的信息)需要使用经典信道进行传输。在接收端,将接收到两部分信息:量子信道接收量子信息;经典信道接收额外的经典信息。这两部分信息通过解调和解码模块后,获得最终的消息。3.2 量子通信技术优势量子通信与传统通信技术相比,具有如下主要特点和优势:(1) 时效性高。量子通信的线路时延近乎为零,量子信道的信息效率相对于经典信道量子的信息效率高几十倍,传输速度快。(2) 抗干扰性能强。量子通信中的信息传输不通过传统信道(如传统移动通信为了使得通信不被干扰,需要约定好频率,而量子通信不需要考虑这些因素),与通信双方之间的传播媒介无关,不受空间环境的影响,具有完好的抗干扰性能。(3) 保密性能好。根据量子不可克隆定理,量子信息一经检测就会产生不可还原的改变,如果量子信息在传输中途被窃取,接收者必定能发现。(4) 隐蔽性能好。量子通信没有电磁辐射,第三方无法进行无线监听或探测。(5) 应用广泛。量子通信与传播媒介无关,传输不会被任何障碍阻隔,量子隐形传态通信还能穿越大气层。因此,量子通信应用广泛,既可在太空中通信,又可在海底通信,还可在光纤等介质中通信。3.3 量子密钥分配基本原理量子密钥分配 (Quantum Key Distribution, QKD)以量子态为信息载体,通过量子信道使通信收发双方共享密钥,是密码学与量子力学相结合的产物。QKD 技术在通信中并不传输密文,而是利用量子信道将密钥分配给通信双方,由于量子力学的测不准和量子不可克隆定理,攻击者无法获取正确的密钥。基于QKD 技术的保密通信系统结构如图3所示,其中上路负责密钥分配,下路负责传输加解密数据。在上路中,量子信道负责传输量子密钥,经典信道负责传输测量基[2]等额外需要的信息。下面,将以BB84[5]方案为例,具体地介绍两条信道起到的作用。图 3 基于QKD 的量子保密通信系统BB84 方案。1984 年,Brassard与Bennett联合提出了第一个实用型量子密钥分配系统—BB84 方案,系统架构如图4 所示。图 4 BB84协议示意图[20]该方案通过量子信道传送密钥,量子信道的信息载体是单个量子,通过量子的相位、极化方向或频率等物理量携带量子密钥信息。BB84 方案利用单个量子作为信息载体两组共扼基,每组基中的两个极化互相正交。由于理想状态的量子信道无法实现,BB84 方案还利用经典信道进行量子态测量方法的协商和码序列的验证。有趣的现象:接收端必须使用正确的测量基,才能正确地测出量子比特(光量子的偏振态);使用错误的测量基,测量结果将发生错误,同时光量子的偏振态发生改变,如图5所示。图 5测量基对测量结果的影响[20]有了以上基础后,理解BB84协议将变得相对容易,其主要步骤如下:量子信道部分(1) Alice发送随机的量子比特串给Bob。Alice随机选择四种偏振片,制备不同偏振状态的光量子,得到足够多的随机量子比特并将其发送给Bob。(2) Bob随机选择测量基测量量子比特。由于Bob并不知道光量子是由发送端那一种测量基编码的,所以他也只能随机选择测量基来进行测量。当选择正确的测量基时,测量的结果正确。当使用错误的测量结果时,测量结果错误。经典信道部分(3) Bob将使用的测量基发送给Alice。(4) Alice将接收的测量基与使用的测量基进行比较,并通过信息告诉Bob哪些位置的测量基是正确的。(5) Bob根据Alice的消息剔除错误的量子比特,并将选择少部分正确的测量结果告诉Alice。(6) Alice确认Bob测量结果的正确性。若错误,则说明存在量子信道可能存在窃听,停止通信或者返回第 (1) 步(由于实际的量子信道中也存在噪声,因此会根据一个错误率阈值判断是否窃听和停止通信)。若正确,剔除部分的量子比特,剩下的二进制串作为最终的密钥。并发送确认信息给Bob。(7) Bob收到确认信息。同样剔除部分的量子比特,剩下的二进制串作为最终的密钥。我们对BB84协议的安全性做一个简单的分析:如果Eve在量子信道中旁路窃听,由于量子不可克隆,因此Eve无法复制出一份相同的量子比特副本;如果他在量子信道中直接测量光量子,由于Eve不知正确的测量基,他也会随机选择,有50%的概率选择正确,50%的概率选择错误。若选择的测量基错误,有上述的有趣的现象可知,测量结果错误,同时光量子的偏振态发生改变。当协议的步骤由 (2) 执行到 (6) 时,Alice将发现到量子信道的窃听,那么她将终止这一过程。如果在经典信道进行窃听呢?实际上也是无效的。即使Eve知道了测量基信息(步骤 (3)),然而由于量子不可克隆,无法得到正确的量子比特串副本。由以上分析可知,BB84协议基于量子不可克隆等原理,实现安全的密钥分配过程。3.4 量子隐形传态基本原理量子隐形传态( Quantum Teleportation) 又称量子远程传态或量子离物传态,是利用量子纠缠的不确定特性,将某个量子的未知量子态通过EPR对(纠缠量子对)的一个量子传送到另一个地方(即EPR对中另一个量子),而原来的量子仍留在原处。如图所示6所示,Alice想和Bob通信,具体流程如下:(1) 制备两个有纠缠的EPR量子(粒子)对,然后将其分开,Alice和Bob各持一个,分别是粒子1和粒子2。(2) Alice粒子1和某一个未知量子态的粒子3进行联合测量,然后将测量结果通过经典信道传送给接Bob。此时,神奇的事情发生了:Bob持有的粒子2将随着Alice测量同时发生改变,由一量子态变成新的量子态。这是由于量子纠缠的作用,粒子2和粒子1之间如同有一根无形。(3) Bob根据接收的息和拥有粒子2做相应幺正变换(一种量子计算变换),根据这些信息,可以重构出粒子3的全貌。图 6 量子隐形传态原理图3.5 理论与试验研究进展1993年,学术界给出了一种利用量子技术传输信息的实际方案,4年后量子通信技术在奥地利科学家的实验室中正式完成了实验验证。经过十多年的发展,量子通信先后实现了信息传递从600m(2007年)到通信距离144km(2012年)的巨大跨越,标志量子通信从理论阶段走向实用化阶段。下面从量子密钥分配和量子隐形传态两个主要研究领域进行介绍。(1) 量子密钥分配国外:1993年,英国研究小组首先在光纤中,使用相位编码的方法实现了BB84方案,通信传输距离达10km;1995年,该小组将距离提升到30km。瑞士于1993年用偏振光子实现了BB84方案,光子波长1.3mm,传输距离1.1km,误码率0.54%;1995年,将距离提升到23km,误码率为3.4%;2002年,传输距离达到67km。2000年,美国实现自由空间量子密钥分配通信,传输距离达1.6km。2003年,欧洲研究小组实现自由空间中23km的通信。2008年10月,欧盟开通了8个用户的量子密码网络;同月,日本将量子通信速率提高100倍,20km时通信速率达到1.02Mbit/s,100km时通信速率达到10.1kbit/s。目前,国外光纤量子密钥分配的通信距离达300km,量子密钥协商速率最高试验记录在50km光纤传输中超过1Mb/s[2]。图7 北京—天津量子密码实验[1]国内:2004年,郭光灿团队完成了途径北京望京—河北香河—天津宝坻的量子密钥分配,距离125km。2008年,潘建伟团队建成基于商用光纤和诱骗态相位编码的3节点量子通信网络,节点间距离达20km,能实现实时网络通话和3方通话。2009年,郭光灿团队建成世界上第一个“量子政务网”。同年9月,中国科技大学建成世界上第一个5节点全通型量子通信网络,实现实时语音量子密码通信。2011年5月,王建宇团队研发出兼容经典激光通信的“星地量子通信系统”,实现了星地之间同时进行量子通信和经典激光通信。2012年2月17日,合肥市城域量子通信实验示范网建成并进入试运行阶段,具有46个节点,光纤长度1700km,通过6个接入交换和集控站,连接40组“量子电话”用户和16组“量子视频”用户。2013年5月,中科院在国际上首次成功实现星地量子密钥分发的全方位地面试验。同年11月,济南量子保密通信试验网建成,包括三个集控站、50个用户节点[2]。在2016年8月16日,我国发射首颗“墨子号”量子卫星,这标志着我国在全球已构建出首个天地一体化广域量子通信网络雏形,为未来实现覆盖全球的量子保密通信网络迈出了新的一步。(2) 量子隐形传态1997 年,奥地利Zeilinger小组首次成功实现了量子隐形传态通信; 1998 年初,意大利Rome 小组实现将量子态从纠缠光子对中的一个光子传递到另一个光子上的方案; 同年底,美国CIT 团队实现了连续变量(连续相干光场) 的量子隐形传态,美国学者用核磁共振( NMR) 的方法,实现了核自旋量子态的隐形传送。2001 年,美国Shih Y H 团队在脉冲参量下转换中,利用非线性方法实施Bell 基的测量,完成量子隐形传态。2002年,澳大利亚学者将信息编码的激光束进行了“远距传物”。1997 年,我国潘建伟和荷兰学者波密斯特等人合作,首次实现了未知量子态的远程传输;2004 年,潘建伟小组在国际上首次实现五光子纠缠和终端开放的量子态隐形传输,此后又首次实现6光子、8光子纠缠态; 2011 年,在国际上首次成功实现了百公里量级的自由空间量子隐形传态和纠缠分发,解决了通讯卫星的远距离信息传输问题。2012年9月,奥地利、加拿大、德国和挪威研究人员,实现了长达143公里的“隐形传输”[2]。3.6 产业化进展与面临的挑战量子通信的战略意义吸引了西方各国科研机构的关注,IBM、NIST、Battelle、NTT、东芝、西门子等著名公司和机构一直密切关注其发展并投资相关研究。英国政府在2013年发布了为期5年的量子信息技术专项,投入2.7亿英镑用于量子通信和量子计算等方面的研究成果转化,促进新应用和新产业的形成。国外成立了多个专门从事量子通信技术成果转化和商业推广的实体公司。例如美国的MagiQ公司和瑞士日内瓦大学成立的idQuantique公司等,能够提供QKD量子通信的商用化器件、系统和解决方案。法国电信研究院成立的SeQureNet公司从事连续变量量子密钥分发产品的开发。美国洛斯阿拉莫斯国家实验室成立了Qubittek公司,主攻智能电网安全通信领域[4]。国内开展量子通信相关研究的代表性机构包括中国科学技术大学、中国科学院微系统所和技术物理所、清华大学、山西大学和南京大学等。以中国科学技术大学相关研究团队为核心发起成立了科大国盾量子、安徽问天量子和山东量子等产业化实体,进行量子通信前沿研究成果向应用技术和用化产品的转化,国家对量子通信领域持续的专项投入和政策扶持为其发展提供了强劲动力。(a) 量子密钥分发机 (b) 量子安全加密手机图 8 科大国盾量子公司的产品相比其他量子信息技术,QKD无论在理论中、试验中还是实际应用中,都已经取得了一些重要的进展。然而,大规模的应用和推广仍然面临一系列的困难和挑战[4],主要表现以下四个方面:(1) 初期市场规模和用户群体十分有限。量子通信目前主要面向的是有高安全性要求的特定应用场景,如银行、政务和国防等通信网络环境。传统通信业界对于量子通信的应用目前仍然持观望态度,参与度和热情较低。(2) 产业化供应链的建立尚需时日。QKD 系统采用的单光子源和光子探测器等核心器件与传统光学器件完全不同,生产将面临量子设备特有的器件参数、制造工艺等新的挑战,因此需要一段时间的发展与适应。(3) 行业标准与规范研尚不完善。对于任何高新技术而言,测试认证和标准化是商用化推广的必备条件,而新型测试认证技术的开发通常是非常复杂、昂贵和耗时的。目前测评技术和标准化研究已经成为量子通信实用化的一大瓶颈。(4) 基础设施建立目前难以实现。QKD 系统前期需要更多的投入与改造,将原有传统的通信系统升级量子通信系统,将消耗巨额的经济成本。QKD 系统的量子态信号和传统强光信号的混传,所以大规模量子通信组网需要额外的光纤资源进行支持,将对量子通信系统的应用造成限制。此外,量子通信无法共享传统光通信设备等基础设备,需要进行全新部署, 造成前期大量软硬件升级改造的高投入要求。4 量子计算量子计算利用量子态的叠加性和纠缠性信息的运算和处理,其最显著优势在于“操作的并行性”,即个叠加态的量子信息进行一次变换,相当于对个量子信息同时进行操作。在本章中,我们将首先介绍三种典型的量子算法的原理,进而介绍量子机器学习与深度学习算法相关知识,最后介绍量子计算机的基本原理和量子编码相关知识。4.1 典型量子算法量子算法是量子计算的灵魂。可以说,没有量子算法就无法实现量子计算的并行性。因此,寻找和设计量子算法是量子计算的关键。在量子算法的研究中,出现了三个里程碑式的重要算法:Shor算法,Grove算法和HHL算法,它们都具有较高的理论意义和应用价值。(1) Shor算法1994年,应用数学家Shor 提出了一个实用的量子算法,通常称为Shor算法[12]。它的出现使得大整数分解问题在量子计算机中在多项式时间内解决成为可能,它计算复杂度仅为 。显然,相比经典算法,Shor算法相当于进行了指数加速。算法主要思想是将整数质因子分解问题转化为求解量子傅里叶变换的周期,将多个输入制备为量子态叠加,进行并行处理和操作,从而到到了量子加速的目的。在实际应用中, 2001年,IBM公司的研究小组首次在开发的核磁共振(Nuclear magnetic resonance,NMR)量子计算机中使用Shor算法,成功将15分解成3×5,这一成果引起业界广泛的关注和讨论。理论上,一旦更多量子比特的量子计算机研究成功,对于1000位大整数,采用 Shor算法可以在不到1秒内即可进行素因子分解,而采用传统计算机分解需要年(而宇宙的年龄为年)。由此可见在量子计算机面前,现有的公开密钥 RSA体系不再安全。(2) Grove算法搜索问题指的是从个未分类的元素中寻找出某个特定的元素。对于该问题,经典算法逐个地进行搜寻,直到找到满足的元素为止,平均需要,时间复杂度为。由于很多问题都可以看作一个搜索问题,如寻找对称密码(DES/AES等)的正确密钥,搜索方程的最佳参数等,因此Grover算法的用途十分广泛。(3) HHL算法由于机器学习算法中的某些求参过程同样可看作是该类问题,因此学者们已经将 HHL 算法应用到机器学习领域,比如 K-means 聚类,支持向量机,数据拟合等算法中,从而达到加速的目的。4.2 量子机器学习与深度学习算法在量子算法中,有一类算法是应用在机器学习或深度学习领域。由于近年来人工智能和机器学习/深度学习的研究热潮,同样带动了量子机器学习/深度学习的发展和研究。众所周知,传统的机器学习/深度学习算法仍然面临计算瓶颈的挑战。然而,若充分利用量子计算的并行性,则可以进一步优化传统机器学习算法的效率,突破计算瓶颈,加速人工智能进程。量子机器学习的研究可追溯到1995年,Kak最先提出量子神经计算的概念[15]。相继学者们提出了量子聚类、量子深度学习和量子向量机等算法。2015年,潘建伟教授团队在小型光量子计算机上,首次实现了量子机器学习算法[16]。从经典—量子的二元概念出发可以将机器学习问题按照数据和算法类型的不同分为4类,如表1所示[9]。表1 机器学习分类量子机器学习的训练数据必须以某种可以为量子计算机识别的格式载入(即制备量子叠加态),经过量子机器学习算法处理以后形成输出,而此时的输出结果是量子叠加态的,需要经过测量得到最终结果[9],该流程如图9所示。图9量子机器学习的基本流程表2概述了目前文献中见到的一些典型量子机器学习算法,及其所需资源和性能改善特征[9]。表2 主要量子机器学习算法如前所述,量子机器学习算法相比经典算法,有以下显著优势:(1) 量子加速。由于量子态的可叠加性,相比传统计算机,量子算法可以在不增加硬件的基础上实现并行计算,在此基础上利用Shor算法、HHL算法和Grover搜索等算法,可实现相对于完成同样功能的经典算法的二次甚至指数加速[4]。(2) 节省内存空间。将经典数据通过制备量子态叠加编码为量子数据,并利用量子并行性进行存储,可实现指数级地节省存储硬件需求。4.3 量子计算机所谓量子计算机,它是指具有量子计算能力的物理设备。为什么要出现这种设备呢?主要有两个原因:(1) 外部原因:摩尔定律失效。根据摩尔定律,集成电路上可容纳的晶体管数目每隔24个月增加一倍,性能也相应增加一倍。然而,一方面随着芯片元件集成度的提高会导致单位体积内散热增加,由于材料散热速度有限,就会出现计算速度上限,产生“热耗效应”。另一方面元件尺寸的不断缩小,在纳米甚至埃尺度下经典世界的物理规律不再适用,出现“尺寸效应”。(2) 内部原因:量子计算机的强并行性。这是量子计算机相比传统计算机的显著优势,量子计算机和量子算法相互结合,可以将计算效率进行二倍加速甚至指数加速,例如传统计算机计算需要1年的任务,使用量子计算机可能需要不足1秒的时间。不同于传统计算机,量子计算机用来存储数据的对象是量子比特;不同于传统计算机,量子计算机用使用量子逻辑门进行信息操作,如对单个量子操作的逻辑门:泡利-X门,泡利-Y门,泡利-Z门和Hadamard门等;对两个量子操作的双量子逻辑门:受控非门CNOT,受控互换门SWAP等等。这些量子的逻辑门的操作可以看做一种矩阵变换,即乘以幺正矩阵(可看做正交矩阵从实数域推广到复数域)的过程。图10以Hadamard门为例,表述了对量子态的形象操作过程。图 10 量子门的操作示意图由图可知,Hadamard门可以将一个量子态变成两个量子态的叠加状态。形象地说,猫生的状态通过Hadamard门转换成生和死的叠加态(概率为状态幅度的平方,概率各为50%)。这种性质十分有用,是实现并行计算基础,可以将N个输入数据转换成一个叠加的量子态,一次量子计算操作,相当于进行了N个数据操作,即实现了N次的并行,后文提到的量子算法正是利用这些量子逻辑门的变换特性。其他量子逻辑门的幺正矩阵有所不同,但操作也类似,这里不做赘述。此外,量子计算机用使用的量子逻辑门是可逆的;而传统计算机的逻辑门一般是不可逆的。前者操作后产生的能量耗散,而后者进行幺正矩阵变换可实现可逆计算,它几乎不会产生额外的热量,从而解决能耗上的问题。与传统的计算机相同的是,量子计算机的理论模型仍然是图灵机。不同的是,量子计算目前并没有操作系统,代替用量子算法进行控制,这决定了目前的量子计算机并不是通用的计算机,而属于某种量子算法的专用计算机。量子计算机和传统计算机的比较结果如表3所示。表3 量子计算机VS 传统计算机量子计算机的基本原理如图11所示。它主要的过程如下:(1) 选择合适的量子算法,将待解决问题编程为适应量子计算的问题。(2) 将输入的经典数据制备为量子叠加态。(3) 在量子计算机中,通过量子算法的操作步骤,将输入的量子态进行多次幺正操作,最终得到量子末态。(4) 对量子末态进行特殊的测量,得到经典的输出结果。图 11 量子计算机工作原理流程图[20]迄今为止,科学家用来尝试实现量子计算机的硬件系统有许多种,包括液态核磁共振、离子阱、线性光学、超导、半导体量子点等。其中,超导和半导体量子点由于可集乘度高,容错性好等优点,目前被认为是实现量子计算机的两种可能方案[1]。最近,IBM宣布的研制50比特和谷歌研制的72比特量子计算机都是基于低温超导系统的方案。4.4 量子编码理论上,需要极少的量子比特便可在量子计算机中实现复杂的量子计算。然而现实中,一方面量子信道上和量子设备中总存在各种噪声,如量子比特的热量等;另一方面量子的“退相干性”[5]。在量子计算,需要使得所有的量子位都持续处于一种“相干态”,然而在现实中很难做到,目前“相干态”仅能维持几百毫秒,随着量子比特的数量以及与环境相互作用的可能性增加,这个挑战将变得越来越大。这两个因素都能导致量子比特的状态翻转或随机化,导致从而导致量子计算失败。量子编码的目的正是为了纠正或防止这些量子比特发生的错误。虽然量子编码和经典编码的基本想法类似,即要以合适的方式引进信息冗余,以提高信息的抗干扰能力,但量子码可不是经典码的简单推广。在在量子情况下,编码存在着一些基本困难,表现在如下3方面[7]:(1) 经典编码中,为引入信息冗余,需要将一个比特复制多个比特。但在量子力学中,量子态不可克隆。(2) 经典编码在纠错时,需要进行测量,以确定错误图样。在量子情况下,测量会引起态坍缩,从而破坏量子相干性。(3) 经典码中的错误只有一种,即0,1之间的跃迁。而量子错误的自由度要大得多,对于一个确定的输入态,其输出态可以是二维空间中的任意态。量子编码按其原理,可分为量子纠错码、量子防错码、和量子避错码,其中量子纠错码是经典纠错码的量子推广。在各种量子纠错方案,实际上都假设了发生错误的量子比特数是给定的,例如常见的有纠一位错的量子码。典型的方案是Shor首次给出了一个新颖的纠错编码技术[17],利用9个量子比特来编码一个量子比特信息,可以纠正一位比特错误。5 后量子密码量子计算的快速发展,对当前广泛成熟使用的经典密码算法,特别是公钥密码算法(如RSA和ECC等)产生了极大的威胁和挑战,具体包括[11]:(1) 所有基于整数分解和离散对数上的非对称密码体制都是不安全的。如RSA、EEC公钥密码算法,它们在多项式时间内可以破解。那么当前主流的公钥加密、数字签名算法将不再安全。(2) 分组密码和序列密码的比特安全性将降低为原来密钥长度的1/2。为了抵抗这种攻击,对称加密算法通过增加密钥长度(2倍密钥长度)即可。(3) Hash 算法比特安全性将降低为原来的2/3。为了抵抗量子计算的攻击,人们提出抗量子密码体制,也称为后量子密码体制(Post-Quantum Cryptography),即在量子计算机出现之后仍然安全的密码体制。它主要包含基于 Hash的密码体制、基于编码的密码体制、基于格的密码体制和基于多变量的密码体制。事实上,从上述的影响结果来看,目前量子计算仅对公钥密码影响最大,而对分组密码、序列密码、哈希算法相对影响较小,因此可以看作它们也具有一定的抗量子计算攻击的特性。表4 抗量子密码体制及其具体算法目前,美国和欧洲正在大力对其投入研究,并快速推动其实用化。2015 年8月,美国国家安全局 NSA 宣布将当前美国政府所使用的“密码算法 B 套件”进行安全性升级,用于2015年至抗量子密码算法标准正式发布的空窗期,并最终过渡到抗量子密码算法。2016 年秋到2017年11月,NIST面向全球征集抗量子密码算法,然后进行 3~5年的密码分析工作,预计在 2022年到2023年,完成抗量子密码标准算法起草并发布。6 总结量子信息技术主要包含量子通信和量子计算两个分支,本文分别介绍了这两个分支技术。从理论角度的看,可用数学证明QKD能达到“绝对安全”。然而实践中由于设备和技术的缺陷,QKD不可能达到理想的“绝对安全”,离完全实用化进程还有很长的路需要探索。对此持既批判吹捧量子密码替代传统密码的极端观点,也看好未来量子密码的发展前景。从目前技术成熟度来看,量子密钥分配 ( QKD ) 是最为成熟的量子技术,它结合对称加密技术形成安全的保密通信系统,目前已经实现了商用化,但主要面向政务、国防、金融等安全性要求很高的特定应用场景,离全面推广和实用化还有很长的距离。从工业界研究热度来看,多数IT和互联网公司致力于研究量子计算,提出“量子计算+人工智能”,以解决计算力瓶颈问题。它具有广泛的应用价值,值得持续关注。从影响程度来看,量子计算的发展对以RSA和ECC为代表公钥密码学产生了巨大威胁,但对对称加密算法(如AES)的威胁较少。可预见将来,即使量子计算机被研发出来,传统密码也不会完全被替代,而将出现传统密码与量子密码(QKD)相互促进、共同繁荣的景象。从我国发展状况来看,量子通信技术发展速度迅猛,在理论研究和实验技术上均取得了许多重大突破,成果卓越。然而,量子算法、量子计算机的研究与欧美发达国家相比,仍有很大的差距,相关研究仍需努力。参考文献[1] 郭光灿,张昊,王琴. 量子信息技术发展概况[J]. 南京邮电大学学报(自然科学版), 2017, 37(3):1-14.[2] 徐兵杰,刘文林,毛钧庆,等. 量子通信技术发展现状及面临的问题研究[J]. 通信技术, 2014(5):463-468.[3] 王矿岩. 量子通信技术发展现状及面临的问题研究[J]. 通讯世界, 2017(1):110-111.[4] 赖俊森,吴冰冰,汤瑞,等. 量子通信应用现状及发展分析[J]. 电信科学, 2016, 32(3):123-129.[5] Bennett C H, Brassard G. Quantum cryptography: Public key distribution and coin tossing[J]. Theoretical Computer Science, 2014, 560:7-11.[6] 陈锦俊, 吴令安, 范桁. 量子保密通讯及经典密码[J]. 物理, 2017, 46(3):137-144.[7] 段路明, 郭光灿. 量子信息讲座 第三讲 量子编码[J]. 物理, 1998(8):496-499.[8] 韩永建. 量子计算原理及研究进展[J]. 科技导报, 2017, 35(23):70-75.[9] 陆思聪, 郑昱, 王晓霆,等. 量子机器学习[J]. 控制理论与应用, 2017(11).[10] 黄一鸣, 雷航, 李晓瑜. 量子机器学习算法综述[J]. 计算机学报, 2018(1).[11] 刘文瑞. 抗量子计算攻击密码体制发展分析[J]. 通信技术, 2017, 50(5): 1054-1059.[12] Shor P W. Algorithms for quantum computation: Discrete logarithms and factoring [C]// Proceedings of the 35th Annual IEEE Symposium on the Foundations of Computer Science. Piscataway, NJ: IEEE, 1994:124-134.[13] Grover L K. A fast quantum mechanical algorithm for database search[C]// Twenty-Eighth ACM Symposium on Theory of Computing. ACM, 1996:212-219.[14] Harrow A W, Hassidim A, Lloyd S. Quantum algorithm for linear systems of equations. Phys Rev Lett, 2009, 103:150502.[15] Kak S. On quantum neural computing[J]. Systems Control & Information, 1995, 52(3-4):143-160.[16] Su Z E, Wang X L, Lu C Y, et al. Entanglement-based machine learning on aquantum computer[J]. Physical Review Letters, 2015, 114(11):110504.[17] Shor P W. Scheme for reducing decoherence in quantum computer memory[J]. Physical Review A, 1995, 52(4):R2493.[18] 孙晓明. 量子计算若干前沿问题综述[J]. 中国科学:信息科学, 2016, 46(8):982.[19] 赵红敏. 量子纠错与经典纠错的比较[J]. 河北科技大学学报, 2008, 29(3):211-213.[20] Makarov V. Quantum cryptography and quantum cryptanalysis [D]. 2007.[1] 这里“不可分割”的含义应该这样理解,比如不可能分割出0.5个原子。[2]如图4所示,测量基对应为两种不同的偏振片,每个偏振片有两个正交的方向。当偏振片方向可以通过偏振片时,测量结果正确。当偏振片方向不是偏振片的方向,无法通过偏振片,测量结果错误。[3]由2.3节可知,20个量子比特可同时存储100万个号码。[4] 表示计算复杂度从降为。[5]通俗地讲,两束频率完全相同的光源产生相干的量子,它们是相互关联的,即对一个量子进行处理,影响就会立即传送到另一个量子,它们是量子并行处理的基础。但由于外部环境的原因,量子由“相干态”退化为“非相干态”,操作一个量子不会影响另一个量子,它们之间是独立的(类似经典计算机的比特),这就是所谓的“退相干性”。来自微信 -

IoT的核心:盘点下一代超低功耗节点黑科技 李飞的说2018年08月27日08:09随着物联网的逐渐铺开,人们已经在生活中看到了越来越多的物联网模块:智能水表,共享单车,等等。目前的物联网仍然主要由运营商推动,物联网模块需要使用标准蜂窝协议与基站通讯。由于基站需要覆盖尽可能大的面积,因此物联网模块需要能做到在距离基站很远时仍能通讯,这就对于物联网模块的射频发射功率有了很高的要求;从另一个角度来说,物联网模块在做无线通讯时仍然需要消耗高达30mA的电流,这使得目前的物联网模组仍然需要配合较高容量的电池(如五号电池)才能工作,这也导致了物联网模组的尺寸很难做小。为了能进一步普及物联网,必须克服这个功耗以及尺寸的限制。例如,如果未来要把物联网做到植入人体内,则不可能再搭配五号电池,而必须使用更小的电池甚至使用能量获取系统从环境中获取能量彻底摆脱电池的限制。为了实现这个目标,从通讯协议上说,可以使用更低功耗的自组网技术,类似BLE;而从电路实现上,则必须使用创新电路来降低功耗。能量获取技术根据之前的讨论,目前电池的尺寸和成本都已经成为了限制IoT设备近一步进入潜在市场的瓶颈。那么,有没有可能使用从环境中获得能量来支持物联网节点工作呢?这种从环境中获取能量来支持物联网节点工作的模块叫做“能量获取”(energy harvesting),目前能量获取电路芯片的研究已经成为了研究领域的热门方向。目前最成熟的能量获取系统可以说是太阳能电池。传统太阳能电池能提供较好的能量获取效率,但是付出的代价是难以集成到CMOS芯片上。最近,不少研究机构都在使用新型CMOS太阳能电池,从而可以和物联网节点的其他模块集成到同一块芯片上,大大增加了集成度并减小模组尺寸。当然,集成在CMOS芯片上的太阳能电池需要付出低能量输出的代价,目前常见的CMOS片上太阳能电池在室内灯光下能提供nW等级的功率输出,而在强光下能提供uW级别的功率输出,这就对物联网模组的整体功耗优化提出了很高的要求。另一方面,也可以将能量获取与小尺寸微型电池配合使用,当光照较好时使用太阳能电池而在光照较弱时使用备用电池,从而提升整体物联网模组的电池寿命。除了太阳能电池外,另一个广为人知的环境能量就是WiFi信号。今年ISSCC上,来自俄勒冈州立大学的研究组发表了从环境中的WiFi信号获取能量的芯片。先来点背景知识:WiFi的最大发射功率是30dBm(即1W),在简单的环境里(即没有遮挡等)信号功率随着与发射设备的距离平方衰减,在距离3m左右的距离信号功率就衰减到了1uW(-30dBm)左右,而如果有物体遮挡则会导致功率更小。俄勒冈州立大学发表的论文中,芯片配合直径为1.5cm的天线可以在非常低的无线信号功率(-33dBm即500nW)下也能工作给电池充电,能量获取效率在5-10%左右(即在距离发射源3m的情况下输出功率在50nW左右)。因此,WiFi信号也可以用来给物联网模组提供能量,但是其输出功率在现实的距离上也不大,同样也需要节点模组对于功耗做深度优化。另外,机械能也可以作为物联网节点的能量获取来源。压电效应可以把机械能转换为电能,从而使用压电材料(例如压电MEMS)就能为物联网节点充电。使用压电材料做能量源的典型应用包括各种智能城市和工业应用,例如当有车压过减速带的时候,减速带下的物联网传感器上的压电材料可以利用车辆压力的机械能给传感器充电并唤醒传感器,从而实现车辆数量统计等。这样,机械压力即可以作为需要测量的信号,其本身又可以作为能量源,所以在没有信号的时候就无需浪费能量了!压电材料的输出功率随着机械能的大小不同会有很大的区别,一般在nW-mW的数量级范围。唤醒式无线系统传统的IoT无线收发系统使用的往往是周期性通讯或主动事件驱动通讯的方案。周期性通讯指的是IoT节点定期打开与中心节点通讯,并在其他时间休眠;事件驱动通讯则是指IoT节点仅仅在传感器监测到特定事件时才与中心节点通讯,而其它时候都休眠。在这两种模式中,都需要IoT节点主动与中心节点建立连接并通讯。然而,这个建立连接的过程是非常消耗能量的。因此,唤醒式无线系统的概念就应运而生。什么是唤醒式无线系统?就是该该系统在大多数时候都是休眠的,仅仅当主节点发射特定信号时才会唤醒无线系统。换句话说,连接的建立这个耗费能量的过程并不由IoT节点来完成,而是由中心节点通过发送唤醒信号来完成。当建立连接的事件由中心节点来驱动时,一切都变得简单。首先,中心节点可以发射一段射频信号,而IoT节点可以通过能量获取(energy harvesting)电路从该射频信号中获取能量为内部电容充电。当IoT节点的电容充电完毕后,无线连接系统就可以使用电容里的能量来发射射频信号与中心节点通讯。这样一来,就可以做到无电池操作。想象一下,如果不是使用唤醒式无线系统,而是使用IoT主动连接的话,无电池就会变得困难,因为无法保证IoT节点在需要通讯的时候在节点内有足够的能量。反之,现在使用唤醒式系统,中心节点在需要IoT节点工作时首先为其充电唤醒,就能保证每次IoT节点都有足够能量通讯。那么,这样的唤醒式无线系统功耗有多低呢?在2016年的ISSCC上,来自初创公司PsiKick发表的支持BLE网络的唤醒式接收机在做无线通讯时仅需要400 nW的功耗,而到了2017年ISSCC,加州大学圣地亚哥分校发表的唤醒式接收机更是把功耗做到了4.5 nW,比起传统需要毫瓦级的IoT芯片小了4-6个数量级!来自UCSD的4.5 nW超低功耗唤醒式接收机反射调制系统唤醒式接收机主要解决了无线链路中如何低功耗接收信号的问题,但是在如果使用传统的发射机,则还是需要主动发射射频信号。发射机也是非常费电的,发射信号时所需的功耗常常要达到毫瓦数量级。那么,有没有可能在发射机处也做一些创新,降低功耗呢?确实已经有人另辟蹊径,想到了不发射射频信号也能把IoT节点传感器的信息传输出去的办法,就是由华盛顿大学研究人员提出的使用发射调制。反射调制有点像在航海和野外探险中的日光信号镜,日光信号镜通过不同角度的反射太阳光来传递信息。在这里,信号的载体是太阳光,但是太阳光能量并非传递信号的人发射的,而是作为第三方的太阳提供的。类似的,华盛顿大学研究人员提出的办法也是这样:中心节点发射射频信号,IoT节点则传感器的输出来改变(调制)天线的发射系数,这样中心节点通过检测反射信号就可以接收IoT节点的信号。在整个过程中IoT节点并没有发射射频信号,而是反射中心节点发出的射频信号,这样就实现了超低功耗。华盛顿大学的Shyam Gollakota教授率领的研究组在反射调制实现的超低功耗IoT领域目前已经完成了三个相关项目。去年,他们完成了passive WiFi和interscatter项目。Passive WiFi用于长距离反射通信,使用WiFi路由器发射功率相对较高的射频信号,而IoT节点则调制天线反射系数来传递信息。多个IoT节点可以共存,并使用类似CDMA扩频的方式来同时发射信息。interscatter则用于短距离数据传输,使用移动设备发射功率较低的射频信号,而IoT节点则调制该射频信号的反射来实现信息传输的目的。Passive WiFi和interscatter芯片的功耗都在10-20微瓦附近,比起动辄毫瓦级别的传统IoT无线芯片小了几个数量级,同时也为物联网节点进入人体内等应用场景铺平了道路。Passive WiFi(上)与Interscatter(下)使用反射调制,分别针对长距离与短距离应用。Passive WiFi和Interscatter还需要使用电信号因此需要供电,而Gollakota教授最近发表的Printed WiFi则是更进一步,完全不需要供电了!在物联网的应用中,许多需要检测的物理量其实不是电信号,例如速度,液体流量等等。这些物理量虽然不是电物理量,但是由于目前主流的信号处理和传输都是使用电子系统,因此传统的做法还是使用传感器电子芯片把这些物理量转化为电信号,之后再用无线连接传输出去。其实,这一步转化过程并非必要,而且会引入额外的能量消耗。Printed WiFi的创新之处就是使用机械系统去调制天线的反射系数,从而通过反射调制把这些物理量传输出去。这样,在IoT节点就完全避免了电子系统,从而真正实现无电池工作!目前,这些机械系统使用3D打印的方式制作,这也是该项目取名Printed WiFi的原因。上图是Printed WiFi的一个例子,即转速传感器。弹簧、齿轮等机械器件在上方测速仪旋转时会周期性地闭合/打开最下方天线(slot antenna)中的开关,从而周期性地(周期即旋转速度)改变最下方天线的反射特性,这样中心节点只要通过反射射频信号就能读出旋转速度。最下方的图是该传感器在不同转速时的反射信号在时间域的变化情况,可见通过反射信号可以把转速信息提取出来。超低功耗传感器物联网节点最基本的目标就是提供传感功能,因此超低功耗传感器也是必不可少。目前,温度、光照传感器在经过深度优化后已经可以实现nW-uW数量级的功耗,而在智能音响中得到广泛应用的声音传感器则往往要消耗mW数量级甚至更高的功耗,因此成为了下一步突破研发的重点。在声音传感器领域,最近的突破来自于压电MEMS(一个典型代表是脱胎于密歇根大学的初创公司Vesper)。传统的声音传感器(即麦克风)必须把整个系统(包括后端ADC和DSP)一直处于活动待机状态,以避免错过任何有用的声音信号,因此平均功耗在接近mW这样的数量级。然而,在不少环境下,这样的系统其实造成了能量的浪费,因为大多数时候环境里可能并没有声音,造成了ADC、DSP等模组能量的浪费。而使用压电MEMS可以避免这样的问题:当没有声音信号时,压电MEMS系统处于休眠状态,仅仅前端压电MEMS麦克风在待命,而后端的ADC、DSP都处于休眠状态,整体功耗在uW数量级。而一旦有用声音信号出现并被压电MEMS检测到,则压电MEMS麦克风可以输出唤醒信号将后面的ADC和DSP唤醒,从而不错过有用信号。因此,整体声音传感器的平均功耗可以在常规的应用场景下可以控制在uW数量级,从而使声音传感器可以进入更多应用场景。超低功耗MCU物联网节点里的最后一个关键模组是MCU。MCU作为控制整个物联网节点的核心模组,其功耗也往往不可忽视。如何减小MCU的功耗?MCU功耗一般分为静态漏电和动态功耗两部分。在静态漏电部分,为了减小漏电,可以做的是减小电源电压,以及使用低漏电的标准单元设计。在动态功耗部分,我们可以减小电源电压或者降低时钟频率来降低功耗。由此可见,降低电源电压可以同时降低静态漏电和动态功耗,因此能将电源电压降低的亚阈值电路设计就成了超低功耗MCU设计的必由之路。举例来说,将电源电压由1.2V降低到0.5V可以将动态功耗降低接近6倍,而静态漏电更是指数级下降。当然,亚阈值电路设计会涉及一些设计流程方面的挑战,例如如何确定亚阈值门电路的延迟,建立/保持时间等都需要仔细仿真和优化。在学术界,弗吉尼亚大学的研究组发布了动态功耗低至500nW的传感器SoC,其中除了MCU之外还包括了计算加速器和无线基带。在已经商业化的技术方面,初创公司Ambiq的Apollo系列MCU可以实现35uA/MHz的超低功耗,其设计使用了Ambiq拥有多年积累的SPOT亚阈值设计技术。在未来,我们可望可以看到功耗低至nW数量级的MCU,从而为使用能量获取技术的物联网节点铺平道路。结语随着物联网的发展,目前第一代广域物联网已经快速铺开走进了千家万户。然而,广域物联网节点由于必须满足覆盖需求,因此射频功耗很难做小,从而限制了应用场景(例如人体内传感器等无法使用大容量电池的场景)。局域物联网将会成为物联网发展的下一步,本文介绍的能量获取技术配合超低功耗无线通信、MCU和传感器可望让物联网节点突破传统的限制,在尺寸和电池寿命方面都得到革命性的突破,从而为物联网进入可植入式传感器等新应用铺平道路。来自微信

IoT的核心:盘点下一代超低功耗节点黑科技 李飞的说2018年08月27日08:09随着物联网的逐渐铺开,人们已经在生活中看到了越来越多的物联网模块:智能水表,共享单车,等等。目前的物联网仍然主要由运营商推动,物联网模块需要使用标准蜂窝协议与基站通讯。由于基站需要覆盖尽可能大的面积,因此物联网模块需要能做到在距离基站很远时仍能通讯,这就对于物联网模块的射频发射功率有了很高的要求;从另一个角度来说,物联网模块在做无线通讯时仍然需要消耗高达30mA的电流,这使得目前的物联网模组仍然需要配合较高容量的电池(如五号电池)才能工作,这也导致了物联网模组的尺寸很难做小。为了能进一步普及物联网,必须克服这个功耗以及尺寸的限制。例如,如果未来要把物联网做到植入人体内,则不可能再搭配五号电池,而必须使用更小的电池甚至使用能量获取系统从环境中获取能量彻底摆脱电池的限制。为了实现这个目标,从通讯协议上说,可以使用更低功耗的自组网技术,类似BLE;而从电路实现上,则必须使用创新电路来降低功耗。能量获取技术根据之前的讨论,目前电池的尺寸和成本都已经成为了限制IoT设备近一步进入潜在市场的瓶颈。那么,有没有可能使用从环境中获得能量来支持物联网节点工作呢?这种从环境中获取能量来支持物联网节点工作的模块叫做“能量获取”(energy harvesting),目前能量获取电路芯片的研究已经成为了研究领域的热门方向。目前最成熟的能量获取系统可以说是太阳能电池。传统太阳能电池能提供较好的能量获取效率,但是付出的代价是难以集成到CMOS芯片上。最近,不少研究机构都在使用新型CMOS太阳能电池,从而可以和物联网节点的其他模块集成到同一块芯片上,大大增加了集成度并减小模组尺寸。当然,集成在CMOS芯片上的太阳能电池需要付出低能量输出的代价,目前常见的CMOS片上太阳能电池在室内灯光下能提供nW等级的功率输出,而在强光下能提供uW级别的功率输出,这就对物联网模组的整体功耗优化提出了很高的要求。另一方面,也可以将能量获取与小尺寸微型电池配合使用,当光照较好时使用太阳能电池而在光照较弱时使用备用电池,从而提升整体物联网模组的电池寿命。除了太阳能电池外,另一个广为人知的环境能量就是WiFi信号。今年ISSCC上,来自俄勒冈州立大学的研究组发表了从环境中的WiFi信号获取能量的芯片。先来点背景知识:WiFi的最大发射功率是30dBm(即1W),在简单的环境里(即没有遮挡等)信号功率随着与发射设备的距离平方衰减,在距离3m左右的距离信号功率就衰减到了1uW(-30dBm)左右,而如果有物体遮挡则会导致功率更小。俄勒冈州立大学发表的论文中,芯片配合直径为1.5cm的天线可以在非常低的无线信号功率(-33dBm即500nW)下也能工作给电池充电,能量获取效率在5-10%左右(即在距离发射源3m的情况下输出功率在50nW左右)。因此,WiFi信号也可以用来给物联网模组提供能量,但是其输出功率在现实的距离上也不大,同样也需要节点模组对于功耗做深度优化。另外,机械能也可以作为物联网节点的能量获取来源。压电效应可以把机械能转换为电能,从而使用压电材料(例如压电MEMS)就能为物联网节点充电。使用压电材料做能量源的典型应用包括各种智能城市和工业应用,例如当有车压过减速带的时候,减速带下的物联网传感器上的压电材料可以利用车辆压力的机械能给传感器充电并唤醒传感器,从而实现车辆数量统计等。这样,机械压力即可以作为需要测量的信号,其本身又可以作为能量源,所以在没有信号的时候就无需浪费能量了!压电材料的输出功率随着机械能的大小不同会有很大的区别,一般在nW-mW的数量级范围。唤醒式无线系统传统的IoT无线收发系统使用的往往是周期性通讯或主动事件驱动通讯的方案。周期性通讯指的是IoT节点定期打开与中心节点通讯,并在其他时间休眠;事件驱动通讯则是指IoT节点仅仅在传感器监测到特定事件时才与中心节点通讯,而其它时候都休眠。在这两种模式中,都需要IoT节点主动与中心节点建立连接并通讯。然而,这个建立连接的过程是非常消耗能量的。因此,唤醒式无线系统的概念就应运而生。什么是唤醒式无线系统?就是该该系统在大多数时候都是休眠的,仅仅当主节点发射特定信号时才会唤醒无线系统。换句话说,连接的建立这个耗费能量的过程并不由IoT节点来完成,而是由中心节点通过发送唤醒信号来完成。当建立连接的事件由中心节点来驱动时,一切都变得简单。首先,中心节点可以发射一段射频信号,而IoT节点可以通过能量获取(energy harvesting)电路从该射频信号中获取能量为内部电容充电。当IoT节点的电容充电完毕后,无线连接系统就可以使用电容里的能量来发射射频信号与中心节点通讯。这样一来,就可以做到无电池操作。想象一下,如果不是使用唤醒式无线系统,而是使用IoT主动连接的话,无电池就会变得困难,因为无法保证IoT节点在需要通讯的时候在节点内有足够的能量。反之,现在使用唤醒式系统,中心节点在需要IoT节点工作时首先为其充电唤醒,就能保证每次IoT节点都有足够能量通讯。那么,这样的唤醒式无线系统功耗有多低呢?在2016年的ISSCC上,来自初创公司PsiKick发表的支持BLE网络的唤醒式接收机在做无线通讯时仅需要400 nW的功耗,而到了2017年ISSCC,加州大学圣地亚哥分校发表的唤醒式接收机更是把功耗做到了4.5 nW,比起传统需要毫瓦级的IoT芯片小了4-6个数量级!来自UCSD的4.5 nW超低功耗唤醒式接收机反射调制系统唤醒式接收机主要解决了无线链路中如何低功耗接收信号的问题,但是在如果使用传统的发射机,则还是需要主动发射射频信号。发射机也是非常费电的,发射信号时所需的功耗常常要达到毫瓦数量级。那么,有没有可能在发射机处也做一些创新,降低功耗呢?确实已经有人另辟蹊径,想到了不发射射频信号也能把IoT节点传感器的信息传输出去的办法,就是由华盛顿大学研究人员提出的使用发射调制。反射调制有点像在航海和野外探险中的日光信号镜,日光信号镜通过不同角度的反射太阳光来传递信息。在这里,信号的载体是太阳光,但是太阳光能量并非传递信号的人发射的,而是作为第三方的太阳提供的。类似的,华盛顿大学研究人员提出的办法也是这样:中心节点发射射频信号,IoT节点则传感器的输出来改变(调制)天线的发射系数,这样中心节点通过检测反射信号就可以接收IoT节点的信号。在整个过程中IoT节点并没有发射射频信号,而是反射中心节点发出的射频信号,这样就实现了超低功耗。华盛顿大学的Shyam Gollakota教授率领的研究组在反射调制实现的超低功耗IoT领域目前已经完成了三个相关项目。去年,他们完成了passive WiFi和interscatter项目。Passive WiFi用于长距离反射通信,使用WiFi路由器发射功率相对较高的射频信号,而IoT节点则调制天线反射系数来传递信息。多个IoT节点可以共存,并使用类似CDMA扩频的方式来同时发射信息。interscatter则用于短距离数据传输,使用移动设备发射功率较低的射频信号,而IoT节点则调制该射频信号的反射来实现信息传输的目的。Passive WiFi和interscatter芯片的功耗都在10-20微瓦附近,比起动辄毫瓦级别的传统IoT无线芯片小了几个数量级,同时也为物联网节点进入人体内等应用场景铺平了道路。Passive WiFi(上)与Interscatter(下)使用反射调制,分别针对长距离与短距离应用。Passive WiFi和Interscatter还需要使用电信号因此需要供电,而Gollakota教授最近发表的Printed WiFi则是更进一步,完全不需要供电了!在物联网的应用中,许多需要检测的物理量其实不是电信号,例如速度,液体流量等等。这些物理量虽然不是电物理量,但是由于目前主流的信号处理和传输都是使用电子系统,因此传统的做法还是使用传感器电子芯片把这些物理量转化为电信号,之后再用无线连接传输出去。其实,这一步转化过程并非必要,而且会引入额外的能量消耗。Printed WiFi的创新之处就是使用机械系统去调制天线的反射系数,从而通过反射调制把这些物理量传输出去。这样,在IoT节点就完全避免了电子系统,从而真正实现无电池工作!目前,这些机械系统使用3D打印的方式制作,这也是该项目取名Printed WiFi的原因。上图是Printed WiFi的一个例子,即转速传感器。弹簧、齿轮等机械器件在上方测速仪旋转时会周期性地闭合/打开最下方天线(slot antenna)中的开关,从而周期性地(周期即旋转速度)改变最下方天线的反射特性,这样中心节点只要通过反射射频信号就能读出旋转速度。最下方的图是该传感器在不同转速时的反射信号在时间域的变化情况,可见通过反射信号可以把转速信息提取出来。超低功耗传感器物联网节点最基本的目标就是提供传感功能,因此超低功耗传感器也是必不可少。目前,温度、光照传感器在经过深度优化后已经可以实现nW-uW数量级的功耗,而在智能音响中得到广泛应用的声音传感器则往往要消耗mW数量级甚至更高的功耗,因此成为了下一步突破研发的重点。在声音传感器领域,最近的突破来自于压电MEMS(一个典型代表是脱胎于密歇根大学的初创公司Vesper)。传统的声音传感器(即麦克风)必须把整个系统(包括后端ADC和DSP)一直处于活动待机状态,以避免错过任何有用的声音信号,因此平均功耗在接近mW这样的数量级。然而,在不少环境下,这样的系统其实造成了能量的浪费,因为大多数时候环境里可能并没有声音,造成了ADC、DSP等模组能量的浪费。而使用压电MEMS可以避免这样的问题:当没有声音信号时,压电MEMS系统处于休眠状态,仅仅前端压电MEMS麦克风在待命,而后端的ADC、DSP都处于休眠状态,整体功耗在uW数量级。而一旦有用声音信号出现并被压电MEMS检测到,则压电MEMS麦克风可以输出唤醒信号将后面的ADC和DSP唤醒,从而不错过有用信号。因此,整体声音传感器的平均功耗可以在常规的应用场景下可以控制在uW数量级,从而使声音传感器可以进入更多应用场景。超低功耗MCU物联网节点里的最后一个关键模组是MCU。MCU作为控制整个物联网节点的核心模组,其功耗也往往不可忽视。如何减小MCU的功耗?MCU功耗一般分为静态漏电和动态功耗两部分。在静态漏电部分,为了减小漏电,可以做的是减小电源电压,以及使用低漏电的标准单元设计。在动态功耗部分,我们可以减小电源电压或者降低时钟频率来降低功耗。由此可见,降低电源电压可以同时降低静态漏电和动态功耗,因此能将电源电压降低的亚阈值电路设计就成了超低功耗MCU设计的必由之路。举例来说,将电源电压由1.2V降低到0.5V可以将动态功耗降低接近6倍,而静态漏电更是指数级下降。当然,亚阈值电路设计会涉及一些设计流程方面的挑战,例如如何确定亚阈值门电路的延迟,建立/保持时间等都需要仔细仿真和优化。在学术界,弗吉尼亚大学的研究组发布了动态功耗低至500nW的传感器SoC,其中除了MCU之外还包括了计算加速器和无线基带。在已经商业化的技术方面,初创公司Ambiq的Apollo系列MCU可以实现35uA/MHz的超低功耗,其设计使用了Ambiq拥有多年积累的SPOT亚阈值设计技术。在未来,我们可望可以看到功耗低至nW数量级的MCU,从而为使用能量获取技术的物联网节点铺平道路。结语随着物联网的发展,目前第一代广域物联网已经快速铺开走进了千家万户。然而,广域物联网节点由于必须满足覆盖需求,因此射频功耗很难做小,从而限制了应用场景(例如人体内传感器等无法使用大容量电池的场景)。局域物联网将会成为物联网发展的下一步,本文介绍的能量获取技术配合超低功耗无线通信、MCU和传感器可望让物联网节点突破传统的限制,在尺寸和电池寿命方面都得到革命性的突破,从而为物联网进入可植入式传感器等新应用铺平道路。来自微信 -

超逼真20张动图,秒懂四大电镜原理(SEM, TEM, AFM, STM)! 材料的显微分析能获得材料的组织结构,揭示材料基本性质和基本规律,在材料测试技术中占重要的一环。对各种显微分析设备诸如SEM、TEM、AFM、STM等,各位材料届的小伙伴一定不会陌生。最近小编发现一些电镜动画,被惊艳到,原来枯燥无味的电镜可以变得这么生动,闲言少叙,下面就和大家一起来分享。扫描电子显微镜(SEM)扫描电镜成像是利用细聚焦高能电子束在样件表面激发各种物理信号,如二次电子、背散射电子等,通过相应的检测器来检测这些信号,信号的强度与样品表面形貌有一定的对应关系,因此,可将其转换为视频信号来调制显像管的亮度得到样品表面形貌的图像。SEM工作图入射电子与样品中原子的价电子发生非弹性散射作用而损失的那部分能量(30~50eV)激发核外电子脱离原子,能量大于材料逸出功的价电子从样品表面逸出成为真空中的自由电子,此即二次电子。电子发射图二次电子探测图二次电子试样表面状态非常敏感,能有效显示试样表面的微观形貌,分辨率可达5~10nm。二次电子扫描成像入射电子达到离核很近的地方被反射,没有能量损失;既包括与原子核作用而形成的弹性背散射电子,又包括与样品核外电子作用而形成的非弹性背散射电子。背散射电子探测图用背反射信号进行形貌分析时,其分辨率远比二次电子低。可根据背散射电子像的亮暗程度,判别出相应区域的原子序数的相对大小,由此可对金属及其合金的显微组织进行成分分析。EBSD成像过程透射电子显微镜(TEM)透射电镜是把经加速和聚焦的电子束投射到非常薄的样件上,电子与样品中的原子碰撞,而改变方向,从而产生立体角散射。散射角的大小与样品的密度、厚度相关,因此,可以形成明暗不同的影像,影像将在放大、聚焦后在成像器件上显示出来。TEM工作图TEM成像过程STEM成像不同于平行电子束的TEM,它是利用聚集的电子束在样品上扫描来完成的,与SEM不同之处在于探测器置于试样下方,探测器接收透射电子束流或弹性散射电子束流,经放大后在荧光屏上显示出明场像和暗场像。STEM分析图入射电子束照射试样表面发生弹性散射,一部分电子所损失能量值是样品中某个元素的特征值,由此获得能量损失谱(EELS),利用EELS可以对薄试样微区元素组成、化学键及电子结构等进行分析。EELS原理图*本文来源于新材料在线®,内容仅为全部的1/2。完整版内容可下载最新版本新材料在线®APP查看2018-07-02来自微信

超逼真20张动图,秒懂四大电镜原理(SEM, TEM, AFM, STM)! 材料的显微分析能获得材料的组织结构,揭示材料基本性质和基本规律,在材料测试技术中占重要的一环。对各种显微分析设备诸如SEM、TEM、AFM、STM等,各位材料届的小伙伴一定不会陌生。最近小编发现一些电镜动画,被惊艳到,原来枯燥无味的电镜可以变得这么生动,闲言少叙,下面就和大家一起来分享。扫描电子显微镜(SEM)扫描电镜成像是利用细聚焦高能电子束在样件表面激发各种物理信号,如二次电子、背散射电子等,通过相应的检测器来检测这些信号,信号的强度与样品表面形貌有一定的对应关系,因此,可将其转换为视频信号来调制显像管的亮度得到样品表面形貌的图像。SEM工作图入射电子与样品中原子的价电子发生非弹性散射作用而损失的那部分能量(30~50eV)激发核外电子脱离原子,能量大于材料逸出功的价电子从样品表面逸出成为真空中的自由电子,此即二次电子。电子发射图二次电子探测图二次电子试样表面状态非常敏感,能有效显示试样表面的微观形貌,分辨率可达5~10nm。二次电子扫描成像入射电子达到离核很近的地方被反射,没有能量损失;既包括与原子核作用而形成的弹性背散射电子,又包括与样品核外电子作用而形成的非弹性背散射电子。背散射电子探测图用背反射信号进行形貌分析时,其分辨率远比二次电子低。可根据背散射电子像的亮暗程度,判别出相应区域的原子序数的相对大小,由此可对金属及其合金的显微组织进行成分分析。EBSD成像过程透射电子显微镜(TEM)透射电镜是把经加速和聚焦的电子束投射到非常薄的样件上,电子与样品中的原子碰撞,而改变方向,从而产生立体角散射。散射角的大小与样品的密度、厚度相关,因此,可以形成明暗不同的影像,影像将在放大、聚焦后在成像器件上显示出来。TEM工作图TEM成像过程STEM成像不同于平行电子束的TEM,它是利用聚集的电子束在样品上扫描来完成的,与SEM不同之处在于探测器置于试样下方,探测器接收透射电子束流或弹性散射电子束流,经放大后在荧光屏上显示出明场像和暗场像。STEM分析图入射电子束照射试样表面发生弹性散射,一部分电子所损失能量值是样品中某个元素的特征值,由此获得能量损失谱(EELS),利用EELS可以对薄试样微区元素组成、化学键及电子结构等进行分析。EELS原理图*本文来源于新材料在线®,内容仅为全部的1/2。完整版内容可下载最新版本新材料在线®APP查看2018-07-02来自微信 -

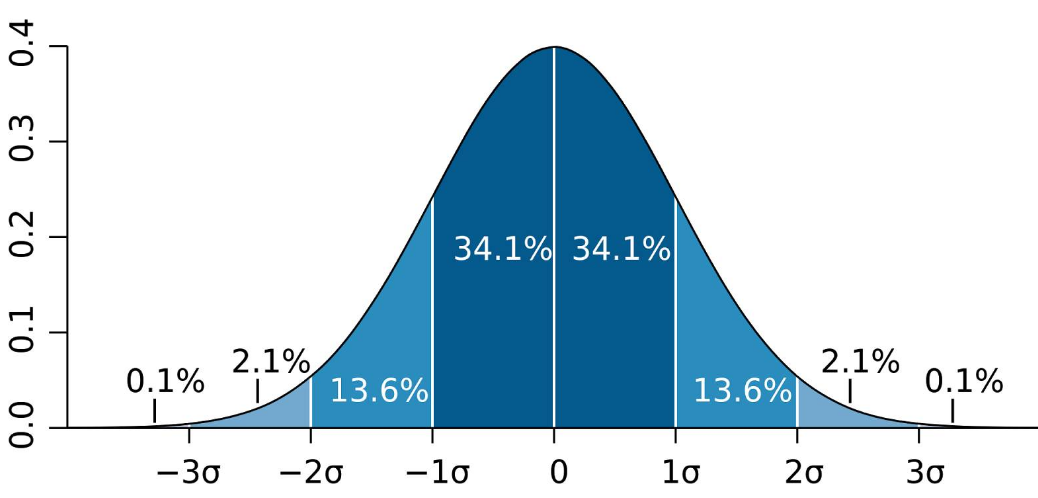

一份数学小白也能读懂的「马尔可夫链蒙特卡洛方法」入门指南 机器之心2017年12月24日12:46作者:Ben Shaver机器之心编译参与:黄小天、刘晓坤在众多经典的贝叶斯方法中,马尔可夫链蒙特卡洛(MCMC)由于包含大量数学知识,且计算量很大,而显得格外特别。本文反其道而行之,试图通过通俗易懂且不包含数学语言的方法,帮助读者对 MCMC 有一个直观的理解,使得毫无数学基础的人搞明白 MCMC。在我们中的很多人看来,贝叶斯统计学家不是巫术师,就是完全主观的胡说八道者。在贝叶斯经典方法中,马尔可夫链蒙特卡洛(Markov chain Monte Carlo/MCMC)尤其神秘,其中数学很多,计算量很大,但其背后原理与数据科学有诸多相似之处,并可阐释清楚,使得毫无数学基础的人搞明白 MCMC。这正是本文的目标。那么,到底什么是 MCMC 方法?一言以蔽之:MCMC 通过在概率空间中随机采样以近似兴趣参数(parameter of interest)的后验分布。我将在本文中做出简短明了的解释,并且不借助任何数学知识。首先,解释重要的术语。「兴趣参数」(parameter of interest)可以总结我们感兴趣现象的一些数字。我们通常使用统计学评估参数,比如,如果想要了解成年人的身高,我们的兴趣参数可以是精确到英寸的平均身高。「分布」是参数的每个可能值、以及我们有多大可能观察每个参数的数学表征,其最著名的实例是钟形曲线:在贝叶斯统计学中,分布还有另外一种解释。贝叶斯不是仅仅表征一个参数值以及每个参数有多大可能是真值,而是把分布看作是我们对参数的「信念」。因此,钟形曲线表明我们非常确定参数值相当接近于零,但是我们认为在一定程度上真值高于或低于该值的可能性是相等的。事实上,人的身高确实遵从一个正态曲线,因此我们假定平均身高的真值符合钟形曲线,如下所示:很明显,上图表征是巨人的身高分布,因为据图可知,最有可能的平均身高是 6'2"(但他们也并非超级自信)。让我们假设其中某个人后来收集到一些数据,并且观察了身高在 5"和 6"之间的一些人。我们可以用另一条正态曲线表征下面的数据,该曲线表明了哪些平均身高值能最好地解释这些数据:在贝叶斯统计中,表征我们对参数信念的分布被称为「先验分布」,因为它在我们看到任何数据之前捕捉到了我们的信念。「可能性分布」(likelihood distribution)通过表征一系列参数值以及伴随的每个参数值解释观察数据的可能性,以总结数据之中的信息。评估最大化可能性分布的参数值只是回答这一问题:什么参数值会使我们更可能观察到已经观察过的数据?如果没有先验信念,我们可能无法对此作出评估。但是,贝叶斯分析的关键是结合先验与可能性分布以确定后验分布。它可以告诉我们哪个参数值最大化了观察到已观察过的特定数据的概率,并把先验信念考虑在内。在我们的实例中,后验分布如下所示:如上所示,红线表征后验分布。你可以将其看作先验和可能性分布的一种平均值。由于先验分布较小且更加分散,它表征了一组关于平均身高真值的「不太确定」的信念。同时,可能性分布在相对较窄的范围内总结数据,因此它表征了对真参数值的「更确定」的猜测。当先验与可能性分布结合在一起,数据(由可能性分布表征)主导了假定存在于这些巨人之中的个体的先验弱信念。尽管该个体依然认为平均身高比数据告诉他的稍高一些,但是他非常可能被数据说服。在两条钟形曲线的情况下,求解后验分布非常容易。有一个结合了两者的简单等式。但是如果我们的先验和可能性分布表现很差呢?有时使用非简化的形状建模数据或先验信念时是最精确的。如果可能性分布需要带有两个峰值的分布才能得到最好地表征呢?并且出于某些原因我们想要解释一些非常奇怪的先验分布?通过手动绘制一个丑陋的先验分布,我已可视化了该情景,如下所示:可视化由 Matplotlib 渲染,并使用 MS Paint 做了改善如前所述,存在一些后验分布,它给出了每个参数值的可能性分布。但是很难得到完整的分布,也无法解析地求解。这就是使用 MCMC 方法的时候了。MCMC 允许我们在无法直接计算的情况下评估后验分布的形状。为了理解其工作原理,我将首先介绍蒙特卡洛模拟(Monte Carlo simulation),接着讨论马尔可夫链。蒙特卡洛模拟只是一种通过不断地生成随机数来评估固定参数的方法。通过生成随机数并对其做一些计算,蒙特卡洛模拟给出了一个参数的近似值(其中直接计算是不可能的或者计算量过大)。假设我们想评估下图中的圆圈面积:由于圆在边长为 10 英寸的正方形之内,所以通过简单计算可知其面积为 78.5 平方英寸。但是,如果我们随机地在正方形之内放置 20 个点,接着我们计算点落在圆内的比例,并乘以正方形的面积,所得结果非常近似于圆圈面积。由于 15 个点落在了圆内,那么圆的面积可以近似地为 75 平方英寸,对于只有 20 个随机点的蒙特卡洛模拟来说,结果并不差。现在,假设我们想要计算下图中由蝙蝠侠方程(Batman Equation)绘制的图形的面积:我们从来没有学过一个方程可以求这样的面积。不管怎样,通过随机地放入随机点,蒙特卡洛模拟可以相当容易地为该面积提供一个近似值。蒙特卡洛模拟不只用于估算复杂形状的面积。通过生成大量随机数字,它还可用于建模非常复杂的过程。实际上,蒙特卡洛模拟还可以预测天气,或者评估选举获胜的概率。理解 MCMC 方法的第二个要素是马尔科夫链(Markov chains)。马尔科夫链由存在概率相关性的事件的序列构成。每个事件源于一个结果集合,根据一个固定的概率集合,每个结果决定了下一个将出现的结果。马尔科夫链的一个重要特征是「无记忆性」:可能需要用于预测下一个时间的一切都已经包含在当前的状态中,从事件的历史中得不到任何新信息。例如 Chutes and Ladders 这个游戏就展示了这种无记忆性,或者说马尔科夫性,但在现实世界中很少事物是这种性质的。尽管如此,马尔科夫链也是理解现实世界的强大工具。在十九世纪,人们观察到钟形曲线在自然中是一种很常见的模式。(我们注意到,例如,人类的身高服从钟形曲线分布。)Galton Boards 曾通过将弹珠坠落并通过布满木钉的板模拟了重复随机事件的平均值,在弹珠的最终数量分布中重现了钟形曲线:俄罗斯数学家和神学家 Pavel Nekrasov 认为钟形曲线,或者更一般的说,大数规律只不过是小孩子的游戏和普通的谜题中的伪假象,其中每个事件之间都是完全独立的。他认为现实世界中的互相依赖的事件,例如人类行为,并不遵循漂亮的数学模式或分布。Andrey Markov(马尔科夫链正是以他的名字命名)试图证明非独立的事件可能也遵循特定的模式。他的其中一个最著名的例子是从一份俄罗斯诗歌作品中数出几千个两字符对(two-character pairs)。他使用这些两字符对计算了每个字符的条件概率。即,给定一个确定的上述字母或空白,关于下一个字母将是 A、T 或者空白等,存在一个确定的概率。通过这些概率,Markov 可以模拟一个任意的长字符序列。这就是马尔科夫链。虽然早先的几个字符很大程度上依赖于初始字符的选择,Markov 表明在长字符序列中,字符的分布会出现特定的模式。因此,即使是互相依赖的事件,如果服从固定的概率分布,将遵循平均水平的模式。举一个更有意义的例子,假设你住在一个有 5 个房间的房子里,里面有一个卧室、浴室、客厅、厨房、饭厅。然后我们收集一些数据,假定只需要当前你所处的房间和相应的时间就可以预测下一个你所处的房间的概率。例如,如果你在厨房,你有 30% 的概率会留在厨房,有 30% 的概率会走到饭厅,有 20% 的概率会走到客厅,有 10% 的概率会走到浴室,以及有 10% 的概率会走到卧室。使用每个房间的概率集合,我们可以构建一个关于你接下来要去的房间的预测链。如果想预测一个人处于厨房之后所在的房间,基于几个状态而做出预测可能有效。但由于我们的预测仅仅基于一个人在房子中的单次观察,可以合理地认为预测结果是不够好的。例如,如果一个人从卧室走到浴室,相比从厨房走到浴室的情况,他更可能会返回原来的房间。因此,马尔科夫链并不真正适用于现实世界。然而,通过迭代运行马尔科夫链数千次,确实能给出关于你接下来可能所处的房间的长期预测。更重要的是,这个预测并不受这个人起始所处的房间的影响。对此可以直观地理解为:在模拟和描述长期过程(或普遍情况)一个人所处房间的概率时,时间因素是不重要的。因此,如果我们理解了控制行为的概率,就可以使用马尔科夫链计算变化的长期趋势。希望通过介绍一些蒙特卡洛模拟和马尔科夫链,可以使你对 MCMC 方法的零数学解释有更直观的理解。回到原来的问题,即评估平均身高的后验分布:这个平均身高的后验分布的实例没有基于真实数据。我们知道后验分布在某种程度上处于先验分布和可能性分布的范围内,但无论如何都无法直接计算。使用 MCMC 方法,我们可以有效地从后验分布中提取样本,然后计算统计特征,例如提取样本的平均值。首先,MCMC 方法选择一个随机参数值。模拟过程中会持续生成随机的值(即蒙特卡洛部分),但服从某些能生成更好参数值的规则。即对于一对参数值,可以通过给定先验信度计算每个值解释数据的有效性,从而确定哪个值更好。我们会将更好的参数值以及由这个值的解释数据有效性决定的特定概率添加到参数值的链中(即马尔科夫链部分)。为了可视化地解释上述过程,首先强调一下,一个分布的特定值的高度代表的是观察到该值的概率。因此,参数值(x 轴)对应的概率(y 轴)可能或高或低。对于单个参数,MCMC 方法会从随机在 x 轴上采样开始。红点表征随机参数采样。由于随机采样服从固定的概率,它们倾向于经过一段时间后收敛于参数的高概率区域:蓝点表示当采样收敛之后,经过任意时间的随机采样。注意:垂直堆叠这些点仅仅是为了说明目的。收敛出现之后,MCMC 采样会得到作为后验分布样本的一系列点。用这些点画直方图,然后你可以计算任何感兴趣的统计特征:通过 MCMC 模拟生成的样本集合计算的任何统计特征,都是对真实后验分布的统计特征的最佳近似。MCMC 方法也可以用于评估多于一个参数的后验分布(例如,人类身高和体重)。对于 n 个参数,在 n 维空间中存在高概率的区域,其中特定的参数值集合可以更有效地解释数据。因此,我认为 MCMC 方法的本质,就是在一个概率空间中进行随机采样以近似后验分布。原文链接:https://towardsdatascience.com/a-zero-math-introduction-to-markov-chain-monte-carlo-methods-dcba889e0c50机器之心推出「Synced Machine Intelligence Awards」2017,希望通过四大奖项记录这一年人工智能的发展与进步,传递行业启示性价值。来自微信

一份数学小白也能读懂的「马尔可夫链蒙特卡洛方法」入门指南 机器之心2017年12月24日12:46作者:Ben Shaver机器之心编译参与:黄小天、刘晓坤在众多经典的贝叶斯方法中,马尔可夫链蒙特卡洛(MCMC)由于包含大量数学知识,且计算量很大,而显得格外特别。本文反其道而行之,试图通过通俗易懂且不包含数学语言的方法,帮助读者对 MCMC 有一个直观的理解,使得毫无数学基础的人搞明白 MCMC。在我们中的很多人看来,贝叶斯统计学家不是巫术师,就是完全主观的胡说八道者。在贝叶斯经典方法中,马尔可夫链蒙特卡洛(Markov chain Monte Carlo/MCMC)尤其神秘,其中数学很多,计算量很大,但其背后原理与数据科学有诸多相似之处,并可阐释清楚,使得毫无数学基础的人搞明白 MCMC。这正是本文的目标。那么,到底什么是 MCMC 方法?一言以蔽之:MCMC 通过在概率空间中随机采样以近似兴趣参数(parameter of interest)的后验分布。我将在本文中做出简短明了的解释,并且不借助任何数学知识。首先,解释重要的术语。「兴趣参数」(parameter of interest)可以总结我们感兴趣现象的一些数字。我们通常使用统计学评估参数,比如,如果想要了解成年人的身高,我们的兴趣参数可以是精确到英寸的平均身高。「分布」是参数的每个可能值、以及我们有多大可能观察每个参数的数学表征,其最著名的实例是钟形曲线:在贝叶斯统计学中,分布还有另外一种解释。贝叶斯不是仅仅表征一个参数值以及每个参数有多大可能是真值,而是把分布看作是我们对参数的「信念」。因此,钟形曲线表明我们非常确定参数值相当接近于零,但是我们认为在一定程度上真值高于或低于该值的可能性是相等的。事实上,人的身高确实遵从一个正态曲线,因此我们假定平均身高的真值符合钟形曲线,如下所示:很明显,上图表征是巨人的身高分布,因为据图可知,最有可能的平均身高是 6'2"(但他们也并非超级自信)。让我们假设其中某个人后来收集到一些数据,并且观察了身高在 5"和 6"之间的一些人。我们可以用另一条正态曲线表征下面的数据,该曲线表明了哪些平均身高值能最好地解释这些数据:在贝叶斯统计中,表征我们对参数信念的分布被称为「先验分布」,因为它在我们看到任何数据之前捕捉到了我们的信念。「可能性分布」(likelihood distribution)通过表征一系列参数值以及伴随的每个参数值解释观察数据的可能性,以总结数据之中的信息。评估最大化可能性分布的参数值只是回答这一问题:什么参数值会使我们更可能观察到已经观察过的数据?如果没有先验信念,我们可能无法对此作出评估。但是,贝叶斯分析的关键是结合先验与可能性分布以确定后验分布。它可以告诉我们哪个参数值最大化了观察到已观察过的特定数据的概率,并把先验信念考虑在内。在我们的实例中,后验分布如下所示:如上所示,红线表征后验分布。你可以将其看作先验和可能性分布的一种平均值。由于先验分布较小且更加分散,它表征了一组关于平均身高真值的「不太确定」的信念。同时,可能性分布在相对较窄的范围内总结数据,因此它表征了对真参数值的「更确定」的猜测。当先验与可能性分布结合在一起,数据(由可能性分布表征)主导了假定存在于这些巨人之中的个体的先验弱信念。尽管该个体依然认为平均身高比数据告诉他的稍高一些,但是他非常可能被数据说服。在两条钟形曲线的情况下,求解后验分布非常容易。有一个结合了两者的简单等式。但是如果我们的先验和可能性分布表现很差呢?有时使用非简化的形状建模数据或先验信念时是最精确的。如果可能性分布需要带有两个峰值的分布才能得到最好地表征呢?并且出于某些原因我们想要解释一些非常奇怪的先验分布?通过手动绘制一个丑陋的先验分布,我已可视化了该情景,如下所示:可视化由 Matplotlib 渲染,并使用 MS Paint 做了改善如前所述,存在一些后验分布,它给出了每个参数值的可能性分布。但是很难得到完整的分布,也无法解析地求解。这就是使用 MCMC 方法的时候了。MCMC 允许我们在无法直接计算的情况下评估后验分布的形状。为了理解其工作原理,我将首先介绍蒙特卡洛模拟(Monte Carlo simulation),接着讨论马尔可夫链。蒙特卡洛模拟只是一种通过不断地生成随机数来评估固定参数的方法。通过生成随机数并对其做一些计算,蒙特卡洛模拟给出了一个参数的近似值(其中直接计算是不可能的或者计算量过大)。假设我们想评估下图中的圆圈面积:由于圆在边长为 10 英寸的正方形之内,所以通过简单计算可知其面积为 78.5 平方英寸。但是,如果我们随机地在正方形之内放置 20 个点,接着我们计算点落在圆内的比例,并乘以正方形的面积,所得结果非常近似于圆圈面积。由于 15 个点落在了圆内,那么圆的面积可以近似地为 75 平方英寸,对于只有 20 个随机点的蒙特卡洛模拟来说,结果并不差。现在,假设我们想要计算下图中由蝙蝠侠方程(Batman Equation)绘制的图形的面积:我们从来没有学过一个方程可以求这样的面积。不管怎样,通过随机地放入随机点,蒙特卡洛模拟可以相当容易地为该面积提供一个近似值。蒙特卡洛模拟不只用于估算复杂形状的面积。通过生成大量随机数字,它还可用于建模非常复杂的过程。实际上,蒙特卡洛模拟还可以预测天气,或者评估选举获胜的概率。理解 MCMC 方法的第二个要素是马尔科夫链(Markov chains)。马尔科夫链由存在概率相关性的事件的序列构成。每个事件源于一个结果集合,根据一个固定的概率集合,每个结果决定了下一个将出现的结果。马尔科夫链的一个重要特征是「无记忆性」:可能需要用于预测下一个时间的一切都已经包含在当前的状态中,从事件的历史中得不到任何新信息。例如 Chutes and Ladders 这个游戏就展示了这种无记忆性,或者说马尔科夫性,但在现实世界中很少事物是这种性质的。尽管如此,马尔科夫链也是理解现实世界的强大工具。在十九世纪,人们观察到钟形曲线在自然中是一种很常见的模式。(我们注意到,例如,人类的身高服从钟形曲线分布。)Galton Boards 曾通过将弹珠坠落并通过布满木钉的板模拟了重复随机事件的平均值,在弹珠的最终数量分布中重现了钟形曲线:俄罗斯数学家和神学家 Pavel Nekrasov 认为钟形曲线,或者更一般的说,大数规律只不过是小孩子的游戏和普通的谜题中的伪假象,其中每个事件之间都是完全独立的。他认为现实世界中的互相依赖的事件,例如人类行为,并不遵循漂亮的数学模式或分布。Andrey Markov(马尔科夫链正是以他的名字命名)试图证明非独立的事件可能也遵循特定的模式。他的其中一个最著名的例子是从一份俄罗斯诗歌作品中数出几千个两字符对(two-character pairs)。他使用这些两字符对计算了每个字符的条件概率。即,给定一个确定的上述字母或空白,关于下一个字母将是 A、T 或者空白等,存在一个确定的概率。通过这些概率,Markov 可以模拟一个任意的长字符序列。这就是马尔科夫链。虽然早先的几个字符很大程度上依赖于初始字符的选择,Markov 表明在长字符序列中,字符的分布会出现特定的模式。因此,即使是互相依赖的事件,如果服从固定的概率分布,将遵循平均水平的模式。举一个更有意义的例子,假设你住在一个有 5 个房间的房子里,里面有一个卧室、浴室、客厅、厨房、饭厅。然后我们收集一些数据,假定只需要当前你所处的房间和相应的时间就可以预测下一个你所处的房间的概率。例如,如果你在厨房,你有 30% 的概率会留在厨房,有 30% 的概率会走到饭厅,有 20% 的概率会走到客厅,有 10% 的概率会走到浴室,以及有 10% 的概率会走到卧室。使用每个房间的概率集合,我们可以构建一个关于你接下来要去的房间的预测链。如果想预测一个人处于厨房之后所在的房间,基于几个状态而做出预测可能有效。但由于我们的预测仅仅基于一个人在房子中的单次观察,可以合理地认为预测结果是不够好的。例如,如果一个人从卧室走到浴室,相比从厨房走到浴室的情况,他更可能会返回原来的房间。因此,马尔科夫链并不真正适用于现实世界。然而,通过迭代运行马尔科夫链数千次,确实能给出关于你接下来可能所处的房间的长期预测。更重要的是,这个预测并不受这个人起始所处的房间的影响。对此可以直观地理解为:在模拟和描述长期过程(或普遍情况)一个人所处房间的概率时,时间因素是不重要的。因此,如果我们理解了控制行为的概率,就可以使用马尔科夫链计算变化的长期趋势。希望通过介绍一些蒙特卡洛模拟和马尔科夫链,可以使你对 MCMC 方法的零数学解释有更直观的理解。回到原来的问题,即评估平均身高的后验分布:这个平均身高的后验分布的实例没有基于真实数据。我们知道后验分布在某种程度上处于先验分布和可能性分布的范围内,但无论如何都无法直接计算。使用 MCMC 方法,我们可以有效地从后验分布中提取样本,然后计算统计特征,例如提取样本的平均值。首先,MCMC 方法选择一个随机参数值。模拟过程中会持续生成随机的值(即蒙特卡洛部分),但服从某些能生成更好参数值的规则。即对于一对参数值,可以通过给定先验信度计算每个值解释数据的有效性,从而确定哪个值更好。我们会将更好的参数值以及由这个值的解释数据有效性决定的特定概率添加到参数值的链中(即马尔科夫链部分)。为了可视化地解释上述过程,首先强调一下,一个分布的特定值的高度代表的是观察到该值的概率。因此,参数值(x 轴)对应的概率(y 轴)可能或高或低。对于单个参数,MCMC 方法会从随机在 x 轴上采样开始。红点表征随机参数采样。由于随机采样服从固定的概率,它们倾向于经过一段时间后收敛于参数的高概率区域:蓝点表示当采样收敛之后,经过任意时间的随机采样。注意:垂直堆叠这些点仅仅是为了说明目的。收敛出现之后,MCMC 采样会得到作为后验分布样本的一系列点。用这些点画直方图,然后你可以计算任何感兴趣的统计特征:通过 MCMC 模拟生成的样本集合计算的任何统计特征,都是对真实后验分布的统计特征的最佳近似。MCMC 方法也可以用于评估多于一个参数的后验分布(例如,人类身高和体重)。对于 n 个参数,在 n 维空间中存在高概率的区域,其中特定的参数值集合可以更有效地解释数据。因此,我认为 MCMC 方法的本质,就是在一个概率空间中进行随机采样以近似后验分布。原文链接:https://towardsdatascience.com/a-zero-math-introduction-to-markov-chain-monte-carlo-methods-dcba889e0c50机器之心推出「Synced Machine Intelligence Awards」2017,希望通过四大奖项记录这一年人工智能的发展与进步,传递行业启示性价值。来自微信